Semmonen postaus. Video aiheesta joka on aika monimutkainen, itsellä vaati useamman läpikuuntelun että avautu oikein, ja graafi ilman mitään selityksiä. Seurauksena 10+ kpl paskapostauksia, joista näkee että kukaan postaajista ei oo kattonu tätä sun linkkaamaa videota.

Ylläpitäjä-toimittajalta melko hyvä postaus, etten sanoisi

Ihankun ois just jossain toisaalla tällä foorumilla vängätty aika paljon pelkkien linkkien, kuvien tai videoiden postaamisesta ja niiden informaatio arvosta

Noh kaatunutta maitoa, suremista jne. Jos joku aiemmin kommentoineista kuten lepakkomäyrät, jiipeet ja muuta vakionaamarit ois itseasiassa kattonu ton videon niin ois voinu huomata että;

Katoin kanssa ton videon aamulla. Ja nyt uudestaan pari kertaa. Jos kattoo ton videon ja kuuntelee & ymmärtää mitä battlenonsense siinä kertoo, niin noin 12:00 minuutin kohdalla alkaa aihepiirin käsittely nimeltä "tämähän on buginen läjä paskaa" jos noin niinkö luova kielenkäyttö sallitaan.

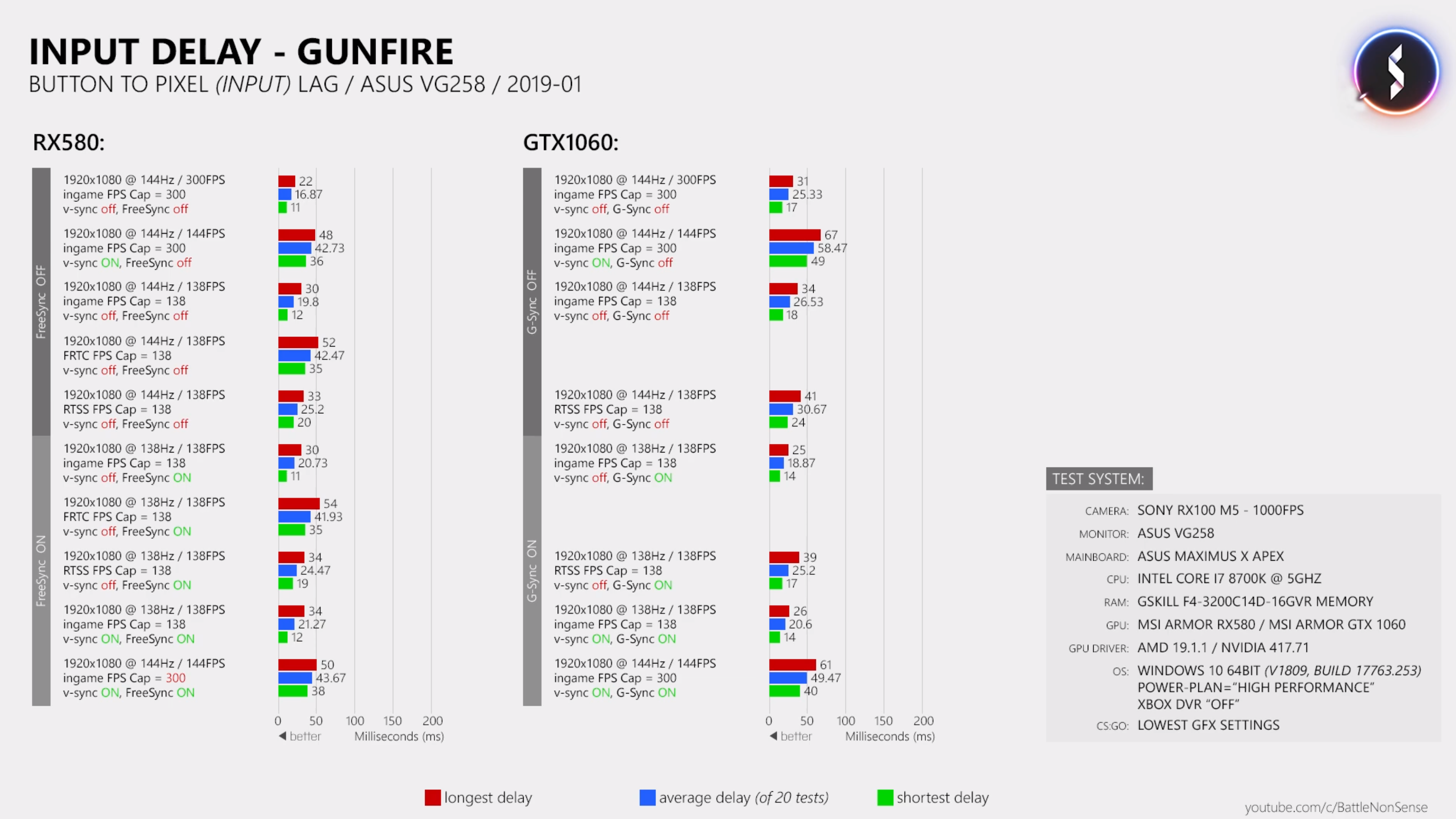

Videohan kulkee kuten mikä tahansa dekkaritarina konsanaan. Alkuun lätistään paskaa, sitten ruetaan testaamaan miten monitorin viiveet käyttäytyy AMD vs. Nvidia ja Freesync vs. Gsync (adaptive sync). Ensi alkuun menee hyvin, ajelee AMD:llä tuloksia eikä ole mitään bugeja eikä mitään, pelkkää testien ajamista ja tulosten tyrkkäämistä graafiin.

Sitten alkaa monitorin testaus nVidian grafiikka kortilla. Ekat ajot ilman gsynkkiä menee hyvin. Mutta sitten kohtaa mystisen homman; nVidialla synkit: OFF ja viiveet on suuremmat mitä AMD:llä. Alkaa ihmetellä että nyt on kyllä outoa paskaa, viiveiden pitäis olla ilman synkkejä molemmilla näyttiksillä samat ja mahdollisten erojen olettaisi olevan freesync-vs.-gsync vertailussa.

Ja sit kompastutaan vähän bugiin kun ruetaan ajamaan gsync-päällä testejä. Battlenonsense kertoo että näytön oikea puoli alkoi sammumaan. Lähetteli siitä bugiraporttia nVidialle, nVidia vastasi että "hyvä löytö, onnistuttiin toistamaan bugi meillä, korjataan seuraavissa ajureissa". Sai monitorin taas pelaamaan rämppäämällä virtoja päälle/pois, välillä ongelman uusiessa.

Powerin rämppäämisen jälkeen aloitti gsync-testit. Ajeli gsync-on (eli adaptive) eikä havainnut että viiveet olisi merkittävästi AMD:n RX580:aa korkeampia freesync-päällä, tulosten ollessa virhemarginaalissa toisistaan.

En kyllä ihan hirveesti lähtis tästä vielä paukuttamaan henkseleitä mihinkään suuntaan. Aika moni edellä videota kommentoineista vaikuttaa olevan siinä uskossa, että battlenonsense ois nyt todistanu että freesynkillä on pienemmät viiveet kuin gsynkillä adaptive-synkkiä ajellessa. Ei ole, eikä Battlenonsense sano näin missään kohtaa videota.

12:00 minuutista eteenpäin. Todistaa lähinnä että nVidian freesynk-tuki gsynk-ajureissa on keskeneräinen, mikä on ehkä odotettavissa kun tämä on eka ajuri missä tuki on ylipäätänsä olemassa. Voitaneen olla siis aika varmoja että tuki paranee tulevaisuudessa.

Erityisesti tämä kohta:

"I then decided to continue with my tests, expecting that I would still continue to measure input-lags that are higher then what I measured when it was connected to the AMD graphics card. But with g-sync now active I measured delays that are very close to those on the freesync test."

"So this got me to the conclusion that when you do not enable gsync on this gsync (freesync) compatible monitor, then you get more input lag then when you connect it to a graphics card from AMD. I've also told nvidia about this, but I have not heard back from them yet".

Eli tässä on se homman pihvi:

Asus VG258 toimii nVidian näytönohjaimella isommilla viiveillä mitä AMD:n näytönohjaimella, kun kaikki synkit on poissa päältä.

Synkit päällä molemmilla about yhtä vikkelästi, ja nVidialla synkit (gsync) päällä vikkelämmin mitä ilman synkkiä.

Lisäksi; graafeista voi päätellä että nVidialla V-sync lisää lagia enemmän mitä AMD:llä, kun katsoo noita palkkeja missä V-sync on: enabled.

"After I spend some time with the VG258 I can say that playing on this monitor with active gsync (adaptive/freesync) feels just as good as playing with freesync." Ja sitten kertoo miten voi käyttää tota freesync-monitoria yhdessä gsync-moduulin sisältävän monitorin kanssa surroundissa kun ajaa molempia g-synkillä.

Summa-summarum:

Voisitte vaikka katsoa sen linkatun lähdemateriaalin ennenkuin rupeatte jauhamaan puolta sivua paskaa vääristä lähtökohdista ja omituisista olettamista