It has become a common practice for several years to report instant (discrete) clock values for CPUs. This method is based on knowledge of the actual bus clock (BCLK) and sampling of core ratios at specific time points. The resulting clock is then a simple result of ratio * BCLK. Such approach worked quite well in the past, but is not longer sufficient. Over the years CPUs have become very dynamic components that can change their operating parameters hundreds of times per second depending on several factors including workload amount, temperature limits, thermal/VR current and power limits, turbo ratios, dynamic TDPs, etc. While this method still represents actual clock values and ratios reported match defined P-States, it has become insufficient to provide a good overview of CPU dynamics especially when parameters are fluctuating with a much higher frequency than any software is able to capture. Another disadvantage is that cores in modern CPUs that have no workload are being suspended (lower C-States). In such case when software attempts to poll their status, it will wake them up briefly and thus the clock obtained doesn't respect the sleeping state.

Hence a new approach needs to be used called the Effective clock. This method relies on hardware's capability to sample the actual clock state (all its levels) across a certain interval, including sleeping (halted) states. The software then queries the counter over a specific polling period, which provides the average value of all clock states that occurred in the given interval. HWiNFO v6.13-3955 Beta introduces reporting of this clock.

Many users might be surprised how different this clock is in comparison to the traditional clock values reported. But please note that this effective value is the average clock across the polling interval used in HWiNFO.

This new method has been tested on several CPUs and has shown to provide more accurate results especially in scenarios with extremely fluctuating values.

For example on Cascade Lake-X running a 1C workload, the effective clock provides values closer to specified 1C Turbo ratio limit, while (due to heavy fluctuations enforced by power limits) the discrete method only occasionally is able to sample the highest ratio.

On Zen2 (Matisse) systems this method can provide results closer to Ryzen Master (RM) per-core clock values, especially because it respects sleeping cores. It is assumed that such cores are marked as sleeping by RM when the effective (average) clock is below a certain threshold (somewhere around 50 MHz and below). Please note, that RM uses a different (proprietary) technique to measure clocks, so there might be some differences between the effective clock in HWiNFO and RM. While we work with AMD on the best way to access more accurate data to measure clock and voltage values, this remains the only method. Additionally, the current effective clock method is an architectural feature meaning that it doesn't depend on a certain CPU model, but is rather universal across a broad range of CPU families.

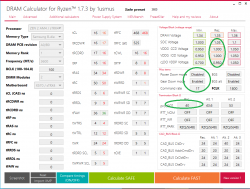

saisi alkaa katselee vähän ram oc ja f clock hommia