Kapasitanssi ei kuluta sähköä.

Nyt ei oikein nähdä metsää puilta.

Kondensaattori säilöö sähköä, ja sen sähkön varaaminen ja purkaminen sinne kondensaattoriin tarkoittaa tehonkulutusta.

Piirin sisällä oleva sähkövaraus on suoraan verrannollinen piirin kapasitanssista ja jännitteestä.

Piirin sisällä olevaan sähkövaraukseen sitoutunut energia on suoraan verrannollinen piirin kapasitanssista ja neliöllisesti verrannollinen jännitteen neliöstä.

Piirin dynaaminen sähköteho tulee hyvin pitkälti siitä, kuinka monta kertaa tämä energia pitää aikayksikköä kohden purkaa ja uudelleen ladata.

Sähkönkulutuksen täytyy aiheutua metallijohtimien ja kapasitanssia ohjaavien transistorien häviöistä. Kun mennään pienempiin valmistusprosesseihin, metallijohtimille jää yhä vähemmän tilaa eli ne joudutaan tekemään ohuemmiksi, jolloin niiden resistanssi kasvaa. Kun samalla pienempi transistori kuitenkin kuluttaa hieman vähemmän, metallijohtimien osuus dynaamisesta sähkönkulutuksesta tulee suuremmaksi.

Sen transistorin ja niiden välillä olevien johtojen kapasitanssi myös pienenee valmistustekniikan pienentyessä.

Metallijohtimien resistanssi kasvaa lineaarisesti neljänneksen huoneenlämmöstä 95 asteeseen. Ja kun resistanssi kasvaa lämpenemisen myötä, se edelleen lämmittää lisää jne.

Sen resistanssin vaikutus on lähinnä se, että se sähkövaraus latautuu sinne signaaliin hitaammin, kun signaali nousee tilasta 0 tilaan 1, tai kun se purkautuu sieltä pois kun signaali laskee tilasta 1 tilaan 0.

Käsittääkseni vuotovirtojen osuus piirin sähkönkulutuksesta tulee koko ajan suuremmaksi, kun mennään pienempiin valmistusprosesseihin.

Käsityksesi on virheellinen, koska uusien valmistustekniikoiden myötä on otettu käyttöön tekniikoita, jotka dramaattisesti auttavat vuotovirtaan.

Vuotovirrat oli suurimmillaan jollain TSMCn ja GFn niinsanotulla "20nm" prosessilla(todellinen johtoväli 64nm). Sitten sen jälkeen otettiin käyttöön FinFETit jotka pudottivat vuotovirtoja dramaattisesti. Intel taas otti FinFETit käyttöön jo P1270-prosessissaan (jota markkinamiehet kutsuu feikkinanometriluvulla 22).

Ja kaikilla valmistustekniikoilla voidaan aina valmistaa erilaisia transistoreita - eniten vuotavat ULVT(Ultra Low Voltage Threshold)-solut, jotka ovat nopeimpia, mutta niitä ei ole pakko käyttää. Toki niitä halutaan käyttää sellaisissa paikoissa, jotka ovat nopeuden kannalta kriittisiä, mutta niiden osuus koko piiristä voi olla hyvin pieni, suurin osa piiristä voi käyttää vähemmän vuotavia transistoreita.

Lämpötilan kasvu lisää vuotovirtoja, mikä kasvattaa staattista sähkönkulutusta, mikä puolestaan kasvattaa lämpötilaa.

Staattisen virrankulutuksen osuus virrankulutuksesta on jossain CPUn monen säikeen maksimikulutuksessa (josta eniten tunnut valittavan) todella pientä.

Et oikein tunnu hokaavan tätä "takaisinkytkentää", mikä korkeammilla lämpötiloilla itsessään on. Eikä se koske vain prossupiiriä, ihan koko prossupaketissa sähkönkulutus kasvaa korkeampien lämpötilojen seurauksena, mikä edelleen lisää lämpenemistä jne.

Hoksaan sen oikein hyvin. Sinä sen sijaan et tunnu ymmärtävän kokonaiskuvaa ja kuvittelet ymmärtäväsi näistä asioista enemmän kuin ihmiset joille piirien suunnittelu on ammatti.

Niin, kun siirtymässä ns. 7 nm valmistusprosessista ns. 5 nm valmistusprosessiin

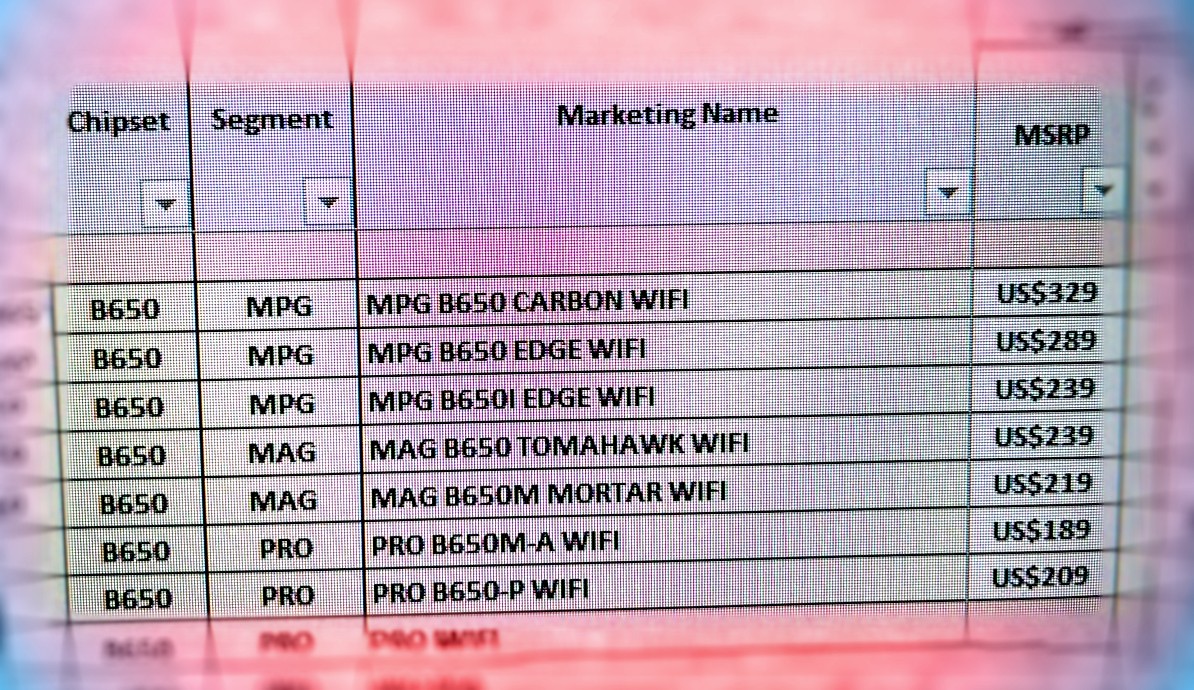

Ei ole mitään todellista 7nm tai 5nm prosessia. On N7-prosessi jolla pienin johtoväli on 40nm ja N5-prosessi jolla pienin johtoväli on jotain n. 30-32nm luokkaa.

transistoritiheys kasvaa enemmän kuin yksittäisen transistorin sähkönkulutus pienenee, tarkoittaa se sähkönkulutuksen kasvamista pinta-alayksikköä kohti. Tällöin tietenkin itse mikroarkkitehtuuri tulisi suunnitella energiatehokkaammaksi.

Ei, vaan tällöin prosessorin luonnollinen toimintalämpötila kasvaa, mutta mitään ei tarvi suunnitella uusiksi. Suuri sähkönkulutus pinta-alaa kohden ja siitä seuraava pieni maksimilämpötilojen nousu ei ole mikään suuri ongelma.

Jollei parempaan pystytä, kellotaajuuksia tulisi laskea. Nythän on tehty päinvastoin, kellotaajuuksia on jopa nostettu.

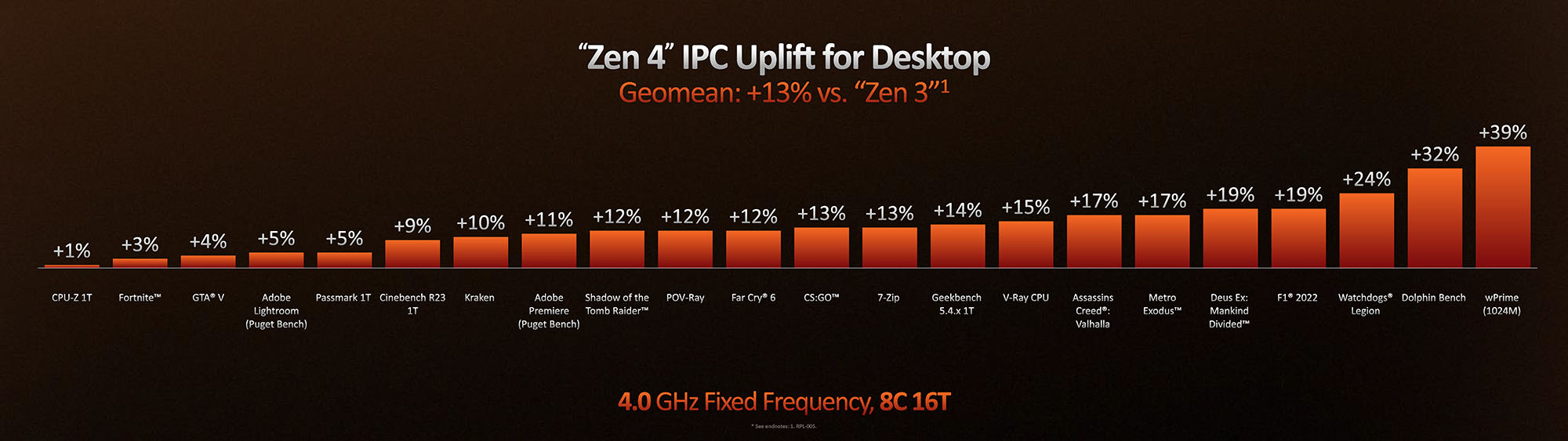

Kellotaajuuksia voidaan nostaa, koska

1) uusi valmistustekniikka pystyy toimimaan nopeammin.

2) uusi valmistustekniikka on energiatehokkaampi kuin vanha, samalla sähkönkulutuksella voidaan piiriä ajaa suuremmalla kellotaajuudella.

Suorituskyky paranee, mutta pellepelottomat jotka tuijottaa vaan lämpömittarisoftan lukemaa ja pelkää suuria lukuja valittaa.

Siinä, että suorituskykyä täysin turhaan heikennettääisiin vain että suuria lukuja pelkäävät harrastelijat saisivat vähemmän pelättävää ei ole mitään järkeä.

Näkisin asian niin päin, että nyt korkeilla lämpötiloilla saavutetaan kovalla hinnalla pieni määrä useimmille käyttäjille turhaa monen säikeen suorituskykylisää.

Se, että piirin jotkut osat käy kuumempana ja sen näkee vain siitä, että lämpötilamittarisofta näyttää suurempia lukuja ei ole mikään "kova hinta". Päin vastoin, se on hyvin halpa hinta.

Ja sillä, että piiriä käytetään suurehkolla jännitteellä ei ole

mitään tekemistä monen säikeen suorituskyvyn kanssa. Siinä on kyse täysin siitä, että tavoitellaan suuria maksimikelloja eli

yhden säikeen suorituskykyä

Oletin, että tämä aiempi viesti

olisi pitänyt paikkansa, että jännite asetetaan niin, että prossu toimii vakaasti 95 asteessa kaikkien ytimien rasituksessa, ja on silloin korkeimmillaan. Emolevyjen tehoratkaisu täytyy kuitenkin mitoittaa tämän käyttötilanteen mukaan. Ei sitä jännitettä yhden ytimen kuormituksessa alemmassa lämpötilassa tarvitsisikaan laskea.

Se, mikä jännite tarvitaan riippuu täysin siitä, mitä kellotaajuutta tavoitellaan.

Jännitettä tarvitaan paljon siihen, että saavutetaan korkea

maksimikello eli yhden säikeen suorituskyky.

Että sotket nyt ihan täysin

1) yhden säikeen ja monen säikeen suorituskyvyn

2) Lämpötilarajan (eli sen, koska piiri laitetaan throttlaamaan lämpöjen takia) ja jännitteen.