@hkultala tai joku muu. Kuinka todennäköisenä pidät L4 cachen paluuta prosessoreihin erillisenä chiplettinä. Tuntuu että noi DDR5:n korkeat latenssit vaikeuttaa kovasti lisääntyneen yhdensäikeen suorituskyvyn todellista siirtymistä suorituskykyyn varsinkin peleissä. Jos L3 määrien lisääminen suoraan ytimiin on vaikeata ja kallista. Olisiko joku 20ns viiveellä oleva L4 hyödyllinen (verrattatuna DDR5 ~60ns) järkevissä määrin?

Samalla valmistustekniikalla se L4 ei olisi yhtään halvempaa kuin L3, ihan samaa SRAMia ne on nykyaikana molemmat.

Joskus n. 8v sitten Intelillä ja IBMllä oli eDRAM- pohjaisia uloimman tason välimuisteja joissain piireissään (crystall well, centaur) mutta eDRAM ei käytännössä toimi moderneilla valmistustekniikoilla.

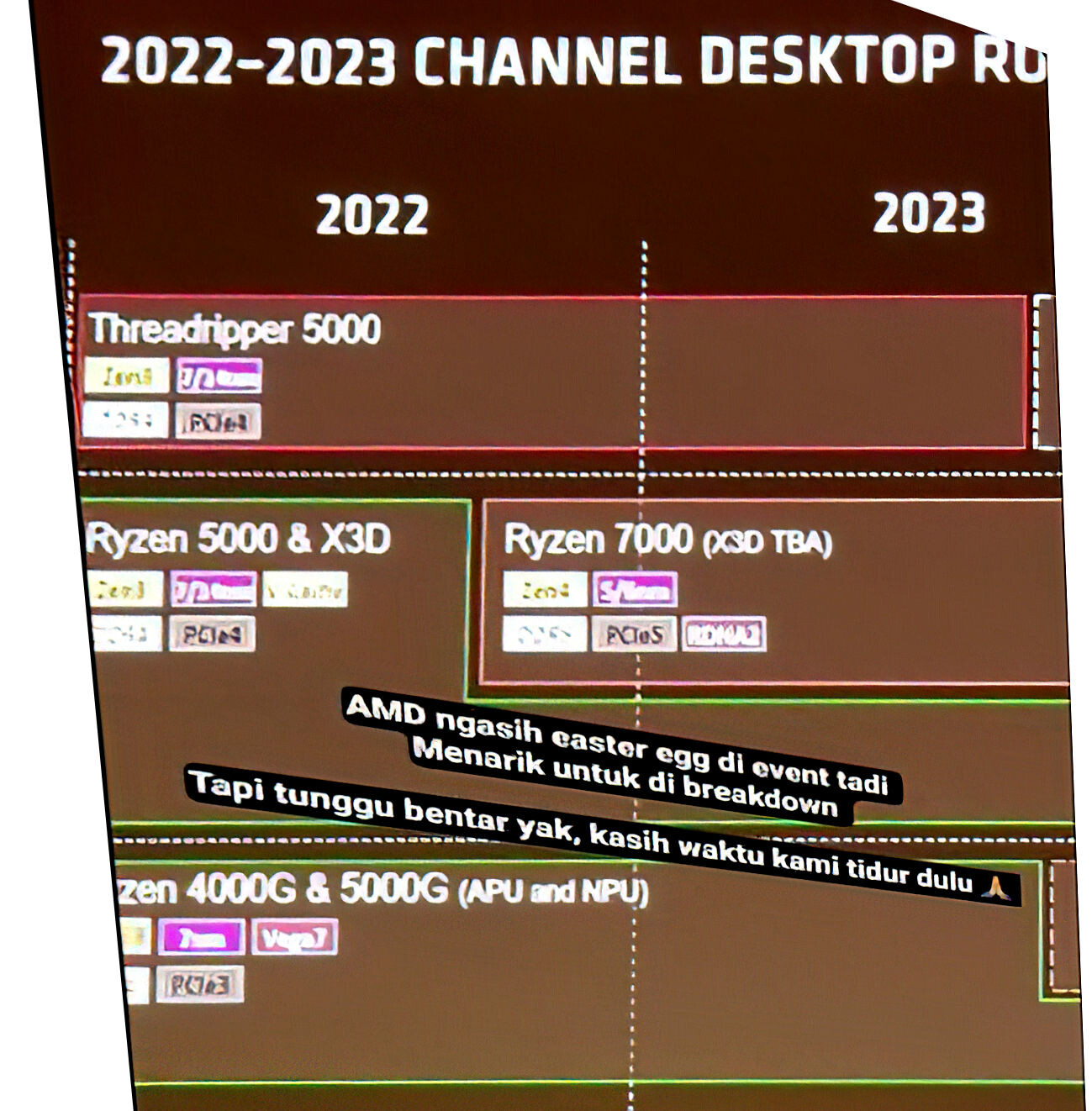

L4-kakussa CPUlla olisi järkeä lähinnä siinä tilanteessa, että prossupiilastu menee jollekin N3-valmistustekniikalle jolla SRAM on kapasiteettiinsa nähden entistä kalliimpaa, mutta L4-piilastu valmistettaisiin jollain N6lla jolla SRAM on halvimmillaan.

Ja samalla sen välimuistipiilastun voisi yhdistää IO-piilastulle, ei tarvi olla erikseen jos IO-piilastu tehdään N6lla.

Ja huhujen mukaanhan AMD on RDNA3-näyttiksissään tekemässä juuri näin, tosin niissä noita muistiohjain-/IO-/L3-piilastuja on kai useampi, eri muistikanaville omansa.

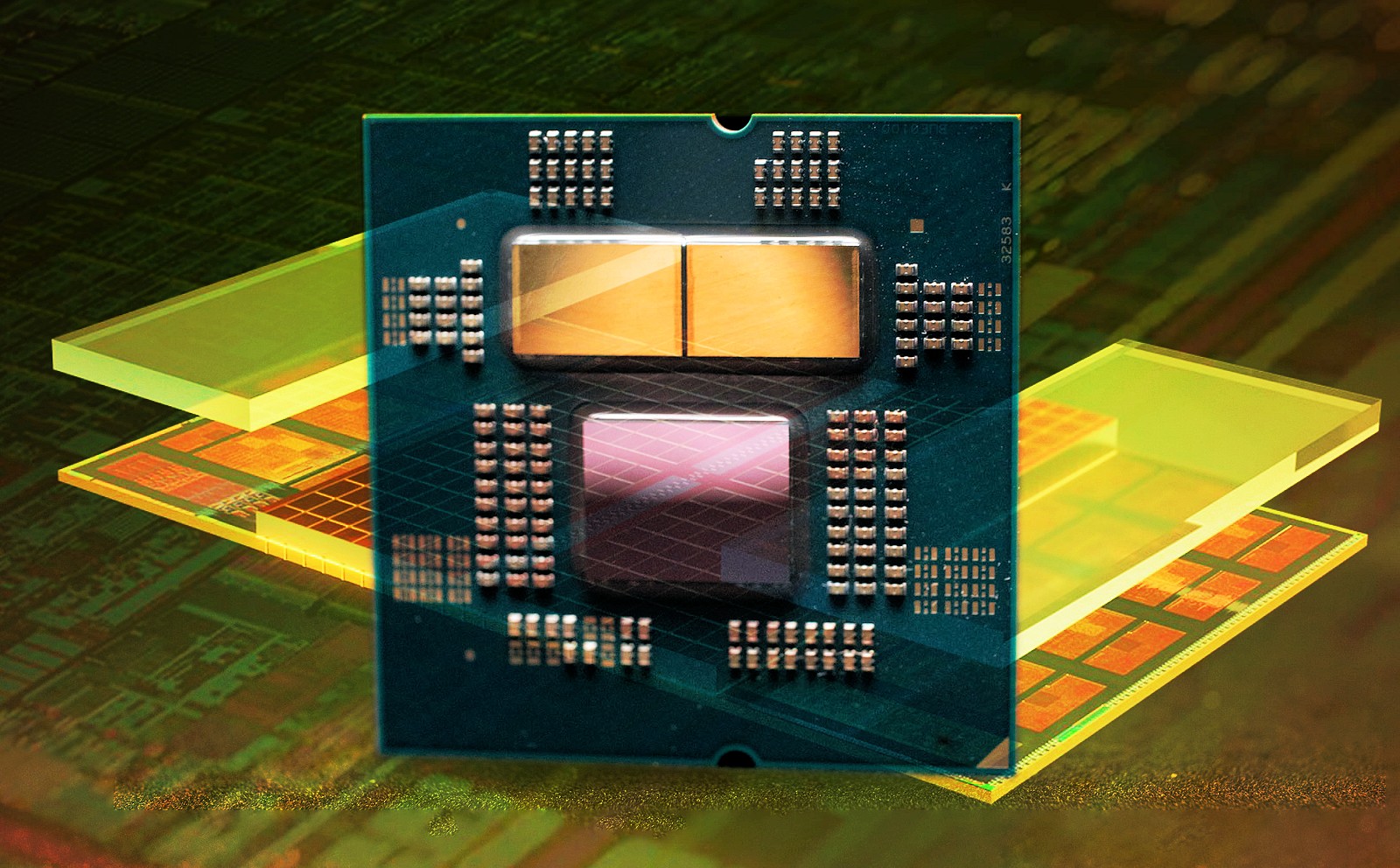

Mutta se, että AMD prossuihinsa integroi suurempia L3-kakkuja vertikaalisella stackäyksellä(v-cache) taas sotii tätä vastaan, tuo IO-piirille tuleva tai erillään oleva L4 olisi vähän vaihtoehto vcachelle mutta molemmissa yhtä aikaa ei oikein ole CPU-käytössä järkeä.

Toisaalta, APUun se L4-kakku voisi sopia hyvin että myös näyttis hyötyisi siitä, koska APUt ovat taas pahasti muistikaistapullonkaulaisia, ja Zen-johdannaisten CPUiden L3 ei ole näyttispuolen käytettävissä (eikä sitä pysty järkevästi modaamaan siten että se olisi näyttispuolen käytettävissä) mutta memory side cachenä toteutettu L4-kakku olisi myös näyttispuolen käytettävissä.

Intelin arkkitehtuuri L3-välimuistin suhteen taas on sen verran erilainen että Intelin L3-saattaa olla jo näyttispuolen käytettävissä tai sen modaaminen siten että se olisi näyttispuolen käytettävissä olisi verrattain helppoa. Joten Intelin integroidut näyttikset eivät samalla tavalla hyötyisi L4-kakusta, Intelille voisi riittää vaan sen L3-kakun kasvattaminen integroidun näyttiksen kaistapullonkaulan helpottamiseen.