Käytetty 3080Ti menee tuohon budjettiin.Sitten vain suosituksia pöytään mitä maksimissaan 700€ Nvidiaa kannattaa ostaa AI työkalujen opiskeluun ja pelaamiseen 1440p resoluutiolla nyt...

-

PikanavigaatioAjankohtaista io-tech.fi uutiset Uutisia lyhyesti Muu uutiskeskustelu io-tech.fi artikkelit io-techin Youtube-videot Palaute, tiedotukset ja arvonnat

Tietotekniikka Prosessorit, ylikellotus, emolevyt ja muistit Näytönohjaimet Tallennus Kotelot ja virtalähteet Jäähdytys Konepaketit Kannettavat tietokoneet Buildit, setupit, kotelomodifikaatiot & DIY Oheislaitteet ja muut PC-komponentit

Tekniikkakeskustelut Ongelmat Yleinen rautakeskustelu Älypuhelimet, tabletit, älykellot ja muu mobiili Viihde-elektroniikka, audio ja kamerat Elektroniikka, rakentelu ja muut DIY-projektit Internet, tietoliikenne ja tietoturva Käyttäjien omat tuotetestit

Softakeskustelut Pelit, PC-pelaaminen ja pelikonsolit Ohjelmointi, pelikehitys ja muu sovelluskehitys Yleinen ohjelmistokeskustelu Testiohjelmat ja -tulokset

Muut keskustelut Autot ja liikenne Urheilu TV- & nettisarjat, elokuvat ja musiikki Ruoka & juoma Koti ja asuminen Yleistä keskustelua Politiikka ja yhteiskunta Hyvät tarjoukset Tekniikkatarjoukset Pelitarjoukset Ruoka- ja taloustarviketarjoukset Muut tarjoukset

Kauppa-alue

Navigation

Install the app

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Huomio: This feature may not be available in some browsers.

Lisää vaihtoehtoja

Tyylin valinta

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

AMD-spekulaatioketju (RDNA:n ja CDNA:n tulevat sukupolvet)

- Liittynyt

- 17.10.2016

- Viestejä

- 10 895

Melkein ostin RX 9070 XT:n, mutta en saanut julkaisuhintaan. Sen hinta ~700€ on aika lailla yläraja minulle. RX 9070 ei tarjoa rahoille tarpeeksi vastinetta.

Käytetty 3080Ti menee tuohon budjettiin.

Eli @mariopossu miltä kuulostaa? Siinä on nyt sitten vaihtoehtoja. Joko odotat 9070XT tai etsit jostain käytetyn 3080Ti kortin tuohon hintaan. Kumpi sinusta vaikuttaa paremmalta 1440p pelaamiseen ja AI työkalujen opiskeluun?

- Liittynyt

- 21.02.2017

- Viestejä

- 6 174

Niin menee myös RTX 3090, joka on tekoälyjuttuihin todella paljon parempi valinta koska 100% enemmän muistia. Ei missään nimessä kannata ostaa 3080 Ti:tä 3090:n sijaan jos haluaa yhtään puuhastella tekoälyn parissa.Käytetty 3080Ti menee tuohon budjettiin.

Enpä pikaisesti löytänyt yhtään 3090 alle 700€. Kyllä tuolla 3080:llakin aika pitkälle AI-opiskelussa pääsee. Mutta jos alle 700€ jostain 3090:n saa niin se sitten.Niin menee myös RTX 3090, joka on tekoälyjuttuihin todella paljon parempi valinta koska 100% enemmän muistia. Ei missään nimessä kannata ostaa 3080 Ti:tä 3090:n sijaan jos haluaa yhtään puuhastella tekoälyn parissa.

- Liittynyt

- 21.02.2017

- Viestejä

- 6 174

Tämän foorumin myyntiosiolla viimeisen kuukauden sisään myyty useita hintaan 700€ tai alle.Enpä pikaisesti löytänyt yhtään 3090 alle 700€. Kyllä tuolla 3080:llakin aika pitkälle AI-opiskelussa pääsee. Mutta jos alle 700€ jostain 3090:n saa niin se sitten.

- Liittynyt

- 25.12.2016

- Viestejä

- 35

Minulle riittää kevyempi kortti myös, kunhan muistia on tarpeeksi. En osta käytettyä ja haluan AMD:n.

Tänne tulin kyselemään, että jos on RX 9060 XT ja RX 9060 tulossa milloin ja mihin hintaan? Opiskelijabudjetilla olen liikkeellä, niin ei kannata ehdotella 700€ kortteja. Paitsi jos niitä julkaisuhintaisia näkyy

Pärjään kannettavallani siihen asti, kunnes saan tuon näytönohjaimen.

Tänne tulin kyselemään, että jos on RX 9060 XT ja RX 9060 tulossa milloin ja mihin hintaan? Opiskelijabudjetilla olen liikkeellä, niin ei kannata ehdotella 700€ kortteja. Paitsi jos niitä julkaisuhintaisia näkyy

Pärjään kannettavallani siihen asti, kunnes saan tuon näytönohjaimen.

- Liittynyt

- 02.09.2021

- Viestejä

- 14

Q2 taitaa olla mitä AMD on kertonut julkaisusta ulos ja jostain näin veikkauksena huhtikuun. Hinnasta ei varmaan uskalla sanoa edes AMD vielä mitään, mutta käytännössä uskoisin saman tapahtuvan, kuin nyt eli odottavat mitä Nvidia tekee 5060 ti/5060 sarjan hinnottelun kanssa ja sitten asettavat MSRP:n sen mukaan. NVidian kortit taitavat tulla kanssa huhtikuussa ulos.Minulle riittää kevyempi kortti myös, kunhan muistia on tarpeeksi. En osta käytettyä ja haluan AMD:n.

Tänne tulin kyselemään, että jos on RX 9060 XT ja RX 9060 tulossa milloin ja mihin hintaan? Opiskelijabudjetilla olen liikkeellä, niin ei kannata ehdotella 700€ kortteja. Paitsi jos niitä julkaisuhintaisia näkyy

Pärjään kannettavallani siihen asti, kunnes saan tuon näytönohjaimen.

Viimeksi muokattu:

- Liittynyt

- 28.12.2021

- Viestejä

- 426

Taitaa olla turha odotella isompia piirejä. Jonkun johtajan suulla ihan vasta totesivat uudelleen, että keskittyvät nyt näihin kortteihin joita myydään eniten. Katsotaan seuraavassa sukupolvessa.

madi

Tukijäsen

- Liittynyt

- 19.07.2017

- Viestejä

- 4 576

Nykäshän ne aikoinaan Radeon VII:n melkeen hatusta niin aina voi toivoaTaitaa olla turha odotella isompia piirejä. Jonkun johtajan suulla ihan vasta totesivat uudelleen, että keskittyvät nyt näihin kortteihin joita myydään eniten. Katsotaan seuraavassa sukupolvessa.

- Liittynyt

- 12.12.2016

- Viestejä

- 4 995

Nykäshän ne aikoinaan Radeon VII:n melkeen hatusta niin aina voi toivoa

Jos on olemassa iso RDNA 4 piiri datacenterpuolelle niin sitten on mahdollista helposti. Muuten ei. Ei taida olla?

Radeon VII oli käytännössä vaan työpöydälle rebrändätty instinct MI60 (tjsp) kortti

- Liittynyt

- 22.10.2016

- Viestejä

- 12 914

Nykäshän ne aikoinaan Radeon VII:n melkeen hatusta niin aina voi toivoa

Ei todellakaan nykäisty "melkein hatusta" vaan

1) ensinnäkin se piiri oli jo kehitetty palvelinkäyttöön rinnakkaislaskentaan, oli pikkujuttu alkaa myymään sitä jo kehitettyä piiriä myös kuluttajamarkkinoille.

2) melko samanlainen piiri (vega 10) oli jo tehty vanhemmalla valmistustekniikalla, oli kohtalaisen pieni vaiva tehdä muutamia pikkuparannuksia, tuplata muistiohjaimet ja vaihtaa valmistustekniikka pienempään.

Ja piirien kehitys kestää monta vuotta, vaikka kaikki palikatkin olisi kasassa, käytännössä tapeout (fyysisen designin valmistuminen) pitää tapahtua selvästi yli vuosi ennen piirien markkinoilletuloa, ja sitä fyysistä designia tehdessä menee pelkästään sen lopulliseen laskemiseen kuukausia. (ja tätä ennen sen designin pitää siis olla jo käytännössä valmis)

Nyt AMDllä ei ole ollut mitään suurempaa RDNA4-piiriä kehitetteillä, joten jos sellaista nyt alettaisiin kehittämään, pikaprojektinakin (jossa ei kehitetä mitään uutta vaan vaan yhdisteltäisiin vanhat palikat eri tavalla) tapeout olisi aikaisintaan ihan loppuvuodesta ja piirit markkinoilla käytännössä vasta joskus talvella 2026-2027.

Eli seuraava iso piiri tulee sitten UDNA-arkkitehtuurilla.

Oma veikkaukseni UDNAsta on, että se ei tule olemaan täysin uusi arkkitehtuuri kuten RDNA oli, vaan että se tulee olemaan vaan RDNAn jatkokehitelmää jossa lähinnä 64-bittisten liukulukujen laskentaa nopeutettu huomattavasti(koska sitä tarvitaan tieteellisessä laskennassa) ja ehkä matalan tarkkuuden laskentaa myös (koska sitä tarvitaan tekoälypuolella). Ja sitten tietysti läjä pikkuparannuksia jotka olisi tullut RDNA5een ilman mitään linjastojen yhdistämistä. Ja voi olla, että nopea 64-bittisten liukulukujen tuki tulee olemaan optionaalinen ominaisuus, joka puuttuu halvemmista piireistä.

Mutta koska GCN-pohjaisesta CDNA:sta luovutaan ja RDNA-arkkitehtuurilinja ottaa myös sen roolin, se pitää brändätä uusiksi (Kuten CDNAkin brändättiin uusiksi vaikka se oli vain vanhan GCN:n jatkokehitelmää enemmän optimoituna tieteellisen laskennan ja tekoälyn tarpeiden suuntaan)

Ja miksi tähän linjastojen ensin erottamiseen ja nyt taas yhdistämiseen sitten päädyttiin: Koska alunperin RDNA:ta kehittäessä tilanne näytti siltä, että tekoälykiihdyttimet ja näyttikset kannattaa tehdä eri piireinä, koska näyttikseltä ei tarvita paljoa tekoälyvääntöä, mutta nyt tilanne on mennyt siihen että näyttiksen tuottamaa kuvaa skaalataan ja sen sekaan lisäillään keinotekoisia frameja tekoälyllä, jolloin myös näyttikseltä tarvitaan paljon tekoälyvääntöä.

- Liittynyt

- 17.10.2016

- Viestejä

- 1 147

Radeon VII ei myöskään saanut edes ostettua juuri mistään.

- Liittynyt

- 20.10.2016

- Viestejä

- 3 620

Se oli nääs edellä aikaansaRadeon VII ei myöskään saanut edes ostettua juuri mistään.

- Liittynyt

- 22.10.2016

- Viestejä

- 12 914

Laitan tähän säikeeseen, vaikka onkin nykysukupolvesta kyse:

Chips and Cheese tehnyt artikkelin RDNA4n säteenjäljitysparannuksista

chipsandcheese.com

chipsandcheese.com

Näköjään tuettuna onkin sekä "vanha" radix4-BVH-puu että "uusi" radix8-BVH-puu siten että jos käytetään radix4-puuta, voidaan yhteen shader-ytimeen liitetyllä säteenjäljitysyksiköllä laskea törmäystarkastusta kahden laatikon alilaatikoihin (2*4=8kpl) rinnakkain, mutta jos käytössä on "uusi" radix-8-puu, sitten lasketaan törmäystarkastusta yhden laatikon kaikkiin kahdeksaan alilaatikoihin rinnakkain.

Yleensä tuo radix8-moodi on nopeampi, koska muistiaccessit BVH-puuhun (joka on jossain välimuisteissa) tyypillisesti dominoi säteenjäljityksen suorituskykyä ja tuo radix8-puu minimoi muistiaccessien määrän, mutta jos olisi joku erikoistilanne jossa esim. BVH-puu on niin pieni että se aina mahtuisi lähimmän tason välimuisteihin eikä muistiviive olisi pullonkaula, kannattaisi ehkä käyttää tuota 2x4-moodia jossa kokonaisuudessaan tarvittavien törmäystarkastusen määrä voi olla hiukan pienempi.

Näppärä ominaisuus RDNA4ssa on myös BVH-laatikoiden pyörittäminen. Jos scenessä on vinoja asioita, voidaan niiden ympärille laittaa vinossa olevia BVH-laatikoita, jolloin BVH-puun "osumatarkkuus" saadaan paljon paremmaksi ja tarvii tehdä vähemmän turhia törmäystarkastuksia.

Chips and Cheese tehnyt artikkelin RDNA4n säteenjäljitysparannuksista

RDNA 4’s Raytracing Improvements

Raytraced effects have gained increasing adoption in AAA titles, adding an extra graphics quality tier beyond traditional “ultra” settings.

Näköjään tuettuna onkin sekä "vanha" radix4-BVH-puu että "uusi" radix8-BVH-puu siten että jos käytetään radix4-puuta, voidaan yhteen shader-ytimeen liitetyllä säteenjäljitysyksiköllä laskea törmäystarkastusta kahden laatikon alilaatikoihin (2*4=8kpl) rinnakkain, mutta jos käytössä on "uusi" radix-8-puu, sitten lasketaan törmäystarkastusta yhden laatikon kaikkiin kahdeksaan alilaatikoihin rinnakkain.

Yleensä tuo radix8-moodi on nopeampi, koska muistiaccessit BVH-puuhun (joka on jossain välimuisteissa) tyypillisesti dominoi säteenjäljityksen suorituskykyä ja tuo radix8-puu minimoi muistiaccessien määrän, mutta jos olisi joku erikoistilanne jossa esim. BVH-puu on niin pieni että se aina mahtuisi lähimmän tason välimuisteihin eikä muistiviive olisi pullonkaula, kannattaisi ehkä käyttää tuota 2x4-moodia jossa kokonaisuudessaan tarvittavien törmäystarkastusen määrä voi olla hiukan pienempi.

Näppärä ominaisuus RDNA4ssa on myös BVH-laatikoiden pyörittäminen. Jos scenessä on vinoja asioita, voidaan niiden ympärille laittaa vinossa olevia BVH-laatikoita, jolloin BVH-puun "osumatarkkuus" saadaan paljon paremmaksi ja tarvii tehdä vähemmän turhia törmäystarkastuksia.

Viimeksi muokattu:

MLID huhuili että amd:lta löytyisi insinöörien testipenkistä tappiinsa viritetty 9070 XT N4X valmistus tekniikalla

256Bit GDDR7 16/24/32Gt

3.4-3.7 Ghz

15-45% nopeampi 4K resoluutiolla verrattuna 9070 XT

Itse olisin toivonut kuulevani jotain huhuja 80/90 luokan chiplet korteista.

256Bit GDDR7 16/24/32Gt

3.4-3.7 Ghz

15-45% nopeampi 4K resoluutiolla verrattuna 9070 XT

Itse olisin toivonut kuulevani jotain huhuja 80/90 luokan chiplet korteista.

totta. videolla oli aika niukasti tarkempia tietoja, mutta navi 48 sitäkin kutsuttiin.Mutta eihän tuo ole sama piiri, jos siinä on GDDR7-tuki?

- Liittynyt

- 22.10.2016

- Viestejä

- 12 914

MLID huhuili että amd:lta löytyisi insinöörien testipenkistä tappiinsa viritetty 9070 XT N4X valmistus tekniikalla

256Bit GDDR7 16/24/32Gt

3.4-3.7 Ghz

15-45% nopeampi 4K resoluutiolla verrattuna 9070 XT

Itse olisin toivonut kuulevani jotain huhuja 80/90 luokan chiplet korteista.

MLID on netin typerimpiä tietotekniikka-aiheisten misinformaatiohuhujen levittäjiä.

Kaikki lähdekritiikki puuttuu täysin ja pusketaan ulos kaikenlaista roskaa. Ja sitten kun ollaan väärässä kun ollan postattu täyttä tuubaa, sitä ei myönnetä vaan selitellään vaan ja keksitään väitteitä että firmojen suunnitelmien on täytynyt muuttua.

Että ei kannata uskoa mitään tuosta

finWeazel

Tukijäsen

- Liittynyt

- 15.12.2019

- Viestejä

- 14 115

Puhdasta ajan ja rahanhukkaa suunnitella+testata uusi piiri, tapeout, maskit yms. että saadaan gddr7 versio navi48:sta. Joko navi48:ssa on jo alunperin muistiohjain mikä pystyy gddr6 ja gddr7 tai gddr7 navi48:sta ei ole olemassa. Menee samaan kategoriaan kuin huhut navi3x respinneistä ja korjauksista joilla saadaan aikaiseksi massiiviset kellotaajuudet.

Viimeksi muokattu:

oon katsonut mlidin videoita jo vuosia ihan viihde mielessä. Ei auta enään pelastaa "misinformaatiohuhuilta"MLID on netin typerimpiä tietotekniikka-aiheisten misinformaatiohuhujen levittäjiä.

Kaikki lähdekritiikki puuttuu täysin ja pusketaan ulos kaikenlaista roskaa. Ja sitten kun ollaan väärässä kun ollan postattu täyttä tuubaa, sitä ei myönnetä vaan selitellään vaan ja keksitään väitteitä että firmojen suunnitelmien on täytynyt muuttua.

Että ei kannata uskoa mitään tuosta

- Liittynyt

- 07.09.2023

- Viestejä

- 182

Tuskin AMD:n pelinäytönohjaimia suosivat edes haluavat ns. Super Duper malleja 9070 xt:stä. Tarkoittaisi siis myös melko massiivista hintalappua kyseiselle tuotteelle. Rx 9070 xt nykymuodossaan ja ovh. hinnallaan(silloin harvoin kun sattuu olemaan ovh.) on oikein toimiva ja myyvä paketti nykymarkkinoilla. Ehkä sitten 11 000 sarjan tai 12 000 sarjan kanssa voisi taas kisata nopeus herruudesta ja siten myös hinta herruudesta. Mutta näkisin että hetken aikaa keskiluokan kortti strategia voisi toimia paremmin AMD:lle ja luultavasti pelialalle positiivisena yleisesti.

- Liittynyt

- 17.10.2016

- Viestejä

- 10 895

Tuskin AMD:n pelinäytönohjaimia suosivat edes haluavat ns. Super Duper malleja 9070 xt:stä. Tarkoittaisi siis myös melko massiivista hintalappua kyseiselle tuotteelle. Rx 9070 xt nykymuodossaan ja ovh. hinnallaan(silloin harvoin kun sattuu olemaan ovh.) on oikein toimiva ja myyvä paketti nykymarkkinoilla. Ehkä sitten 11 000 sarjan tai 12 000 sarjan kanssa voisi taas kisata nopeus herruudesta ja siten myös hinta herruudesta. Mutta näkisin että hetken aikaa keskiluokan kortti strategia voisi toimia paremmin AMD:lle ja luultavasti pelialalle positiivisena yleisesti.

Ehdottomasti tämä. Ehkä muutama on eriävää mieltä mutta ihan rehellisesti voin sanoa että en todellakaan ostaisi AMD:n 3500€ "tämä voittaa RTX 5090" korttia.

joo tuo clickbait "9080 XT" taitaa olla MLID märkä päiväuni.

vähän ihmetyttää miten amd:lla voisi olla tuollainen 14900ks tapainen halo tuote ilman 14900k olemassa oloa.

niin udna piti olla seuraava projekti joten kuullostaa kummalliselta tälläinen "navi 48?" virittely

vähän ihmetyttää miten amd:lla voisi olla tuollainen 14900ks tapainen halo tuote ilman 14900k olemassa oloa.

niin udna piti olla seuraava projekti joten kuullostaa kummalliselta tälläinen "navi 48?" virittely

finWeazel

Tukijäsen

- Liittynyt

- 15.12.2019

- Viestejä

- 14 115

Taitaa mennä 2026 syksyyn tai ehkä jopa 2027 alkuvuoteen rdna5/udna kaupanhyllyllä. Normisykli ja välissä isoin panostus ai-konesaliin. Jos ei olis ai-konesalia niin olisi voinut kuvitella all in panostuksella uuden highend pelipiirin 2025 loppupuolelle.joo tuo clickbait "9080 XT" taitaa olla MLID märkä päiväuni.

vähän ihmetyttää miten amd:lla voisi olla tuollainen 14900ks tapainen halo tuote ilman 14900k olemassa oloa.

niin udna piti olla seuraava projekti joten kuullostaa kummalliselta tälläinen "navi 48?" virittely

- Liittynyt

- 18.01.2023

- Viestejä

- 1 672

Tuollaisen ylihintaisen radeon kortin kohdeyleisö taitaa olla aika pieni jos hinta on sama mitä Nvidian 80 sarjalaisella(tai yli) mutta jäät paitsi käytännössä kaikesta joka tekee noista RTX hyvän valinnan työasema kortiksi. CUDAn ja hyvän video koodekkien puute taitaa olla ne isoimmat murheenkryynit. Toki kilpailu on hyvästä ja ei se kuluttajaa tarvitse kiinnostaa onko jonkun tuotteen markkinoille tuominen kannattavaa vai eikö. Varmasti löytyy joku niche kohdeyleisö joka valitsee mielummin radeonin kuin nvidian siihen omaan tarkoitukseensa.

Taitaa tosin olla MLID:in voimafantasioita ja clickbaittaamisia nämä huhuilut.

Taitaa tosin olla MLID:in voimafantasioita ja clickbaittaamisia nämä huhuilut.

bahis

Tukijäsen

- Liittynyt

- 06.03.2019

- Viestejä

- 4 130

Ihan turhaa ulinaa jos et ole edes sitä 5090 ostamassa. Jos oikeasti tulisi nopeampi ja kaikessa parempi kortti kuin 5090 niin kyllä sillä ostajia löytyisi.Ehdottomasti tämä. Ehkä muutama on eriävää mieltä mutta ihan rehellisesti voin sanoa että en todellakaan ostaisi AMD:n 3500€ "tämä voittaa RTX 5090" korttia.

Ja ei tämän "9080 XT:n" ollut tarkoituskaan kilpailla 5090:n kanssa vaan 5080 / 5080 Super. Piirin koko sama kuin 5080, muistit mahdollisesti samat kuin 5080 Super ja hinta varmaan olisi sitten hieman alle sen 5080:n...

bahis

Tukijäsen

- Liittynyt

- 06.03.2019

- Viestejä

- 4 130

MLID toistaa asioita joita kuulee eri yrityksissä töissä olevilta "vuotajilta". Välillä ne on ihan totta ja välillä keksittyä. Toisinaan myös omia päätelmiä tarinoi, mutta kyllä niistä videoissa myös mainitsee että on omia arveluita. Mutta totta kyllä että monesti ne vuodot ja päätelmät osuu harhaan...MLID on netin typerimpiä tietotekniikka-aiheisten misinformaatiohuhujen levittäjiä.

Kaikki lähdekritiikki puuttuu täysin ja pusketaan ulos kaikenlaista roskaa. Ja sitten kun ollaan väärässä kun ollan postattu täyttä tuubaa, sitä ei myönnetä vaan selitellään vaan ja keksitään väitteitä että firmojen suunnitelmien on täytynyt muuttua.

Että ei kannata uskoa mitään tuosta

Mutta sinä varmaan olet sen verran perillä valmistustekniikoista että osaat sanoa olisiko N4P FinFET prosessilla olevaa Navi48:a mahdollista järkevällä työmäärällä muokata valmistettavaksi N4X tai N3X prosessille?

Muistiohjaiman muutos GDDR6 -> GDDR7 saattaisi ehkä olla mahdollista jos olisi jo alunperin ollut suunnitelmat molemmille vaihtoehdoille...

- Liittynyt

- 14.10.2016

- Viestejä

- 25 092

Prosessin vaihto voi olla helppoakin jos suunnittelusäännöt on pysynyt samoina, eli ehkä N4P/X vaihto olisi verrattain triviaali. Se ei kuitenkaan taikoisi sinne mitään GDDR7-muistiohjaimia, se vaatisi täysin uuden piirin suunnittelun, ellei muistiohjain sitten ole valmiiksi niitä tukeva (mitä se tuskin kuitenkaan on, GDDR7 muuttaa signalointitavankin ihan toiseen)Mutta sinä varmaan olet sen verran perillä valmistustekniikoista että osaat sanoa olisiko N4P FinFET prosessilla olevaa Navi48:a mahdollista järkevällä työmäärällä muokata valmistettavaksi N4X tai N3X prosessille?

ps. vaikka vain NVIDIA markkinoi "omaa prosessiaan" niin kaikki isot asiakkaat kustomoivat TSMC:n prosesseja omiin tarpeisiinsa eikä yhden N4P ole sama kuin toisen N4P jne

- Liittynyt

- 17.10.2016

- Viestejä

- 10 895

Ihan turhaa ulinaa jos et ole edes sitä 5090 ostamassa.

Eli sinä haluat nyt laittaa kirjoihin että sinusta henkilö joka ei ole ostamassa jotain tiettyä tuotetta ja todennetusti sitä hanki ei saisi osallistua mihinkään sitä koskevaan keskusteluun? Jos siis joku henkilö täältä kirjoittaa jotain prosessoriin, näytönohjaimeen, emolevyihin, muisteihin tms. liittyvään ketjuun mutta ei omista / tule ostamaan kyseistä tuotetta se on sinusta vain "turhaa ulinaa"?

Seuraavaksi kannattaa varmaan siirtyä esim. 5060 ketjuun kertomaan tätä ilosanomaasi...

Otaksun siis että sinulla jo on tuo 5090 ja olit sitä kovasti vaihtamassa tuohon huhuttuun ja tulevaan AMD:n uuteen malliin.. ..koska muuten kaikki viestisi tässä ketjussa olisivat sinua lainaten "turhaa ulinaa" jos et moisia omista...

- Liittynyt

- 28.10.2016

- Viestejä

- 6 357

Ehkä pointti on siinä, että turha paukutella, että en ostais kolmentonnin näyttistä, jos ei oo ostamassa kolmentonnin näyttistä. On niille ostajia kuitenkin, eikä se fakta, että sinä et sitä osta, tee tuotetta turhaksi.Eli sinä haluat nyt laittaa kirjoihin että sinusta henkilö joka ei ole ostamassa jotain tiettyä tuotetta ja todennetusti sitä hanki ei saisi osallistua mihinkään sitä koskevaan keskusteluun? Jos siis joku henkilö täältä kirjoittaa jotain prosessoriin, näytönohjaimeen, emolevyihin, muisteihin tms. liittyvään ketjuun mutta ei omista / tule ostamaan kyseistä tuotetta se on sinusta vain "turhaa ulinaa"?

Seuraavaksi kannattaa varmaan siirtyä esim. 5060 ketjuun kertomaan tätä ilosanomaasi...

Otaksun siis että sinulla jo on tuo 5090 ja olit sitä kovasti vaihtamassa tuohon huhuttuun ja tulevaan AMD:n uuteen malliin.. ..koska muuten kaikki viestisi tässä ketjussa olisivat sinua lainaten "turhaa ulinaa" jos et moisia omista...

- Liittynyt

- 17.10.2016

- Viestejä

- 10 895

Ehkä pointti on siinä, että turha paukutella, että en ostais kolmentonnin näyttistä, jos ei oo ostamassa kolmentonnin näyttistä. On niille ostajia kuitenkin, eikä se fakta, että sinä et sitä osta, tee tuotetta turhaksi.

Toki muutamia henkilöitä löytyy, mutta se on kohtuullisen pieni määrä pelaajia. Sen näkee esim. Steamin tilastoja katsomalla. Tai ihan myyntilukuja jos niitä suostuvat paljastamaan. Eli paljonko maailmassa on myyty GTX 5090 korttia julkaisun jälkeen vs. esim. 7090XT korttia mikä on "vähemmän tunnettu" sekä noin yleisesti haluttu kilpailijan kortti. Uskallan väittää että silti siihen on "tyydytty" ihan hinnan takia.

Alunperin sanoinkin että muutamia eriäviä mielipiteitä voi löytyä mutta toki, kyllähän aina löytyy ostajia mitä kalleimmille esineille. En silti usko että tuollaisen tekeminen olisi AMD:lle järkevää mikä oli oma pointtini. Eli vaikka sanoinkin että en itse sitä tuotetta ostaisi en tunne kovin montaa muutakaan joka olisi valmis iskemään 3500€ AMD:n uutuus näytönohjaimeen kiinni.

EDIT: toki tällä foorumilla muutamia löytyy, mutta edelleen väitän että heidän määränsä on suhteessa kaikkeen muuhun Suomen väkilukuun pieni promillen murto-osa.

bahis

Tukijäsen

- Liittynyt

- 06.03.2019

- Viestejä

- 4 130

Eli sinä haluat nyt laittaa kirjoihin että sinusta henkilö joka ei ole ostamassa jotain tiettyä tuotetta ja todennetusti sitä hanki ei saisi osallistua mihinkään sitä koskevaan keskusteluun? Jos siis joku henkilö täältä kirjoittaa jotain prosessoriin, näytönohjaimeen, emolevyihin, muisteihin tms. liittyvään ketjuun mutta ei omista / tule ostamaan kyseistä tuotetta se on sinusta vain "turhaa ulinaa"?

Seuraavaksi kannattaa varmaan siirtyä esim. 5060 ketjuun kertomaan tätä ilosanomaasi...

Otaksun siis että sinulla jo on tuo 5090 ja olit sitä kovasti vaihtamassa tuohon huhuttuun ja tulevaan AMD:n uuteen malliin.. ..koska muuten kaikki viestisi tässä ketjussa olisivat sinua lainaten "turhaa ulinaa" jos et moisia omista...

Ei vaan tarkoitin sitä että se että joku sanoo ettei ostaisi AMD:n korttia vaikka se voittaisi 5090:n ei tuo mitään lisäarvoa keskusteluun jos kyseinen henkilö ei muutenkaan olisi ostamassa kyseisen hintaluokan korttia. Eli juurikin mitä @perato tuossa aiemmin jo mainitsi.

Itse ostaisin Gigabyten blokillisen 5090:n jos niitä saisi, mutta ainut kauppa missä niitä on ollut viimeisen 2kk aikana tilattavissa oli sellainen mistä en muista syistä tilausta tehnyt.

Jos AMD:ltä olisi tulossa 5080:aa nopeampi 32GB muistilla oleva blokillinen kortti niin ehdottomasti sellaisen ostaisin ennemmin kuin ylihintaisen 5090:n...

- Liittynyt

- 17.10.2016

- Viestejä

- 10 895

Ei vaan tarkoitin sitä että se että joku sanoo ettei ostaisi AMD:n korttia vaikka se voittaisi 5090:n ei tuo mitään lisäarvoa keskusteluun jos kyseinen henkilö ei muutenkaan olisi ostamassa kyseisen hintaluokan korttia.

Toisaalta onko tämä sama myös kääntäen? Eli jos minä tai vaikka Sampsa kritisoi 330€ uutta 5060 korttia huonoksi eri syiden (esim. 8Gt muistia) takia eikö mielipiteemme tuo mitään lisäarvoa keskusteluun (eli on "ihan turhaa ulinaa" poislukien arvostelut kuitenkin koska Sampsa esim. tekee niitä työkseen) koska emme kuitenkaan ostaisi niin halpaa korttia koneeseemme? Vai koskeeko tämä ainoastaan kalliimpia tuotteita ja missä menisi sitten raja? Jos minulla on aiemmin 5900X ja nyt 7900X saanko puhua myös vähemmän säikeitä omaavissa ketjuissa ja onko sitten 5950X ja 7950X prosessorien ketjut sellaisia että koska en kalliimpaa & useampi ytimistä prosessoria ole ostanut en ole jäävi niissä puhumaan? (Enkä ole ajatellut ostavani 16-ydin/32-säie prosessoria ihan hetkeen ja vasta äskettäin siirryin 64Gt muistimäärään)

Kääntäen siis esim. henkilö joka omistaa omakotitalon saa kommentoida kaikkia muita asumismuotoja mutta henkilö joka asuu vuokralla ei saa osallistua keskusteluun jotka koskevat mitään muita asumismuotoja jne.

bahis

Tukijäsen

- Liittynyt

- 06.03.2019

- Viestejä

- 4 130

Miten nyt et ymmärrä että kommenttisi siitä että SINÄ et ostaisi AMD:n 5090:aa nopeampaa korttia ei tuo mitään lisäarvoa keskusteluun, koska et ole sen hintaluokan korttia kuitenkaan ostamassa? Eli kommentillasi ei ollut mitään tekemistä spekuloidun AMD:n kortin kanssa ja siten ketjun aiheen kanssa...Toisaalta onko tämä sama myös kääntäen? Eli jos minä tai vaikka Sampsa kritisoi 330€ uutta 5060 korttia huonoksi eri syiden (esim. 8Gt muistia) takia eikö mielipiteemme tuo mitään lisäarvoa keskusteluun (eli on "ihan turhaa ulinaa" poislukien arvostelut kuitenkin koska Sampsa esim. tekee niitä työkseen) koska emme kuitenkaan ostaisi niin halpaa korttia koneeseemme? Vai koskeeko tämä ainoastaan kalliimpia tuotteita ja missä menisi sitten raja? Jos minulla on aiemmin 5900X ja nyt 7900X saanko puhua myös vähemmän säikeitä omaavissa ketjuissa ja onko sitten 5950X ja 7950X prosessorien ketjut sellaisia että koska en kalliimpaa & useampi ytimistä prosessoria ole ostanut en ole jäävi niissä puhumaan? (Enkä ole ajatellut ostavani 16-ydin/32-säie prosessoria ihan hetkeen ja vasta äskettäin siirryin 64Gt muistimäärään)

Kääntäen siis esim. henkilö joka omistaa omakotitalon saa kommentoida kaikkia muita asumismuotoja mutta henkilö joka asuu vuokralla ei saa osallistua keskusteluun jotka koskevat mitään muita asumismuotoja jne.

Saat toki kirjoittaa tässä ketjussa, mutta kommentti missä ei ole mitään muuta sisältöä kuin että SINÄ et ostaisi korttia ei tuo mitään lisäarvoa.

finWeazel

Tukijäsen

- Liittynyt

- 15.12.2019

- Viestejä

- 14 115

imho. niin kauan kuin on eri muistivaihtehtoja tarjolla niin asiat on a-ok. Kuluttajat valitsee itselleen sopivan tuotteen.

Viime kädessä argumentit kutistuu siihen. että pitäisi saada halvemmalla enemmän muistia ja enemmän fps:aa. Toisaalta pörssiyrityksen tehtävä on tehdä voittoa sijoittajille. Absoluuttinen yrityksen onnistuminen on mitataan osakkeen arvosta ja kvartaalituloksesta

Frank Azorin ja oletettavasti myös amd linja... ihan sama linja kuin nvidialla. 8GB riittää pelaajien enemmistölle.

www.tomshardware.com

www.tomshardware.com

Viime kädessä argumentit kutistuu siihen. että pitäisi saada halvemmalla enemmän muistia ja enemmän fps:aa. Toisaalta pörssiyrityksen tehtävä on tehdä voittoa sijoittajille. Absoluuttinen yrityksen onnistuminen on mitataan osakkeen arvosta ja kvartaalituloksesta

Frank Azorin ja oletettavasti myös amd linja... ihan sama linja kuin nvidialla. 8GB riittää pelaajien enemmistölle.

'[The] Majority of gamers are still playing at 1080p and have no use for more than 8GB of memory': AMD justifies RX 9060 XT's 8GB of VRAM

Do you buy an 8GB GPU to play at 1080p, or do you play at 1080p because you have an 8GB GPU?

Viimeksi muokattu:

- Liittynyt

- 22.10.2016

- Viestejä

- 12 914

MLID toistaa asioita joita kuulee eri yrityksissä töissä olevilta "vuotajilta". Välillä ne on ihan totta ja välillä keksittyä. Toisinaan myös omia päätelmiä tarinoi, mutta kyllä niistä videoissa myös mainitsee että on omia arveluita. Mutta totta kyllä että monesti ne vuodot ja päätelmät osuu harhaan...

Mutta sinä varmaan olet sen verran perillä valmistustekniikoista että osaat sanoa olisiko N4P FinFET prosessilla olevaa Navi48:a mahdollista järkevällä työmäärällä muokata valmistettavaksi N4X tai N3X prosessille?

N4P => N4X onnistuu hyvin helpolla, ei tarvi tehdä edes uutta leiskaa. Mutta sillä ei saada mitään 45% nopeutuksia, vaan se lisäkello minkä sillä saa tuo jonkun n. 5% nopeutuksen.

Jos esim tiedettäisiin ajoissa että seuraava sukupolvi myöhästyy niin sillä voisi taikoa helpolla välimallit jotka olisi inasen nopeampi kuin edellinen, lähinnä että saadaan OEM-valmistajille myytyä "uusia" piirejä pakettikoneisiin.

Samaan tapaan kuin tuli esim. Polariksesta(radeon RX 400-sarjasta) hiukan korkeakelloisempi 500-sarja.

N4P => N3X sen sijaan ei onnistu helpolla vaan tulisi selvästi kalliimmaksi ja sen tekeminen veisi enemmän aikaa, N3:sa on ihan erilaiset suunnittelusäännöt kuin N4ssa ja koko fyysinen design pitäisi tehdä uusiksi.

Muistiohjaiman muutos GDDR6 -> GDDR7 saattaisi ehkä olla mahdollista jos olisi jo alunperin ollut suunnitelmat molemmille vaihtoehdoille...

Muistiohjaimen muutos ei oletuksena olisi helppo/nopea juttu vaan vaatisi myös uuden leiskan piiristä. Olisi helppo ja nopea ainoastaan siinä tapauksessa että se alkuperäinen muistiohjain jo tuki GDDR7aa mutta se GDDR7-tuki oli siitä jostain syystä pois päältä, esim. jonkun helposti korjattavissa olevan pikkubugin takia tai koska markkinatilanteen (muistien hintojen tms.) takia ei vaan haluttu käyttää GDDR7aa.

- Liittynyt

- 12.12.2016

- Viestejä

- 4 995

Muistiohjaimen muutos ei oletuksena olisi helppo/nopea juttu vaan vaatisi myös uuden leiskan piiristä. Olisi helppo ja nopea ainoastaan siinä tapauksessa että se alkuperäinen muistiohjain jo tuki GDDR7aa mutta se GDDR7-tuki oli siitä jostain syystä pois päältä, esim. jonkun helposti korjattavissa olevan pikkubugin takia tai koska markkinatilanteen (muistien hintojen tms.) takia ei vaan haluttu käyttää GDDR7aa.

Onko kuitenkaan mahdoton skenaario, että muuten samanlaisesta piiristä olisi sekä GDDR6 että GDDR7 versiot suunnittelu valmiiksi asti, nopeampi vain hyllytetty ennen fyysistä tuotantoa n. vuosi sitten mm. muistin hintojen/saatavuuksien takia ja koska hitaammasta laskettu saavan edelleen ihan hyvä tuotto pienemmällä riskillä? Vuodenvaihteessa kun näitä täysin valmiita kortteja ollut jo kauppojen varastoissa (eli piirien massatuotanto alkanu kesällä 24) ja nähty nVidian Blackwellin taso niin uudelleenaktivoitu tämä GDDR7 versio. Piirituotanto käyntiin nyt kesällä, kortit ulos vuodenvaihteessa.

AMD:llä on nyt rahaa tehdä jossain määrin päällekkäisiä piiriprojekteja. Ilman fyysistä tuotantoa kahdelle eri muistiversiolle suunnitellut muuten identtiset piirit eivät voi olla mitään satojen miljoonien investointeja? Tämmöinen paperilla lähes valmis piiri jos aktivoidaan tuotantoon tilanteiden muuttuessa niin tuollainen vuosi uudelleenaktivoinnista valmiiksi tuotteeksi kuulostaa täysin realistiselta. Ainut huhu siis mistä MLID videossa oli varsinaisesti edes vähäistä lihaa oli 48Gb PRO-kortista, joka olisi tulossa aikaisintaan Q4/25, todennäköisemmin Q1/26. Kaikki muu oli hostin omaa spekulaatiota (vaikka ei tätä selkeästi ilmaissut, tuo käyttää globaalista politiikasta tuttua "strategic ambiguity" -taktiikkaa eli sanoo asioita niin, että voi myöhemmin kiistää vahvistaneensa mitään, pelkästään spekuloineen, mutta toisaalta jos osuukin niin voi väittää julistaneensa asian olleen juuri näin suurella todennäköisyydellä...)

- Liittynyt

- 21.06.2017

- Viestejä

- 7 588

Sen näkee esim. Steamin tilastoja katsomalla. Tai ihan myyntilukuja jos niitä suostuvat paljastamaan. Eli paljonko maailmassa on myyty GTX 5090 korttia julkaisun jälkeen vs. esim. 7090XT korttia mikä on "vähemmän tunnettu" sekä noin yleisesti haluttu kilpailijan kortti. Uskallan väittää että silti siihen on "tyydytty" ihan hinnan takia.

Sieltä tilastoista näkee että esim 4090 malli löytyy korkeammalta kuin yksikään AMD:n kortti. Eli jos tuota tilastoa uskotaan niin kyseistä korttia on myyty kyllä paljon.

5090 tulee siis suurella todennäköisyydellä myös myymään ihan reippaasti. Välttämättä ei samoihin pääse kuin 4090 koska 4090 toi todella suuren loikan suorituskykyyn, mutta jos sieltä tialstosta katsotaan 3090 niin on sekin myynyt.

Kyllä noille kalliille korteille vaan tuntuu kysyntää olevan.

N4P => N4X onnistuu hyvin helpolla, ei tarvi tehdä edes uutta leiskaa. Mutta sillä ei saada mitään 45% nopeutuksia, vaan se lisäkello minkä sillä saa tuo jonkun n. 5% nopeutuksen.

Tuskin kukaan edes väittää että se 45% olisi nodesta saatava nousu vaan eiköhän sillä tarkoiteta "best case" eli node + muistit niin jossain tilanteissa nvidian puolella on nähty ihan merkittäviä nopeuseroja gddr7 hyväksi kun on verrattu about samantehoisia kortteja keskenään.

Viimeksi muokattu:

bahis

Tukijäsen

- Liittynyt

- 06.03.2019

- Viestejä

- 4 130

N4P => N4X onnistuu hyvin helpolla, ei tarvi tehdä edes uutta leiskaa. Mutta sillä ei saada mitään 45% nopeutuksia, vaan se lisäkello minkä sillä saa tuo jonkun n. 5% nopeutuksen.

n. 20% korkeammista kelloista oli maininta joka saavutettaisiin prosessimuutoksella + tehorajojen 20% - 50% nostolla. Muistikaista nousisi myös 50% GDDR7 myötä ja noiden yhdistelmällä best case scenario oli 45% lisää suorituskykyä.

Todella epätodennäköistä kyllä, että tuollaista olisi tulossa. Eiköhän ole ihan jonkun AMD fanipojan kuvitelmaa.

- Liittynyt

- 17.10.2016

- Viestejä

- 2 049

Juu. RTX 5060 sai G7 muisteista aika paljon hyötyä. Seuraavaksi näytönohjaimissa nähdään toinen isompi loikka (lopullisessa) suorituskyvyssä kun 3 Gt muistipiirit saadaan koko tuotestäckiin. Ne siis auttaa tilanteissa joissa 50 sarjan korteilla muisti nyt loppuu kesken.jossain tilanteissa nvidian puolella on nähty ihan merkittäviä nopeuseroja gddr7 hyväksi kun on verrattu about samantehoisia kortteja keskenään

Pelko oli turhaa. 9070XT on havaittavasti nopeampi kuin 3080, varmasti keskimäärin noin 30-50%.Ajoissa paljon ristiriitaa, 2070 nopein. Mutta ei 6900XT näytä häviävän, nyt on kyllä versio 8 jo.

Edit. DxO Photolab 8 kuvanmuunto RAW muodosta.

- Liittynyt

- 20.10.2016

- Viestejä

- 5 237

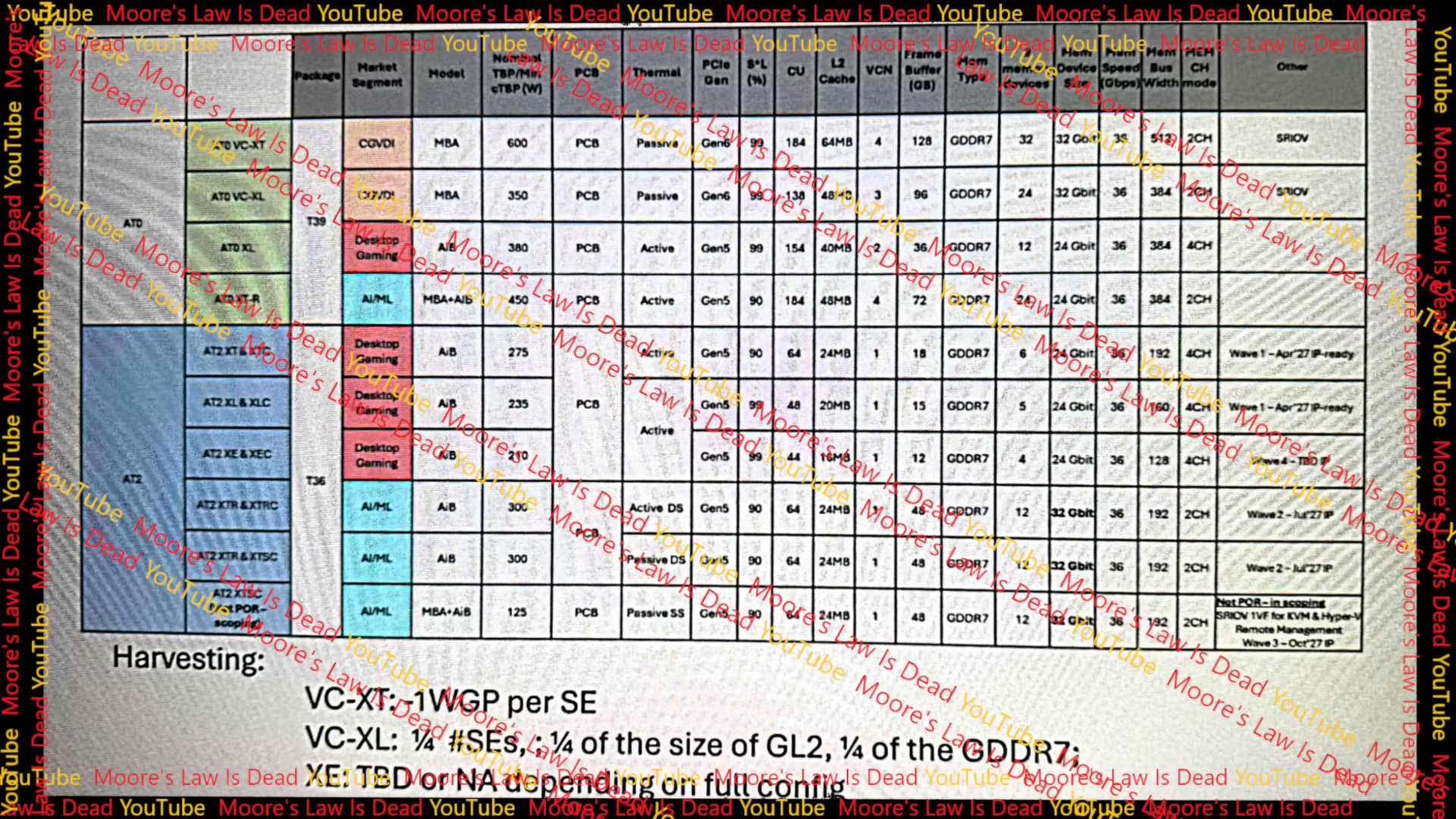

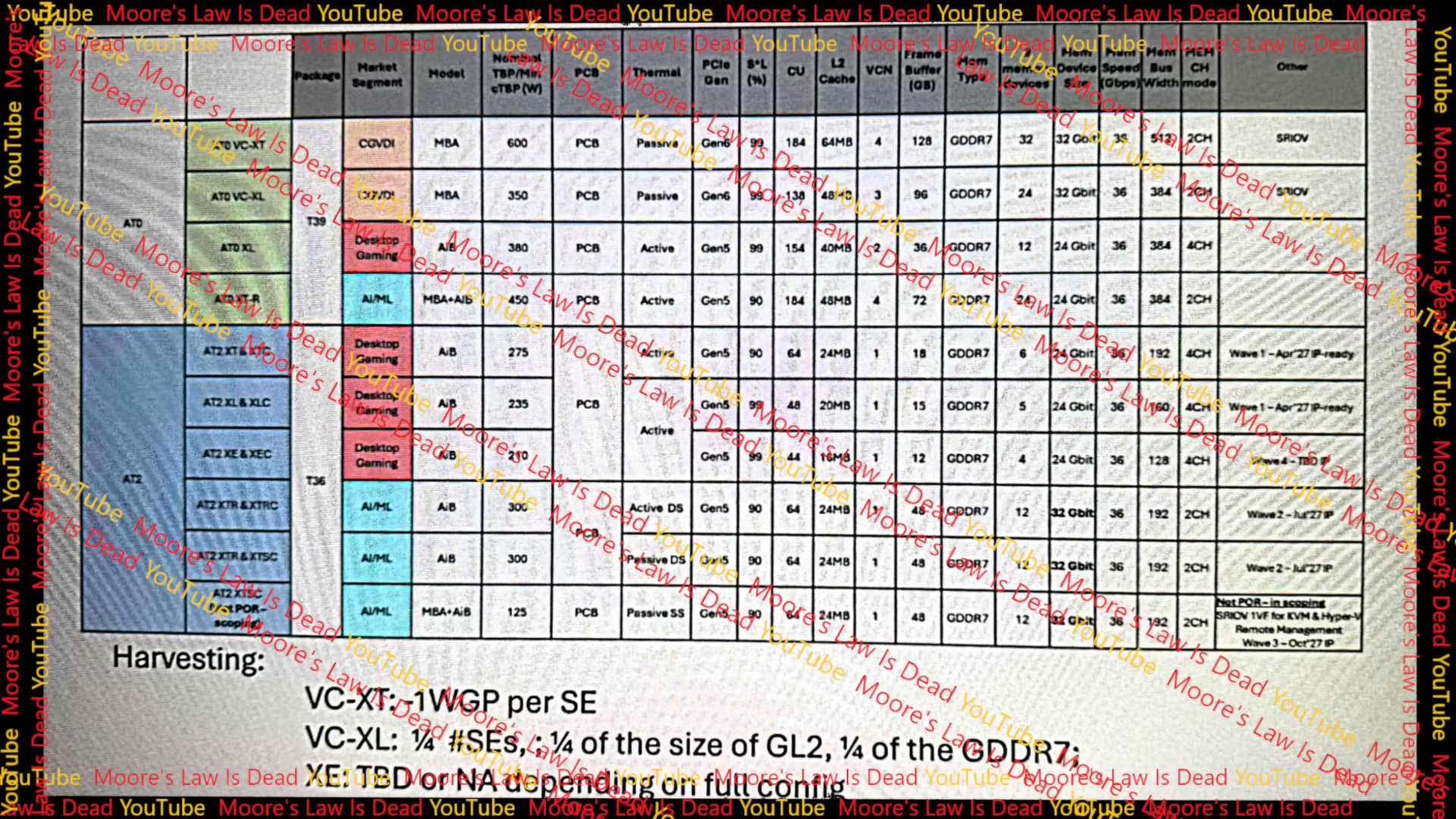

Moore’s Law Is Dead spekuloi tulevista RDNA 5 -piireistä.

Tulossa on ainakin piiriversiot AT0 ja AT2. Lisäksi arvellaan, että olisi tulossa myös kolmas piiriversio AT3, mutta siitä on saatavissa vielä vähemmän tietoa (spekulaatiota).

Lippulaivassa olisi spekulaation mukaan 184 CU:ta, kun esim RX 7900XTX:ssä niitä oli 96 kpl.

Piirissä käytettäisiin 36Gb/s GDDR7 -muisteja 512 bitin väylän kautta, ja virrankulutus (TDP) olisi 600W.

Leikatussa AT0 XL -versiossa TDP olisi 380W ja muistiväylä 384-bittinen.

www.club386.com

www.club386.com

Tulossa on ainakin piiriversiot AT0 ja AT2. Lisäksi arvellaan, että olisi tulossa myös kolmas piiriversio AT3, mutta siitä on saatavissa vielä vähemmän tietoa (spekulaatiota).

Lippulaivassa olisi spekulaation mukaan 184 CU:ta, kun esim RX 7900XTX:ssä niitä oli 96 kpl.

Piirissä käytettäisiin 36Gb/s GDDR7 -muisteja 512 bitin väylän kautta, ja virrankulutus (TDP) olisi 600W.

Leikatussa AT0 XL -versiossa TDP olisi 380W ja muistiväylä 384-bittinen.

RDNA 5 specs leak suggests AMD is cooking up a proper high-end GPU | Club386

AMD isn't holding back with RDNA 5 according to alleged internal documents containing specifications about upcoming GPUs.

finWeazel

Tukijäsen

- Liittynyt

- 15.12.2019

- Viestejä

- 14 115

Kuulostaa yhtä uskottavalta clickbait materialilta kuin navi3x kellotaajuudet, no vähintään respinnin jälkeen kelloa luvassa, eiku viimeistään navi4x:ssa, eikun. En pidättele hengitystä 512bit amd pelipiiriä odotellessa. MLID:n track record niin huono ettei kannata kiinnittää mitään huomiota siihen. Jos paremmat huhupajat alkavat tuollaisista puhumaan niin uskottavuus voisi olla nollaa suurempi.Piirissä käytettäisiin 36Gb/s GDDR7 -muisteja 512 bitin väylän kautta, ja virrankulutus (TDP) olisi 600W.

Leikatussa AT0 XL -versiossa TDP olisi 380W ja muistiväylä 384-bittinen.

- Liittynyt

- 12.12.2016

- Viestejä

- 4 995

Lippulaivassa olisi spekulaation mukaan 184 CU:ta, kun esim RX 7900XTX:ssä niitä oli 96 kpl.

Piirissä käytettäisiin 36Gb/s GDDR7 -muisteja 512 bitin väylän kautta, ja virrankulutus (TDP) olisi 600W.

Leikatussa AT0 XL -versiossa TDP olisi 380W ja muistiväylä 384-bittinen.

Joo-o, uskon kun näen...

Vaikka olisi totta, niin joko nämä ovat jotain muuta kuin pelipiirejä (mahdollisesti kuitenkin myös pelaamiseen soveltuen), ovat chipplettejä ja tuo on joku teoreettinen maksimikoko yhdelle kokonaisuudelle tai CU:n koko pienenee nykyisestä ja muistikaistaa sekä ei selitä. Vaikea nähdä AMD:n tekevät 512 bittisellä muistikaistalla pelipiiriä

bahis

Tukijäsen

- Liittynyt

- 06.03.2019

- Viestejä

- 4 130

Kuulostaa yhtä uskottavalta clickbait materialilta kuin navi3x kellotaajuudet, no vähintään respinnin jälkeen kelloa luvassa, eiku viimeistään navi4x:ssa, eikun. En pidättele hengitystä 512bit amd pelipiiriä odotellessa. MLID:n track record niin huono ettei kannata kiinnittää mitään huomiota siihen. Jos paremmat huhupajat alkavat tuollaisista puhumaan niin uskottavuus voisi olla nollaa suurempi.

Joo-o, uskon kun näen...

Vaikka olisi totta, niin joko nämä ovat jotain muuta kuin pelipiirejä (mahdollisesti kuitenkin myös pelaamiseen soveltuen), ovat chipplettejä ja tuo on joku teoreettinen maksimikoko yhdelle kokonaisuudelle tai CU:n koko pienenee nykyisestä ja muistikaistaa sekä ei selitä. Vaikea nähdä AMD:n tekevät 512 bittisellä muistikaistalla pelipiiriä

Jos katsoitte videota tai tuota taulukkoa niin sen mukaan ei 512bit pelipiiriä olisi tulossakaan vaan pelipuolen lippulaiva olisi 384bit ja 154CU.

512bit kortit tuon mukaan olisi ML/AI ja CGVDI segmentteihin suunnattuja.

- Liittynyt

- 18.10.2016

- Viestejä

- 6 353

Ihme jos ei siirry chiplettiin ainakin lippulaivamallien osalta. Massiivipiirien teko on liian kallista ja hankalaaJoo-o, uskon kun näen...

Vaikka olisi totta, niin joko nämä ovat jotain muuta kuin pelipiirejä (mahdollisesti kuitenkin myös pelaamiseen soveltuen), ovat chipplettejä ja tuo on joku teoreettinen maksimikoko yhdelle kokonaisuudelle tai CU:n koko pienenee nykyisestä ja muistikaistaa sekä ei selitä. Vaikea nähdä AMD:n tekevät 512 bittisellä muistikaistalla pelipiiriä

Uutiset

-

Intelin isoon Battlemageen perustuva Arc Pro B70 pääsi pelitesteihin

6.5.2026 05:35

-

AMD ylsi ensimmäisellä neljänneksellä jälleen ennätysliikevaihtoon

6.5.2026 04:32

-

Ruotsalainen Mionix julkaisi ultrakeveän Avior Air Carbon Fiber -pelihiiren norjalaisella järjestelmäpiirillä

6.5.2026 02:49

-

Samsungin vuosi alkoi menestysneljänneksellä

5.5.2026 04:40

-

Intelin 12 P-ytimellä varustettu Core 9 273PQE pelitesteissä (Bartlett Lake)

5.5.2026 01:16