- Liittynyt

- 14.10.2016

- Viestejä

- 25 074

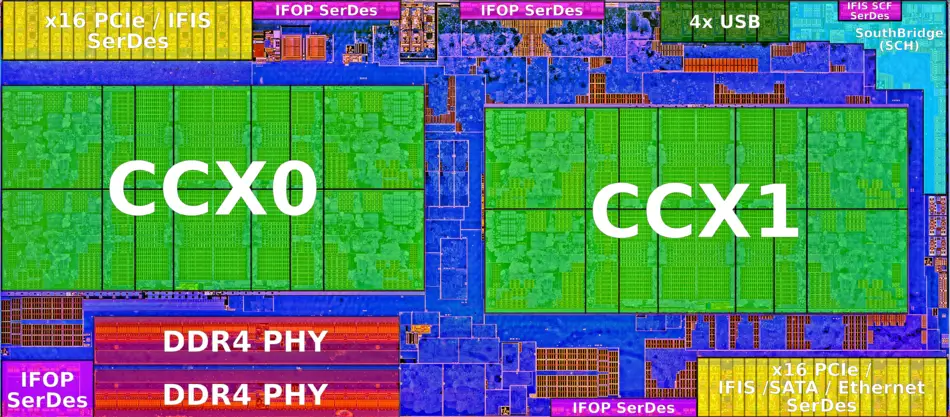

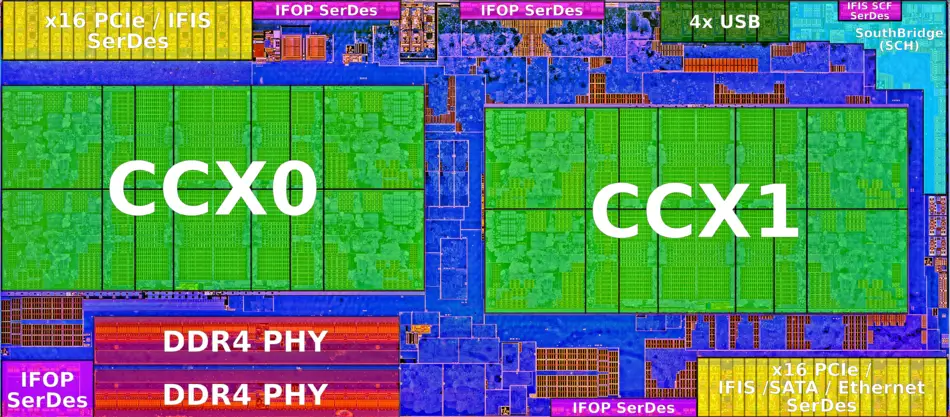

Mutta lue myös se loppuviesti, käytännössä varmasti siellä on 2x4c CCX:t eikä 1x8c CCXJuurikin näin.

Follow along with the video below to see how to install our site as a web app on your home screen.

Huomio: This feature may not be available in some browsers.

Mutta lue myös se loppuviesti, käytännössä varmasti siellä on 2x4c CCX:t eikä 1x8c CCXJuurikin näin.

Edelleen olemassa AM4, TR4 ja SP3 ja nämä Rome-palvelinprosessorit menevät SP3-kantaan, ovat yhteensopivia nykyisten emojen kanssa jne.Vieläkö on olemassa ; AM4 / TR4 / SP3 vai , joko AMD on julkaissut uusia kantoja

Tämän ketjun perusteella on vaikeaa arvailla mihin esitetyt vaihtoehdot sopisivat , mutta

Virallisesti ei ole julkaistu täysin uusia socketteja , ?

Mutta mitä muistia on chipletissä ; erillistä L1 vai yhteistä L3 vai toimiiko noi ytimet ilman mitään omaa muistiaan

Vertaa CCX malliin jota tuskin kuopataan

Ja siihen vielä hiottu piiri mukaan samaan soppaan. 15 vuoden perusteella tiedettiin myös että Epyc 1 on 1 iso piiri ja Epyc 2 tulee olemaan toinen iso piiri... Voin olla kaikesta väärässä, mutta jonkinlaisia älykkäitä argumentteja toivoisin miksi näin on.

Toivoisin teitysti, että luet viestin kokonaan jossa mainetsenkin puheen olevan Epyc2:sta.

Ensinnäkään missään ei ole sanottu Zen2 piirin olevan 2CCX ja osa on jopa sitä mieltä ettei sinne sellainen mahtuisikaan. Miten sen saman CPU ja IO piirin latenssi kasvaa muisteille jos se otetaan EPYC2 ja laitetaan AM4 alustalle?

Toisaalta AMD:n resursseilla ei kaiken järjen mukaan ala tekemään intelin tapaan ties kuinka montaa erilaista piiriä, kun jokaisen aloituskustannuksetkin ovat suuret (suunnittelut, maskit, testit). Aivan mahdollista pari eri piiriä toki on, mutta olettamus suuntaan tai toiseen ei näytä minusta sen todenäköisemmältä.

Edelleen olemassa AM4, TR4 ja SP3 ja nämä Rome-palvelinprosessorit menevät SP3-kantaan, ovat yhteensopivia nykyisten emojen kanssa jne.

Tuki ainakin AM4-kannalle ja muistaakseni muillekin on luvattu 2020 asti, sitä en muista oliko lupaus että 2020 julkastavat prossut sopivat vai että 2020 tulee aikaisintaan uusi kanta. Olikohan AnandTechin haastattelussa missä Papermaster sanoi aika suoraan että kanta vaihtuisi kun siirrytään DDR5-muisteihin (ja PCIe 5.0:aan ilmeisesti samassa rytäkässä)

Chipletissä on varmasti L1-välimuistit ja käytännössä varmasti L2- ja L3-välimuistit. Jos käytössä on myös L4-taso se voisi olla I/O-piirillä.

Teknisesti voiko AM4-kanta tukea DDR5:ttä vai ei riippuu toki siitä tarvitaanko sen kanssa lisäpinnejä vai ei, mutta sitä ei tulisi kuitenkaan ikinä tapahtumaan, koska se vain sotkisi markkinoita kun pitäisi arpoa mikä AM4-prossu sopii mihin AM4-emoon jne.Luvattiin "tukea" 2020 saakka, joka tarkoittanee 2020 prosessorien sopivan AMD:n puolesta AM4 kantaan. Emolevyjen tuki erikseen. AMD voisi tukea myös DDR5-aikakaudella AM4:a mutta AM4 tulee olemaan niin pitkäikäinen kanta ettei olisi paha juttu vaikkeivät tukisi.

Edelleen olemassa AM4, TR4 ja SP3 ja nämä Rome-palvelinprosessorit menevät SP3-kantaan, ovat yhteensopivia nykyisten emojen kanssa jne.

Tuki ainakin AM4-kannalle ja muistaakseni muillekin on luvattu 2020 asti, sitä en muista oliko lupaus että 2020 julkastavat prossut sopivat vai että 2020 tulee aikaisintaan uusi kanta. Olikohan AnandTechin haastattelussa missä Papermaster sanoi aika suoraan että kanta vaihtuisi kun siirrytään DDR5-muisteihin (ja PCIe 5.0:aan ilmeisesti samassa rytäkässä)

Chipletissä on varmasti L1-välimuistit ja käytännössä varmasti L2- ja L3-välimuistit. Jos käytössä on myös L4-taso se voisi olla I/O-piirillä.

Sinä täysin tahallaan jätät huomiotta se ison eron että silloin 15 vuotta sitten se muistiohjain oli kaukana prrosessorista emolevyllä sen suhteellisen hitaan ja kapean prosessoriväylän päässä eikä samasa paketoinissa chipletin vieressä ja dedikoidulöa väylällä per chiplet.Huono vertaus. Viimeiset 15 vuotta prosessoriin integroitu muistiohjain on tarjonnut selvästi alemmat latenssit kuin muistiohjain erillisellä piirillä suunnilleen saman aikakauden prosessoreissa. Juuri tuo pienempi latenssi oli alunperinkin tärkein syy miksi AMD siirsi muistiohjaimen prosessoriin.

Joten melkoista magiaa saa AMD säätää jos latenssi pienenee siirtämällä muistiohjain erilliselle piirille. Ei tarvitse ennustella koska asia on itsestäänselvyys. Tuo tahnaesimerkki on vastaava. Olihan mahdollista että tahnalla saadaan pienemmät lämmöt jos se tahna olisi ollut joku uusi ihmekeksintö. Eipä ollut eikä yllättänyt.

...

Nyt en ihan ymmärrä, kaikissa Zeppelin-pohjaisissa on käytössä ihan "sama niputus", eli jokaisella sirulla on omat 2 kanavaansa, poislukien 2. sukupolven TR:t joissa kahdesta sirusta on poistettu muistiohjaimet käytöstä.Tuohon jatkoa ; onko tämän Epycin muistiohjain yksi yhtenäinen 8-kanavainen vai Threadripper johdannannainen 2x4-kanavaa vai jopa Ryzen perintöä 4x2 kanavan niputus

Toistaiseksi ei ole kerrottu yksityiskohtia, mutta graafien perusteella kaikki liikenne menee I/O-sirun kautta.Miten nuo chipletit on ositettu , onko kaikki sisään / ulos tietoliikenne linkitetty pelkästään tämän I/O sirun kautta vai onko chiplet-ytimillä suorat kontaktit myös muisti / pcie väyliin

1 - 2 chiplettiä ja pienempi I/O-siru tai yksi isompi siru jossa on 8 - 16 ydintä (henk.koht. en usko että menisi 16 ytimeen mutta ei sitä tietenkään ikinä tiedä)Tämä ihan vaan ihmettelynä , miten kuluttaja-luokan uudet prossut voitaisiin suunnitella , tuskin ne kuitenkaan tulevat lähivuosina perustumaan mihinkään ilmakoukkutekniikkaan

Muistanko oikein että vaikka on 2 64 bit kanavaa niin se kumminkin pystyy tekemään myös 32 bittilisä lukuja ja kirjoituksia ts kerralla ei tarvi tehdä koko kanavan (64 bit) levyistä operaatiota.Nyt en ihan ymmärrä, kaikissa Zeppelin-pohjaisissa on käytössä ihan "sama niputus", eli jokaisella sirulla on omat 2 kanavaansa, ...

Mutta lue myös se loppuviesti, käytännössä varmasti siellä on 2x4c CCX:t eikä 1x8c CCX

Muistanko oikein että vaikka on 2 64 bit kanavaa niin se kumminkin pystyy tekemään myös 32 bittilisä lukuja ja kirjoituksia ts kerralla ei tarvi tehdä koko kanavan (64 bit) levyistä operaatiota.

Jos puhut nyt noista prosessori-chipleteistä niin olet oikeassa, ei ole sanottu että olisi 2 CCX:ää, mutta mikäli CCX on edelleen 4 ydintä (perusteluita miksi näin olisi löytyy jo aiemmin ketjusta) niin sitten niissä on 2 CCX:ää, koska kahdeksan chipletin piiri on 64-ytiminen

Vetoja? Kumpi tahansa on mahdollista. Itse en näe mitenkään käytännössä varmaksi 2x4 ratkaisua. Molemmilla on teknisiä etuja ja haittoja.

Sinä täysin tahallaan jätät huomiotta se ison eron että silloin 15 vuotta sitten se muistiohjain oli kaukana prrosessorista emolevyllä sen suhteellisen hitaan ja kapean prosessoriväylän päässä eikä samasa paketoinissa chipletin vieressä ja dedikoidulöa väylällä per chiplet.

Alkoi kiinostaa... mutta minä postasin benchmarkit tilanteesta, jossa se ei ollut kaukana emolevyllä vaan samassa MCMssä.

Ja huomattava lisäviive silloinkin.

AMD esitteli 7 nanometrin Zen 2 -prosessorit ja Vega 20 -grafiikkapiirin

Tämä +1!Alkoi kiinostaa

Valitettavast CPU Wordilla ei ole i7-980X mallin välimuisti latensejen tietoja

(niin että näkisi mikä osa latenssista johtuu nimeomaan siitä erilisestä musitiohajimesata)

i7-980X

Level 1 cache size ? 6 x 32 KB 4-way instruction 6 x 32 KB 8-way data caches

Level 2 cache size ? 6 x 256 KB 8-way set associative caches

Level 3 cache size 12 MB 16-way set associative shared cache

i5-661

Level 1 cache size ? 2 x 32 KB instruction caches 2 x 32 KB data caches

Level 2 cache size ? 2 x 256 KB

Level 3 cache size 4 MB shared cache

Cache latency

4 (L1 cache)

10 (L2 cache)

39 (L3 cache)

Jos Zen2:lla on jättimäinen L4 joka vähentää suoraa keskusmusitin käyttöä se tietenkin autaisi kononaisviiveisiin merkittävästi.

i5-661 latenssin n. tuplautuu L3:n ja keskumusitin välillä kun taas Zen1 Epyc/Threaripper latenssin eri sirujen L3 hakujen välillä yli tuplautuu (jos muistan oikein) ts Zenillä on lähtokohtaisesti paljon parannetavaa että pääsee edes tuohon i5-661 tasoon ts on syytä olettaa että AMD on parantanut sitä merkittävästi tai muuten koko Chiplet idea olisi itsetuho.

Vai mokasinkon tuon i5-661 välimuisti viiveen tulkinassa (sivulta puutui määre joten onko se ns:iä vai kellojaksoja).

Nyt tässä taas pohdin, että mikäli erilliselä piirillä toteuttavat Ryzenit saattaisi 3 ccx ehkä olla myös mahdollinen (?)

12 ydintä ehkä vielä olisi sellainen että pienemmällä prosessilla teho ei karkaa emolevyspeksien ulkopuolelle (tai tarvitse laskea kelloja nykyisiä alemmas).

Eikai tuollaisen 3 ccx toteuttamiselle samalle piirille ole teknisesti kahta juuri hankalampi? (symmetria?, piirin epätasainen lämmöntuotto?)

Tosin oma veikkaus on, että keskittyvät kasvattamaan IPC:tä ja nostamaan kellotaajuuksia. Kuitenkin alkaisi kilpailla 12 ytimellä jo TR4 kantaisten kanssa osasta ostajia.

(Oletuksena, että zen2-threadripper tehdään disabloimalla Romen IO-piiristä puolet muistikanavista, ja lätkimällä sinne sopiva määrä Romen CPU-chiplettejä; En usko, että threadripperiä varten tulee mitään uutta piilastua)

Voisiko AMD laitaa tuohon IO piiriin vastaavat muistien varjotagit jotka tarkistaessa ydin/CCX/chiplet tietäisi voiko tiedon hakea toisen Chipletin välimuistista (ja minkä chipletin missä välimuistissa se tieto on) IO-piirin L4 muistista vai täytyykö se halkea keskusmuistista.... tosin onneksi tätä helpottaa L3n yhteydessä olevat L2ien "varjo-TAGit" joilla L2-osumatarkastukset saa tehtyä samalla L3-osumatarkastuksen kanssa). ....

Teknisesti voiko AM4-kanta tukea DDR5:ttä vai ei riippuu toki siitä tarvitaanko sen kanssa lisäpinnejä vai ei, mutta sitä ei tulisi kuitenkaan ikinä tapahtumaan, koska se vain sotkisi markkinoita kun pitäisi arpoa mikä AM4-prossu sopii mihin AM4-emoon jne.

Kyllä se tuki luvattiin ihan emolevytasoa myöden.

Sinä täysin tahallaan jätät huomiotta se ison eron että silloin 15 vuotta sitten se muistiohjain oli kaukana prrosessorista emolevyllä sen suhteellisen hitaan ja kapean prosessoriväylän päässä eikä samasa paketoinissa chipletin vieressä ja dedikoidulöa väylällä per chiplet.

Jokatapauksessa Threadripperin väitemä mättää kun hän perustelee näillä viiveillä sitä että siksi AMD tekisi kokonaan eri piirin AM4 Ryzen (ei iGPU) malleja varten ja samaan aikaan vitää että AMD ei tekisi Apua 8:lla ytimellä jos tuo toteutuisi AMD joutuisi tekemään kolme täysin eriä prosesori tuotetta Zen2 sukupolveen Chipletit Epycejä (ja Thradripperejä) varten, 8-(16) ytimisen Ryzeniä vartten ja 4 ytimisen Apua varten.

Kun tosiasia on se että jos viiveet on niin suuret että sen takia Chipelttejä ei käytetä Ryzeneissä se ratkaisu mihin AMD kaupallisista systä (ei liikaa fyysisiä tuotteita toimitus/varasto ketjussa) päätyy on se että se tekee 8 ytimisen Apun jota myydään myös iGPU:tomana Ryzeninä (se iGPU puoli on vain kytketty pois käytöstä), kun se "7nm" 8 ydin Apu piirin fyysinen koko ei ole niin merkittävä kustannustekijä kuin mitä Threadripper haluaa uskoa.

Jotenkin vaikea uskoa että oltaisiin lähdetty huonontamaan tilannetta vain serveriraudan vuoksi unohtaen kaikki muut markkinat. En oo millään tavalla mikään specialisti mutta luulis että serveripuolellakin hitaista viiveistä on haittaa?

Kolmas CCX ei olisi käytännössä millään tavalla poissa IPCstä(*) eikä turbokelloista. Se voisi olla jopa oikein hyvä kompromissi.

Peruskellot olisi toki alemmat kuin kahdella CCXllä samanlaisilla ytimillä, mutta monen säikeen suorituskyky silti parempi. Ja verrattuna nykymalleihin peruskellot voisi silti todennäköisesti olla korkeammat.

Kilpaileminen TR4-kantaisten kanssa ei olisi AMDlle ongelma sen takia, että se 3-CCXäinen ryzen olisi kuitenkin halvempi valmistaa kuin EPYCistä cripplattu/downskaalattu threadripper. Ja mitä halvemmalla valmistettavan piirin saa myytyä samaan markkinasegmenttiin, sitä enemmän jää katetta käteen.

(Oletuksena, että zen2-threadripper tehdään disabloimalla Romen IO-piiristä puolet muistikanavista, ja lätkimällä sinne sopiva määrä Romen CPU-chiplettejä; En usko, että threadripperiä varten tulee mitään uutta piilastua)

(*) Toki lisä-CCXn tuoma inasen monimutkaisempi väylärakenne piirin eri osien välillä voi inasen hidastaa kommunikaatiota CCXien välillä tai muistille, mutta tämän vaikutus on hyvin, hyvin pieni, käytännössä merkityksetön.

Kovasti puhuuvat jotta IO-die on valmistettu 14nm prosessilla joten olisiko se sitten tosiaan sillä IBM:ltä perityllä prosessilla valmistettu ja sekin on varmaa että IO-die tulee GF:ltä.

Mikäli se tehdään sillä kalliilla prosessilla niin ehkä threadrippereihin olisi kannattavaa valmistaa leikattu piiri, puolet muistikaistoista veke ja puolet kakusta veke. Toki se riippuu varmaan pitkälti siitä millaisia määriä AMD ennakoi myyvänsä Threadrippereitä.

Mainaan kun joku ratkaisu AMD:n on täytynyt keksiä näiden muistiviive ongelmien lievittämiseen tai muutoin koko chiplet pohajiseen rakenteeseen siirtyminen olisi umpikuja, käytännössä se kävisi vain Epyc ja Threadripper tuotteisiin ja AMD hehkutuksen perusteella uskon että AMD aikomus on käytää chiplet toteutusta tulevaisuudessa laajemminkin kuin vain kahdessa tuoteessa.

Kahdella eri prosessorikannalla. Se ei ollut AM2+ kaksilla muisteilla tai AM3 kaksilla muisteilla, vaan oli prosessori joka sopi sekä AM2+ että AM3-emoihin ja tuki molempia muisteja, kun emot tukivat yhtä muistia. Se on täysin eri asia kuin AM4-emolevy joka tukisi vain osaa AM4-prosessoreista sen perusteella mitä muistia emoon voi lykätä.AM2+/AM3 aikana AMD tuki kahta muistityyppiä samalla prosessorilla.

AMD ei tee emolevyjä, joten tuki riippuu lopulta emolevyjen valmistajista.

Ei AMD sanonut sanaakaan tuon käytöstä missään muualla kuin 64-ytimisessä Epycissä. Ja kun sitä Epycciä voidaan ihan helposti myydä kymppitonnilla kappale eikä Intelillä ole mitään sitä vastaan, noilla spekseillä voi chiplet-ratkaisun suunnitella vain yhdelle mallille.

Kahdella eri prosessorikannalla. Se ei ollut AM2+ kaksilla muisteilla tai AM3 kaksilla muisteilla, vaan oli prosessori joka sopi sekä AM2+ että AM3-emoihin ja tuki molempia muisteja, kun emot tukivat yhtä muistia. Se on täysin eri asia kuin AM4-emolevy joka tukisi vain osaa AM4-prosessoreista sen perusteella mitä muistia emoon voi lykätä.

AMD voi piirisarjojen myyjänä edellyttää että niitä käytetään vain emolevyillä jotka tukevat kaikkia.

Se on ihan hyvin voinut olla myyntiehdoissa mukana, meillä ei ole tietoa sopimuksen sisällöstä mutta on tieto, että AMD uskaltaa sen tuen luvataAMD ei voi pakottaa tekemään jokaiseen emolevyyn BIOS päivityksiä jotta tukisivat uusia prosessoreita. Se on asia joka mietityttää tällä hetkellä.

Sinä veisaat latenssi virttä kuin jonain kiveenhakattuna totuutena. Tosiasia on se että sinun totuudet tämän asian suhteen on ihan yhtä paljon mutua kuin kaikkien muidenkin veihtoehdot koska AMD on ollut erittäin salamyhkäinen eikä ole avannut juuri lainkaan asiaa sen enempää. Ensivuoden puolella ollaan huomattavan paljon viisaampia ja nähtään että kene lottorivi lopulta osui parhaiten kohdilleen.

Tästä vänkäämistä on varmaan aivan turha jatkaa ennenkuin saadaan jotain uutta infoa.

Sinä veisaat latenssi virttä kuin jonain kiveenhakattuna totuutena. Tosiasia on se että sinun totuudet tämän asian suhteen on ihan yhtä paljon mutua kuin kaikkien muidenkin veihtoehdot koska AMD on ollut erittäin salamyhkäinen eikä ole avannut juuri lainkaan asiaa sen enempää. Ensivuoden puolella ollaan huomattavan paljon viisaampia ja nähtään että kene lottorivi lopulta osui parhaiten kohdilleen.

Tästä vänkäämistä on varmaan aivan turha jatkaa ennenkuin saadaan jotain uutta infoa.

Onko tilanne, etteivät tarkista muiden ccx:ien muisteja ollenkaan tietoisena valintana, vaan hakevat suoraan keskusmuistista, jos ei löydy L4-muistista mielekäs? Siis miten merkittävä menetys suorituskyvylle olisi se, että välillä haetaan keskusmuistista vaikka tieto sattuisi olemaan jonkin toisen ccx:n muistissa?Yksi oleellinen syy zen1n hitaaseen muistiviiveeseen on toisen CCXn välimuistien tarkastaminen.

Intelillä on kaikille ytimille(sekä myös näyttikselle) yhteinen LLC (CPUn näkökulmasta L3, näyttiksen näkökulmasta L4)-välimuisti. Kun siitä tulee huti, voidaan välittömästi alkaa hakemaan dataa muistista.

Ryzenilla tarvii vielä tarkastaa tilanne, että "entäs jos se data löytyykin toiselta CCXltä?". Eli kun ollaan tarkastettu että omasta L3sta tulee huti, pitää seuraavaksi tarkastaa toisen CCXn välimuistit(ja tässä ei riitä edes pelkkä L3 vaan voi olla myös toisen CCXn L2ssa, koska L3 ei ole inklusiivinen L2n suhteen, tosin onneksi tätä helpottaa L3n yhteydessä olevat L2ien "varjo-TAGit" joilla L2-osumatarkastukset saa tehtyä samalla L3-osumatarkastuksen kanssa).

Ja vasta kun selviää, että dataa ei löydy toisenkaan CCXn välimuisteista, kannattaa sitä alkaa hakemaan DRAM-muistista.

Raven Ridgellä ei ole toista CCXää, mutta sen GPU taitaa olla välimuistikoherentti CPUn kanssa(ja se GPU ei käytä samaa L3sta kuin CPU), jolloin samat tarkastukset pitää kuitenkin tehdä GPUn välimuisteista. (tästä Raven Ridgen GPUn välimuistikoherenttiudesta en ole aivan varma).

Piiri, jossa olisi vain yksi kahdeksan ytimen CCX eikä ollenkaan näyttistä mahdollistaisi siis selvästi alhaisemman muistiviiveen. Kahdeksan ytimen CCX kuitenkin helposti lisäisi L3n viivettä jonkin verran.

Onko tilanne, etteivät tarkista muiden ccx:ien muisteja ollenkaan tietoisena valintana, vaan hakevat suoraan keskusmuistista, jos ei löydy L4-muistista mielekäs? Siis miten merkittävä menetys suorituskyvylle olisi se, että välillä haetaan keskusmuistista vaikka tieto sattuisi olemaan jonkin toisen ccx:n muistissa?

Siis L4 muisti oisi hyödytön, mikäli ei tarkistaisi toisten ccx:ien L3 ja L2? Tarkoitan, että tolla I/O-piirillä olisi L4 ja jos siihen ei osuisi ei lähtisi tarkistelemaan jokaista muuta ccx:ää. Vai pystyykö kaikkien muiden CCX:ien välimuistit tarkistamaan yhdellä kertaa? Jos tossa oisi 16 ccx:ää kuten todennäköiseltä näyttää. Joutuisiko tarkistamaan jopa 15 kertaa onko toisen ccx:n muistissa?Silloinhan se L4 välimuisti olisi hyödytön, ei siihen silloin kannattaisi pahemmin transistoreja tuhlata.

Taitaa liene nyt haku keskusmuistista olla noin 3-4x pitempi viiveinen kun jos löytyy L3:sta. Tarkistelu viiveet on varmasti lyhyemmät.

Onko tilanne, etteivät tarkista muiden ccx:ien muisteja ollenkaan tietoisena valintana, vaan hakevat suoraan keskusmuistista, jos ei löydy L4-muistista mielekäs? Siis miten merkittävä menetys suorituskyvylle olisi se, että välillä haetaan keskusmuistista vaikka tieto sattuisi olemaan jonkin toisen ccx:n muistissa?

Okei, eli on pakko tarkistaa. Funtsin vaan, jos ois nopeampaa suunnata tossa suoraan välimuistiin mikäli I/O piirin muistista ei löytyis, mut tää selvensi. Eli ei voiEi intelillä ole mitään ccxiä. Ja kun intelillä(vielä coffee lakessa ja sitä vanhemmissa prossuissa) LLC ja L2 ja L1t ovat kaikki keskenään inklusiivisia, riittää tarkastaa L3, koska tällöin jos jotain ei ole L3ssa, sitä ei ole myöskään L2ssa eikä L1ssä. zenissä L2 ja L3 eivät ole keskenään inklusiivisia(L1t ja L2 ovat) joten pitää tarkastaa myös L2(mutta ei L1siä).

Tosin skylake-sp:ssä tämä inklusiivisuus poistui L2n ja L3n väliltä intelillä, siinä pitää tarkastaa myös L2t. Veikkaan, että siinä on niiden tarkastamiseen jotain zenin varjo-tagien tapaisia optimointeja.

Välimuistin koherenttius pakottaa varmistamaan, että missään ei ole datasta likaista kopiota.

Okei, eli on pakko tarkistaa. Funtsin vaan, jos ois nopeampaa suunnata tossa suoraan välimuistiin mikäli I/O piirin muistista ei löytyis, mut tää selvensi. Eli ei voi

Ei Minä en sanonut yksi minä sanoin kaksi, ts kaksi eri CPU toteutusta (Chiplet ja Apu) ja yksi tai kaksi IO-piiriä (riipuen siiitä tuleeko erilisiä Ryzen (IO-piiriä käyttäviä) malleja vai toteutetaanko kaikki Ryzen mallit Apuja karsimalla....

Taas ollaan vähän liikaa otettu mallia Ryzenistä "pakko valmistaa vain yhtä piiriä".

...

Jotain tuonkaltaista itse kuvittelin olevan siinä IO-Piirissä, AMD:han oli tässävaihessa ihan tahallaan hyvin vähäsanainen IO-Piirin sisälllöstä/toiminnasta ja se IO-Piiri on ainoa "ässähihassa" jolla AMD pystyy kiertämään noita latenssi ongelmia....

2) Se on iso ja inklusiivinen kaikkien CCXien välimuistien kanssa. Silloin riittää tarkastaa, onko jotain dataa siellä. Jos ei ole, ei sitä voi olla myöskään minkään CCXn L3ssa eikä minkään ytimen L1/L2ssa

3) Se ei ole inklusiivinen CCXien välimuistien kanssa. Tällöin tarvii tarkastaa CCXien välimuistit.

4) Se on muistin puolella jolloin tämän suhteen on kuin sitä ei olisi (tästä lisää alempana)

...

Ei Minä en sanonut yksi minä sanoin kaksi, ts kaksi eri CPU toteutusta (Chiplet ja Apu) ja yksi tai kaksi IO-piiriä (riipuen siiitä tuleeko erilisiä Ryzen (IO-piiriä käyttäviä) malleja vai toteutetaanko kaikki Ryzen mallit Apuja karsimalla.

Tosin jos vängällä haluat että Thredripperissä ei käytetä chiplettejä niin voisihan sitä jonkunlaisen vanilla Treadripperin toteutta käyttämättä kahta Apua (ilman iGPU:ita) yhdessä Threaripperissö ;-p

Juuri tuo kaksi Ryzeniä (ilman APU:a) Threadripperiin on se todennäköisin skenaario.

Ja edelleen, yhden piirin toteuttaminen 7nm prosessille on $300M.

Nyt heitän oman veikkauksen, että vetäsevät kumminkin sen 3 ccx ryzenin, 1 ccx apun ja threadripperit sit joko ryzenit liimaillen tai epyc pohjaisina (mahd molempia, jos tulee suuria ydinmääriä)

Tuolla sais AM4 kannalle 4 core apun, 6,9 ja 12 core ryzenit. Nykyisinkin se 4 core ryzen ilman apua taitaa olla melko marginaalituote (jonka voisi tehdä apuistakin, jos markkinoilla haluaa pitää) ja voisihan kai siitä 3 ccx sulkea yhden kokonaan... kai

Onko siinä virransyötön pinnit joka ytimelle, vai miksi pinnit loppuisivat? Eikö virransyöttöä voisi reitittää niin että saisi ytimet virtaa? I/O- puoli kuitenkaan ei muuttuisi emolevyn suuntaan kun olisi sama määrä pcie linkkejä ja muistiväyliä.AMD on kehittänyt vuosia Ryzen moduuliprossuja , Summit . Raven , Pinnacle

Nuo kaikki perustuvat CCX moduuliin jossa on 4-Zen ydintä , tuntuisi hullun hommalta hylätä kaikki tehty kehitystyö

Jos taasen CPU hun ängetään 3s CCX niin AM4 socketin pinnit loppuvat kesken ja koko IF kalvosto menisi uusiksi

Noissahan on jonkun "mikälie" alihankkija muistinohjaimet jotka ovat se pullonkaula

Vaan eipä tunnu kukaan tietävän tai arvaavan millaiset muistiohjaimet uusissa Epyceistä löytyy

AMD on kehittänyt vuosia Ryzen moduuliprossuja , Summit . Raven , Pinnacle

Nuo kaikki perustuvat CCX moduuliin jossa on 4-Zen ydintä , tuntuisi hullun hommalta hylätä kaikki tehty kehitystyö

Jos taasen CPU hun ängetään 3s CCX niin AM4 socketin pinnit loppuvat kesken ja koko IF kalvosto menisi uusiksi

Noissahan on jonkun "mikälie" alihankkija muistinohjaimet jotka ovat se pullonkaula

Onko siinä virransyötön pinnit joka ytimelle, vai miksi pinnit loppuisivat? Eikö virransyöttöä voisi reitittää niin että saisi ytimet virtaa? I/O- puoli kuitenkaan ei muuttuisi emolevyn suuntaan kun olisi sama määrä pcie linkkejä ja muistiväyliä.

Vaan eipä tunnu kukaan tietävän tai arvaavan millaiset muistiohjaimet uusissa Epyceistä löytyy

Nyt en kyl hiffaa mitä ajat takaa. Siis jos (kun) ovat suunitelleet uudelleen piirin zen 2 en ymmärrä miksei ccx:iä olisi voinut sijoittaa "vinkkeliin" niin, että valmis piiri on nelikanttinen ja I/O-alue on yhdessä nurkassa. Olennaistahan tässä on se, että pienemmällä nodella tehonkulutuksen samoilla kelloilla pitäisi huomattavasti laskea ja osakuorma boosteissa ei kaikki ytimet ole käytössä.Fyysisesti tuo Ryzen PCB on rajallinen , 3s CCX olisi pakko sijoittaa kahden valmiin moduulin väliin , mutta just siellä sijaitsevat nuo prossun IO ( in/ out ) komponentit , ne olisi joko siirrettävä tai lisättävä IF kalvostoa , mutta tuollainen vehje todennäköisesti polttaisi itsensä jos se saataisiin käynnistymään , ainakaan AMDn vakiojäähyt eivät riittäisi mihinkään

Emovalmistajilla on ollut ratkaisemattomia ongelmia tuotannon siirtyessä 14LPP FinFET tekniikasta 12 LP FinFET tegnologiaan , eli tuskin nykyiset AM4 emot kykenisivät yhtymään noihin 3-kanta grilleihin

Sen sijaan TR pohjaan voisi tulla prossu jossa pohjana olisi Zen -moduuli ja toisen moduulin paikalla 2 Rome lähtöistä Chiplettiä jolloin siellä olisi paljon työytimiä , todennäköisesti tälläinen sekarakenne vaatisi moduulien väliin L4 / L5 palikan puskuroimaan prossun sisäistä ja io liikennettä

Fyysisesti tuo Ryzen PCB on rajallinen

, 3s CCX olisi pakko sijoittaa kahden valmiin moduulin väliin , mutta just siellä sijaitsevat nuo prossun IO ( in/ out ) komponentit , ne olisi joko siirrettävä tai lisättävä IF kalvostoa

, mutta tuollainen vehje todennäköisesti polttaisi itsensä jos se saataisiin käynnistymään , ainakaan AMDn vakiojäähyt eivät riittäisi mihinkään

Emovalmistajilla on ollut ratkaisemattomia ongelmia tuotannon siirtyessä 14LPP FinFET tekniikasta 12 LP FinFET tegnologiaan

, eli tuskin nykyiset AM4 emot kykenisivät yhtymään noihin 3-kanta grilleihin

Sen sijaan TR pohjaan voisi tulla prossu jossa pohjana olisi Zen -moduuli ja toisen moduulin paikalla 2 Rome lähtöistä Chiplettiä jolloin siellä olisi paljon työytimiä , todennäköisesti tälläinen sekarakenne vaatisi moduulien väliin L4 / L5 palikan puskuroimaan prossun sisäistä ja io liikennettä

Prosessoria ei rakenneta ilmaan vaan piirilevyn päälleProsessoria ei tehdä PCBstä vaan piistä..

/files/styles/1200px/private/102426-zen-core-die-shot-1260x709.jpg?itok=02n8zFZ1

Lämmöntuotto ei ole ongelma ? Paljonko lyöt vetoaKun nuo CCXt putoaa pinta-alaltaan noin puoleen "7nm" valmistustekniikan myötä, niitä mahtuu aivan helposti 3 vierekkäin.

Tai sitten niitä mahtuu kaksi päällekkäin ja kolmannen päälle vaikka näyttistä. Tai sitten niitä mahtuu 4 2x2-muodostelmaan, koska paketti on nelikulmainen ja siinä on todella runsaasti tilaa pystysuunnassa kun tuo nyky-zeppelin on noin pitkulainen.

7nm valmistustekniikan uhotaan pudottavan sähkönkulutus puoleen samalla kellotaajuudella.

Ja jännitettä ja kelloa hiukan pudottamalla saa sähkönkulutusta ja lämmöntuottoa todella helpolla paljon alemmaksi. (jollain n. 20% kellotaajuuspudotuksella pääsee n. puoleen sähkönkulutukseen ja lämmöntuottoon)

Että lämmöntuotto ei todellakaan ole yhtään mikään ongelma vaikka ytimien määrää lisättäisiin.

Siis mitä tämä tarkoittaa ? emoilla Ei ole väyliä / prossuilla ei ole väyliä. Ja emolevyjä ei tuoteta milään tuollaisilla tekniikoilla, ne on PCBtä eikä piitä..

Mitä tekemistä piillä on PCB väylien kanssa

Mitä ihmettä tuo lause on edes tarkoittavinaan?

QUOTE="hkultala, post: 3917969, member: 4329"]

Hohhoijaa. Nyt ollaan pihalla kuin lumiukko.

Ei välimusitit tule minkään eri ydinten väliin vaain ydinten ja MUISTIN väliin. Niiden tehtävä on nopeuttaa MUISTIHAKUJA, eikä käskykannassa edes ole mitään käskyjä siirtää dataa suoraan ydinten välillä vaan ainoastaan käskyt siirtää dataa musitiin tai muistista. "ydinten välinen kommunikaatio" on vain sivuvaikutusta siitä, että muistista osoitettava data onkin ennestään jo jonkun muun ytimen välimuistissa.

Prosessorit ja kaikki vastaavat puolijohteet tehdään piistä leikatulle ohuelle kiekolle.Prosessoria ei rakenneta ilmaan vaan piirilevyn päälle

Tziizus mitä tulkintaa

Kyseessä oli ja on edelleen kahden moduulin ja IF kalvoston välinen muistiliikenne

miten helvatussa sen voi sekoittaa erillisiin ytimiin

Onko jotain lähdettä tälle luvulle?

Kyseessä oli ja on edelleen kahden moduulin ja IF kalvoston välinen muistiliikenne

Käytämme välttämättömiä evästeitä, jotta tämä sivusto toimisi, ja valinnaisia evästeitä käyttökokemuksesi parantamiseksi.