En minä lähtisi prosessoria valitsemaan yhden tai useammankaan pelimoottorin paremmuuden tai huonommuuden perusteella.

Eivät ne prosessorin erot ole merkittäviä 4K:lla pelatessa, vaan eroja saadaan lähinnä 1080p tai matalammilla resoluutioilla. Näytönohjaimella voi olla enemmän merkitystä, jos nyt tulevassa uudessa sukupolvessa niilläkään.

Ja tilanne saattaa olla prosessorin osalta sitten puolen vuoden tai vuoden päästä kallistunut toiseen suuntaan.

Valintaperusteeni olisivat mieluummin:

1. Pelisuorituskyky: Lähinnä riittääkö perusmalli vai pitääkö mennä huippumalleihin, ja onko muuta käyttöä kuin pelaaminen

2. Hinta (prosessori + emolevy +muistit): perusmalli, keskitaso vai huipputaso kohdan 1 ja 3 valinnoilla.

3. Alustan (emolevyn) ominaisuudet: liitännät - niiden määrät ja nopeudet, ja riittävätkö itselle ja mahdollisiin tulevaisuuden tarpeisiin

4. Jatkuvuus: pitääkö uudenpaan prosessorimalliin vaihtaessa päivittää alustaa (emolevy ja/tai muistit)

5. Haluaako hifistellä. Omasta kokemuksesta voin sanoa, että kalliiksi tulee!

Itse valitsisin:

- 7950X:n (tai säästövaihtoehtona 7700X)

- 32 tai 64GB DDR5 (5600/6000 tiukoilla latensseilla (28-32) jos on siihen varaa, tai vähän löysemmillä esim 36, jolloin pääsee 25-40% halvemmalla).

- Emolevy: PCIe gen5 (sekä 16x että M.2), eli sopiva B650E (tai X670E jos löytyisi järkevän hintainen). Näistä emoista ja niiden hinnoista vain on aika vähän tietoa vielä.

Olen siihen varautunut ainakin että seuraavat osat : virtalähde + kotelo + prossu + emo + muistit + windows käyttis Noi kaikki yhdessä tulee maksaan jotain 2200-3000€ maksimissaan. Muut osat on valmiina. Virtalähteenkin mielellään vaihdan kun näyttiksien lisävirtakaapelien standardi muuttumassa se PCI-ex 5.0 12 pinninen lisävirtaliitin.

Vastaan samoilla numeroilla, mitä luettelit tossa :

1. Mielellään ostais samantien n. 700-1200€ maksavan hyvän mallin eli paras tai toisiksparas, ettei heti tarvi olla päivittämässä taas uuteen "koneeseen".

2. Mitähän noi vois maksaa , ehkä n . 700-1200€(prossu) + 300-800€(emo) + 64Gt hyvää DDR 5 muistia maksaa 300-500€ = 1300€ - 2500€ yhteensä

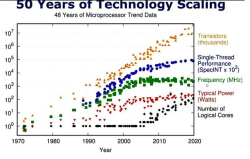

3. Emolevy on tärkeä osa, että siihen voi tulevaisuudessa päivittä osia. Haluisin ainakin PCI-express 5.0 väylän näyttikseen ja ainakin yhden kovopaikan, jossa on PCI-ex 5.0 väylä. Nopeammalla väylällä saa viimsetkin prosentit pelikäyttöön puristettua kokonpanosta irti. (vaikutus ehkä 1%....3% yleensä) ,mutta jos uuden koneen kasaa, niin ei sitä viittis enää vanhalla tekniikalla lähtee kasaan kts. :

AMD Radeon RX 6500 XT PCI-Express Scaling

The AMD Radeon RX 6500 XT comes with only a narrow PCI-Express x4 interface. In this article, we took a closer look at how performance is affected when running at PCI-Express 3.0; also included is a full set of data for the academically interesting setting of PCI-Express 2.0.

5. Hifistelen niissä osissa, missä on se on järkevää. Emolevyyn ei kannata laittaa liikaa rahaa. Voihan myös olla että jokin muu prossumalli kuin paras tai toisiks paras on parempi valinta, en osaa sanoa vielä. Mutta tässä tullaan taas siihen, että jos tingin liikaa hinta laatusuhteesta, sit taas joutuu pian jo ostaan uuden koneen. Mielummin ostas kerralla kunnollisen et pärjää taas useamman vuoden. Tulee pitkässä juoksussa "halvemmaksi" Tai no ehkä helpompaa kun ei kokoajan tarvi vaihtaa.

Viimeksi muokattu: