Vastaus osa 2:

Tuo tyyppi siis jatkuvasti sekoittaa keskenään

A) varmistettua faktaa

B) virheellisiä väitteitä

C) yleisesti monessa paikassa ääneen lauottuja spekulaatiota, joiden toteutumista voidaan pitää todennäköisenä, muttei varmoina

D) omia spekulaatioitaan

Eikä mitenkään selvästi erottele näitä keskenään

Sitten itse asiaan

n. kohta 9:30

Spekulaatio siitä että 4400G olisi 8/16 ydintä/säiettä on aivan järjetön, kun 4600H on 6/12 ydintä/säiettä.

Myös spekulaatio siitä että 4800X olisi 12 ydintä on ei mielestäni vaikuta kovin todennäköisesti toteutuvalta, kahden piilastun malli on paljon kalliipi valmistaa kuin yhden, ja kun 4900 H on kuitenkin 8/16. Ei kuitenkaan mahdoton ole.

Tyyppi on siis vetänyt hihasta/typeristä/virheellisistä perusteluista hirveästi malleja ja ydinmääriä ja hintoja mutta kaikki on vaan virheellisiin oletuksiin ja huonoihin pohjatietoihin perustuvaa spekulaatiota. Ja sotkee samaan taulukkoon hienosti sekaisin todellisia speksejä, virheellisiä speksejä julkaistuista tuotteista, sekä omaa spekulaatiotaan, eikä mitenkään selvästi erottele, mikä on mitäin.

n. kohta 14:32 sotkee IPCtä ja valmistustekniikkaa keskenään. höpöhöpö. Selitin jo edellsiessä viestissäni.

n. 16:03 on ihan täyttä paskaa:

1) "Matissa & renoir desktop are increasing core counts". fakta: Mitään useampiytimisiä desktop-renoireja ei vielä ole julkaistu, ja ensimmäiset oikeat vuodot desktop-renoireista on 4 ydintä, 8 säiettä, eli ei yhtään enempää kuin vanhoissa malleissa.

On mahdollista, että >4-ytimisiä desktop-renoireja JOSKUS tulee, mutta melko varmasti ei nimellä 4400G, ei niillä spekseillä ja hinnoilla mitä tuon pellen taulukoissa lukee.

2) Puhuu varmana "zen2 level IPC increase" zen3lle. Tosiasiassa zen3n IPCstä ei ole mitään

varmoja tietoja. Kaikki jutut zen3n ipc-parannuksista on spekulaatiota joka ei perustu mihinkään tekniseen vaan on pelkkää arvelua sen perusteella että

yleensä uusien mikroarkkitehtuurien myötä ipc paranee.

Se, että zen3n ipc paranee jonkin verran on

todennäköistä, mutta ei varmaa. Se, että se paranee yleisesti 15% - sitä en pidä enää niin todennäköisenä. Oma arvioni menisi lähemmäs 10%ia.

3) "comet could be 20+% behind zen 3in ipc".

Ei todellakaan.

Zen2 ja Comet lake on keskimäärin melko tasoissa ja zen3 ei todellakaan tule parantamaan >25%ia (mitä sen tarvisi parantaa jotta tämä väite pitäisi paikkaansa) Menee nyt ihan naurettaviksi nämä väitteet.

16:45

Vetää hihasta noita IPC-parannuksia, ja nyt

käyttää perusteena zen3-parannusta josta ei ole mitään oikeaa faktaa olemassa.

Spekuloidaan ensin yksi luku ja sitten käytetään sitä lukua perusteluna spekulaatioon toisesta luvusta

Lisäksi, todellisuudessa homma menee näiden IPC parannusten ennustusten suhteen juuri toisinpäin; Menneiden IPC-parannusten perusteella ei kannata ennustaa tulevaa positiivisella kertoimella; IPCn parantaminen on hyvin vaikeaa, kun softissa vaan ei ole käskytason rinnakkaisuutta paljon. Käytännössä lähestytään asymptoottisesti sitä maksimia minkä softat mahdollistaa.

Se, että nyt saadaan jostain sitä IPCtä taiottua lisää tarkoittaa, että se keino sen IPCn parantamiseksi on jo käytetty.

Zen pystyi parantamaan IPCtä paljon excavatoriin nähden

koska exvacatorin ipc oli niin onneton.

Ja zen2 pystyi parantamaan niin paljon zeniin nähden, koska

1) zen, vaikka paransi paljon excavatoriin nähden, suunniteltiin kiireessä ja paljon jo tiedossa olevia parannuksia piti jättää toteuttamatta. Zenissä oli edelleen löysiä jäljellä, kiireen takia.

2) zen2 tuhlasi hirveän määrän transistoreja todella isoihin l3-kakkuihin. (ei päde renoiriin)

Pitää keksiä uusia, entistä monimutkaisempia temppuja, jotta sitä IPCtä saadaan jälleen tämän jälkeen parannettua. Zen2ssä on paljon vähemmän löysiä joita zen3 voisi parantaa.

Yhdelle säikeelle käytettävissä olevan L3-kakun määrä tullee toki zen3ssa kasvamaan, mutta samalla sen L3n viive tulee kasvamaan selvästi.

Tuo spekuloi että zen4ssta tulisi suurempi L2-kakku. Mikäli verrataan zen2een, niin tästä olen vihdoin tuon kanssa samaa mieltä. Tosin se voisi olla järkeä kasvattaa jo zen3ssa (koska L3-viive kasvaa), mutta voi olla että "7nm"llä ei ole varaa siihen, vaan tämä jätetään zen4lle jonka uudella valmistustekniikalla tähän on paremmin varaa.

"20-32 cores on desktop".

En pidä todennäköisenä alle tonnin hintaluokassa, kahden muistikanavan kannoilla. Alempana tästä lisää

17:04 Mainitaan AVX-512 zen4lle. Vihdoin sanottu jotain järkevää. Viimeistään zen4ssa tullee AVX-512.

Sen sijaan "7nm" IO-piiriä pidän epätodennäköisenä. Tämä taas vaikuttaa vähän siltä että heitellään numeroita ymmärtämättä niitä; TSMCn nykyinen "7nm" prosessi on pinta-alaa kohden fundamentaalisesti kalliimpi kuin GFn 12/14 nm prosessi, koska se vaatii moninkertaisemman multipatternoinnin, kaiken valmistaminen sillä on vaan hitaampaa, samassa ajassa saadaan samankokoiselta linjalta vähemmän valmista piipinta-alaa ulos. GFn uusi EUV (7+) taas vaatii uuden litografiakaluston joka halutaan siirtää tuottamaan pienemmällä "5nm" prosessilla pian, ja kun "5nm" on vauhdissa, ei EUV-7+ tule halpenemaan markkinateknisistä/kysynnän ja tarjonnan lakiin liittyvistä syistä.

Isot IO-transistorit on siis kalliimpia valmistaa "7nm" tekniikalla kuin "12/14" nm tekniikalla. Lisäksi AMDn ja GFn sopimus loppuu vasta 2024, joten AMDn on järkevää valmistaa IO-piirejään GFn vanhoilla tekniikoilla. "7nm" IO-piiri oikeastaan yhdistäisi huonot puolet chiplet-rakentaan ja moniliittipiirin kanssa, kun IO-piirillä ei saataisi riittävästi säästöjä vanhan valmsitustekniikan käytöstä mutta silti olisi kaksi eri piilastua, ja niiden välinen kommunikaatio-overhead ja paketoinnin kalliimpi hinta jne.

En kuitenkaan pidä täysin mahdottomana.

17:30. "AMD exclusive N5P node " .. Jätkä on TÄYSIN pihalla siitä miten Intelin ja TSMCn valmistustekniikat vertautuu toisiinsa. Lisäksi höppöttää yhdestä "20% paremmasta" luvusta ilman mitään konkretiaa, mitä sillä on tarkoittavinaan. EI valmistustekniikoita mitata millään yhdellä "tämä on x% parempi kuin tuo" luvulla. Joku on parempi matalilla jännitteillä matalillakelloilla, toinen parempi kellottumaan suurella jännitteellä , joku mahdollistaa pienemmät vuotovirrat, joku mahdollistaa pienemmän SRAMin, toinen mahdollistaa pienemmän yleisen logiikan jne.

Hyvä esimerkki on se, että tällä hetkellä TSMCn "7nm" on matalilla ja keskimääräisillä kelloilla n. 2x energiatehokkaampi kuin intelin "14+++"-prosessi, mutta suurella jännitteellä, suurella virrankulutuksella Intelin "14+++" mahdollistaa silti suuremmat maksikellotaajuudet (zen2n ja comet laken liukuhihnan vaiheiden pituudet on aika samaa luokkaa, niiden pitäisi samallta valmistustekniikalla kellotua aika samoihin luokkiin)

(Täälläkin jotkut vuosi sitten jotkut hypetti kuinka zen2 tulee kellottumaan vähintään jonnekin 5 GHz kun ei ymmärretty sitä, että maksimikellot on ihan eri asia kuin kellotaajuus jossain selvästi virrankulutus-/lämpörajoiteisessa tilanteessa, ja näistä energiatehokkuusparannusluvuista yritettiin ekstrapoloida maksimikellotaajuusparannuksia)

Rocket lakessa on melko varmasti suurempi ipc kuin zen3lla; Kuten jo edellisessä viestissäni selitin, vanhempi valmistustekniikka ei huononna IPCtä. ja Sunny cove on jo huomattavasti zen2sta edellä ja zen 3 tulee todennäköisesti pääsemään ipcssä keskimäärin lähelle sunny covea muttei sen ohi. Willow Cove taas todennäköisesti parantamaan jonkin verran Sunny Coveen nähden.

Intel tulee todennäköisesti olemaan hiukan edellä yhden säikeen suorituskyvysssä, mutta zen3 tulee olemaan niin paljon energiatehokkaampi että monen säikeen suorituskyvyssä AMD tulee olemaan todella paljon edellä kun ytimiä voi olla enemmän ja monen ytimen kuormituksessa ne voivat käydä paljon suuremmilla kelloilla ilman että lämmöntuotto tai virrrankulutus tulee ongelmaksi.

AMDllä ei todennäköisesti tule olemaan pitkiin aikoihin mitään 20-ytimisiä 2-kanavaiseen kuluttajakantaan meneviä prosessoreita.

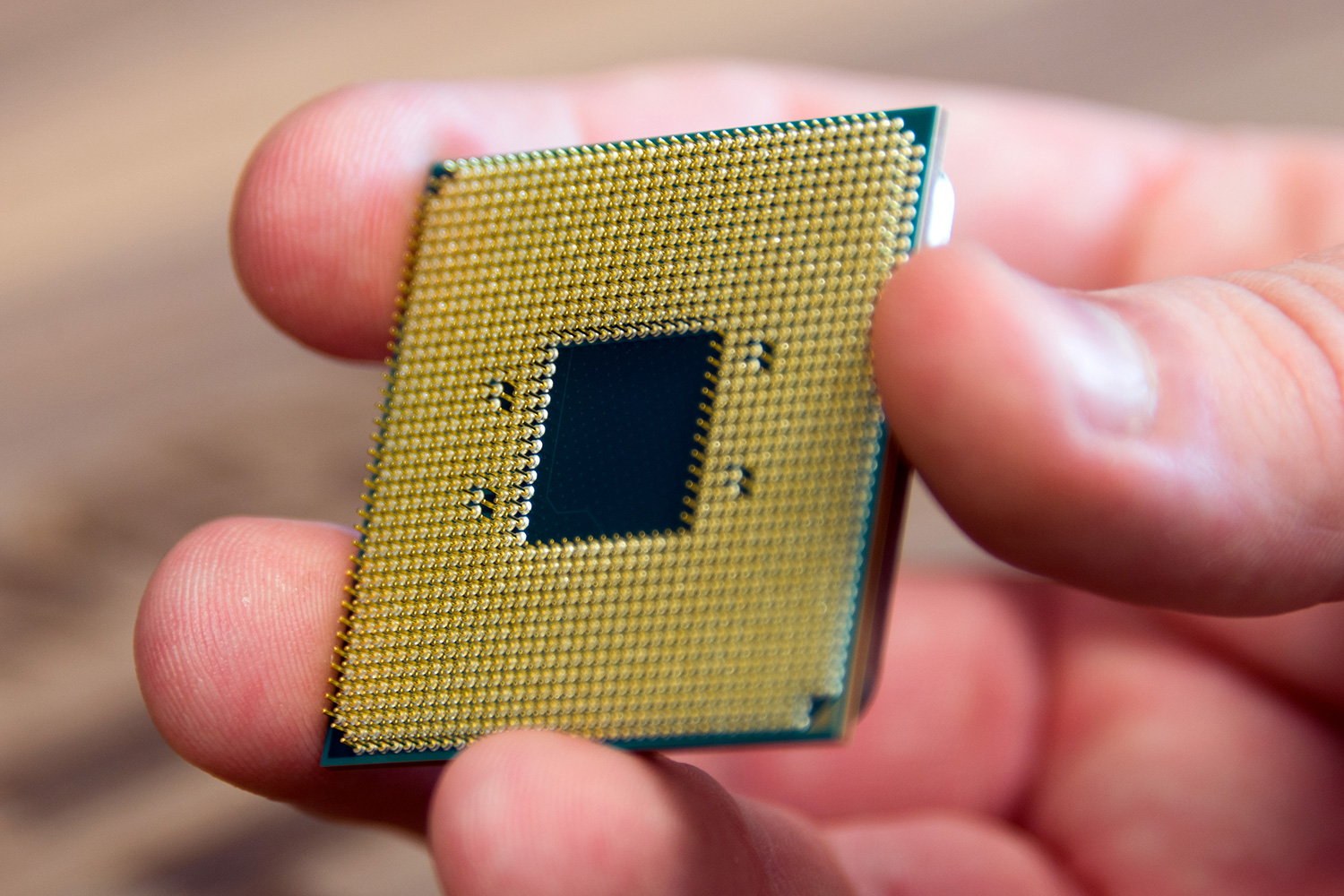

Zen3-CCX ja Zen3-CCD on 8 ydintä. Normaalit kuluttajamallit yhdellä CCXllä, yhdellä CCDllä, kalleimmat mallit kahdella.

20 ydintä tarkoittaisi joko montaa CCXää (ja samalla CCDtä) tai CCXn suurentamista entisestään, TAI kahden CCXn CCDtä. Mikään ei mielestäni ole kovin todennäköistä zen4een. CCXn suurentaminen tarkoittaa lisäksi aina suurempaa L3-viivettä

Todennäköisesti ei ole sanonut tarkkaanottaen niin, vaan tyyppi muistaa väärin/omiaan. On tainnut sanoa jotain vähän sinnepäin, tyyliin että "ydinmääriä tullaan kasvattamaan" ja että "ydinmääriä ollaan vähintään jossain tuotteissa kasvatettu joka sukupolvi viimeiset pari vuotta" muttei ehkä että niitä kasvatetaan

joka sukupolvi tulevaisuudessakin.

64-ytiminen EPYC ja Threadripper on jo ongelmissa windowsin schedulerin kanssa, kun windowsin scheduler ei tue kunnolla yli 64 rautasäiettä, vaan 128 rautasäikeen prosessoreilla kaikki pitää keinotekoisesti jakaa kahteen "säieryhmään", ja tästä koitui vaikka mitä häsläystä, purkkaa ja myös hidastumista softille jotka haluaa käyttää koko prosessirin laskentakapsiteettia. Ja tämä on aika syvällä tietyissä windowsin rajapinnoissa, en odottaisi tähän päivitystä kovin nopeaan tahtiin.

128 ytimellä, 256 säikeellä tarvisi sitten neljä säieryhmää ja yksi softa saisi melko helpolla käyttöönsä maksimissaan vain neljäsosan koko prosessorin laskentakapsiteetista.

Linuxilla ei toki mitään tällaisia ongelmia ole, se tukee hyvin suuria ydinmääriä.

Intelin "7nm" prosessi tulee olemaan vähintään yhtä kehittynyt kuin TSMCn "5nm" prosessi, Intel ei tarvi mitään "5nm" prosessia päästäkseen tasoihin.

TSMCn "5nm" prosessi on tiheydeltän (SRAM-solun koko) vain n. 1.5 kertaa tiheämpi kuin Intelin "10nm" prosessi, ja

wikichipin arvioiden mukaan Intelin "7nm" prosessi tulee olemaan n. 1.35 kertaa tiheämpi kuin TSMCn "5nm" prosessi:

The 5 nanometer (5 nm) lithography process is a technology node semiconductor manufacturing process following the 7 nm process node. Commercial integrated circuit manufacturing using 5 nm process is set to begin sometime around 2020.

en.wikichip.org

Kyseessä on yhden henkilön TULKINTA siitä mitä messuilla (kuulemma) sanottiin.

Kyseessä on yhden henkilön TULKINTA siitä mitä messuilla (kuulemma) sanottiin.