Miten vertaisit l3 ja l4 välimuisteja? L4 on kuitenkin hitaampaa jolloin vaikka se onkin nopeampi, kuin DRAM, niin missä määrin se että on hitaampi kuin l3 vaikuttaa ja vähän jos avaisit v-cachen ja l4 välimuisti muistiohjainpiirillä mahdollisia eroja ja miksi amd siirtyisi v-cachesta l4 cacheen?

L3 ja L4 ei ota kantaa siihen, miten ne on toteutettu, ne on vaan että monennestako välimuistitasosta on kyse, kun lasketaan yhimen suunnasta.

Esim CPUissa Intelin ja AMDn L3-välimuistit on jo melko erilaisia, Intelillä L3 on kaikille ytimille yhteisiä, hitaamman kytkentäverkon takana, kun taas AMDllä pieni määrä ytimiä(CCX) jakaa L3-välimuistin keskenään mutta CCXiä voi koko piirillä olla useita.

Käytännössä kaikki välimuistitasot on nykyään SRAMia ja ulompien tasojen hitaampi nopeus tulee käytännössä muutamasta eri asiasta:

1) Haku ulomman tason välimuistista aloitetaan vasta kun selviää, että sisemmän tasin välimuisti ei osunut. Ei ulomman välimuistitason kokonaisviiveessä on aina mukana kaikkien sisempien tasojen välimuistien viiveet

2) Isommille, kauempana ytimestä oleville välimuisteille tarvitaan pidemmät johdot

3) Välimuisti, joka palvelee useampaa ydintä tai useampaa sisemmän tason välimuistia tarvii monimutkaisemman (hitaamman) kytkentäverkon

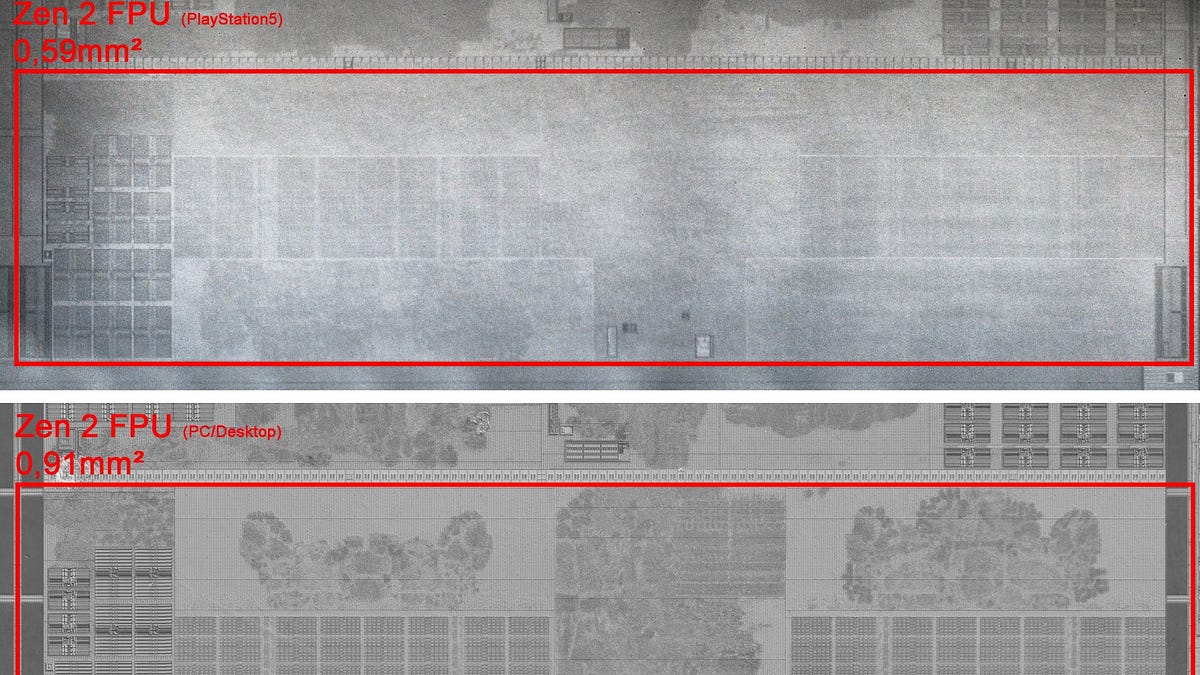

4) Uloimmat tason välimuistit tyypillisesti tehdään tiheys- ja tehonkulutusoptimoiduista SRAM-soluista, sisemmän tason välimuistit tyypillisesti tehdään nopeusoptinoiduista SRAM-soluista

Viime vuosikymmenellä muutamassa piirissä oli eDRAM-pohjaisia L4-välimuisteja, nykyään eDRAM on kuitenkin kuollut.

Mikäli L4 tulee muistinohjainpiilastulle, siinä on lisäviiveenä vielä piilastujen välisen linkin viive, mutta se on silti todella paljon nopeampaa kuin normaali omalla DRAM-valmistustekniikalla valmistettu DRAM, normaali DRAM on vaan viiveiltään nykyään aina todella hidasta.