- Liittynyt

- 05.11.2020

- Viestejä

- 312

Et sit edes viitsinyt noita juttuja kattoa mihin viittasin aikaisemmin. Hieno homma.

In a call with AMD, we have confirmed the following:AnandTech Forums: Technology, Hardware, Software, and Deals

Seeking answers? Join the AnandTech community: where nearly half-a-million members share solutions and discuss the latest tech.www.anandtech.com

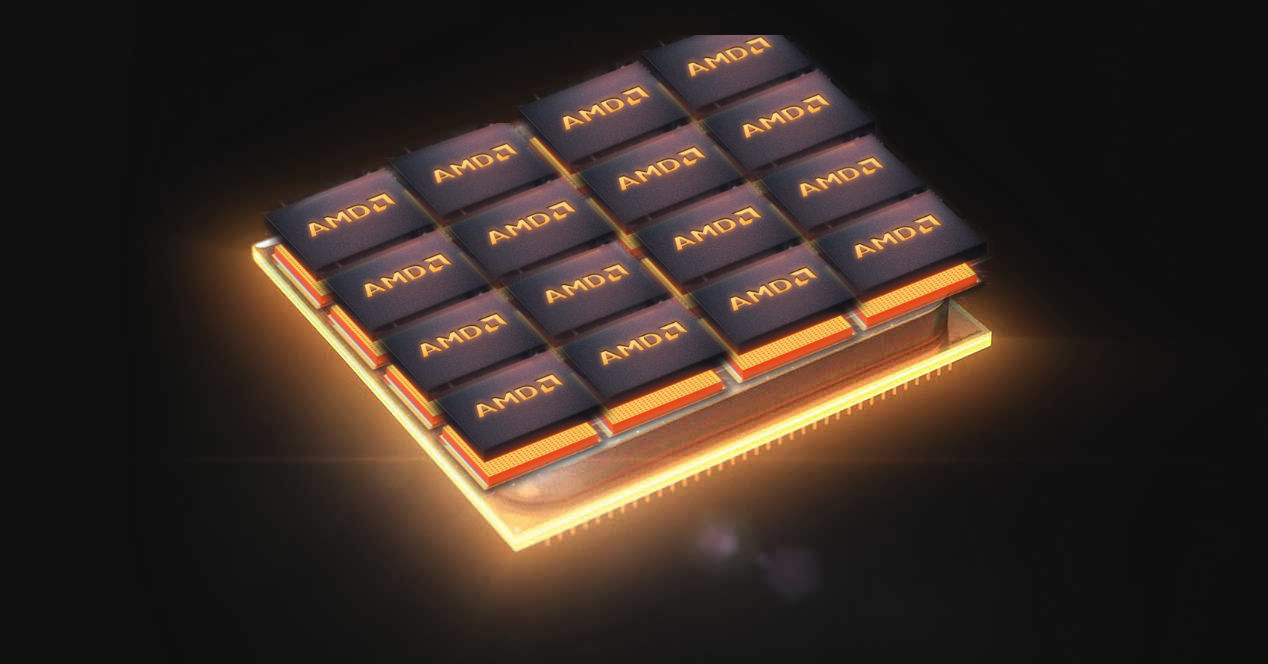

This technology will be productized with 7nm Zen 3-based Ryzen processors. Nothing was said about EPYC.

Those processors will start production at the end of the year. No comment on availability, although Q1 2022 would fit into AMD's regular cadence.

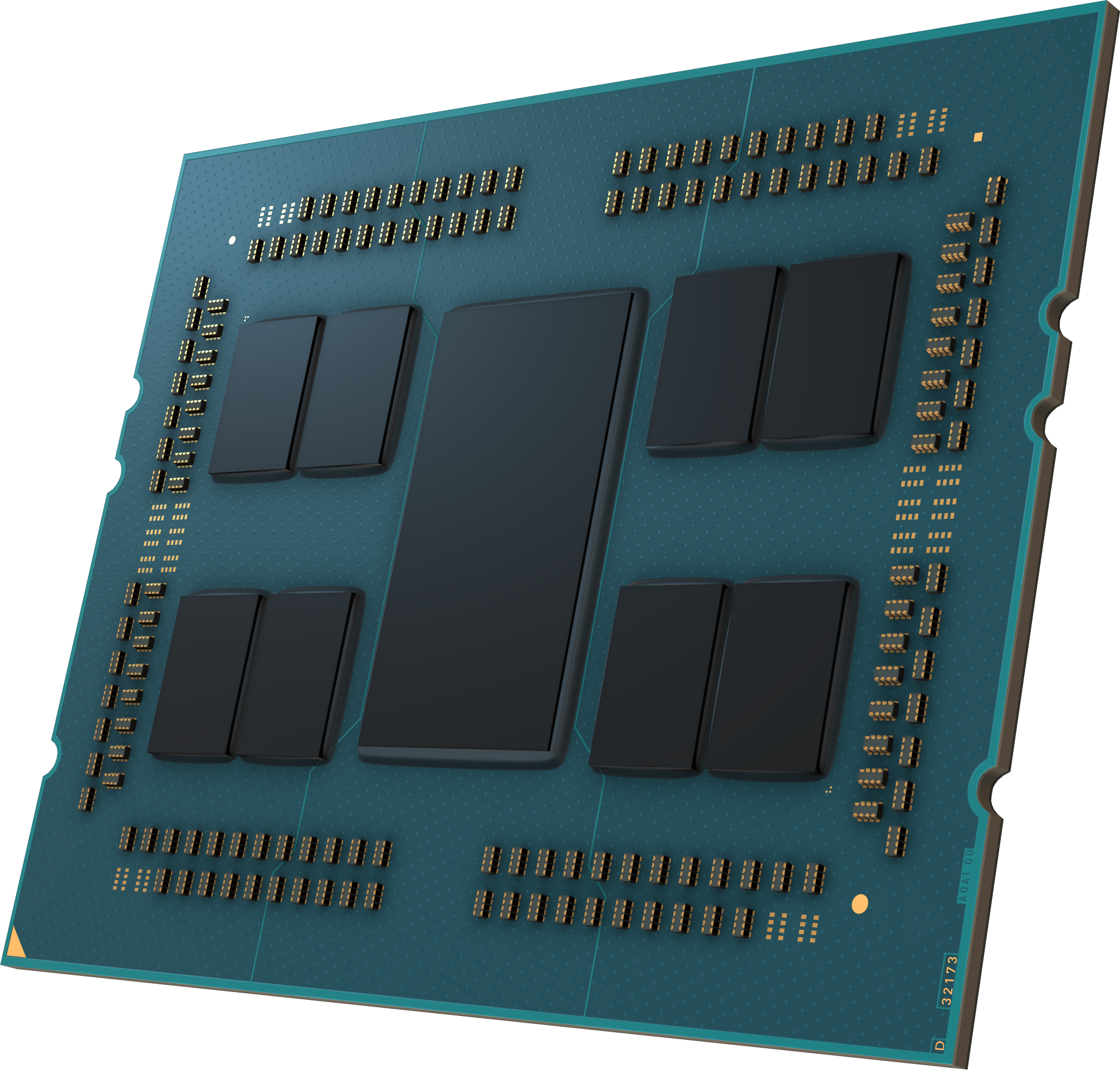

This V-Cache chiplet is 64 MB of additional L3, with no stepped penalty on latency. The V-Cache is address striped with the normal L3 and can be powered down when not in use. The V-Cache sits on the same power plane as the regular L3.

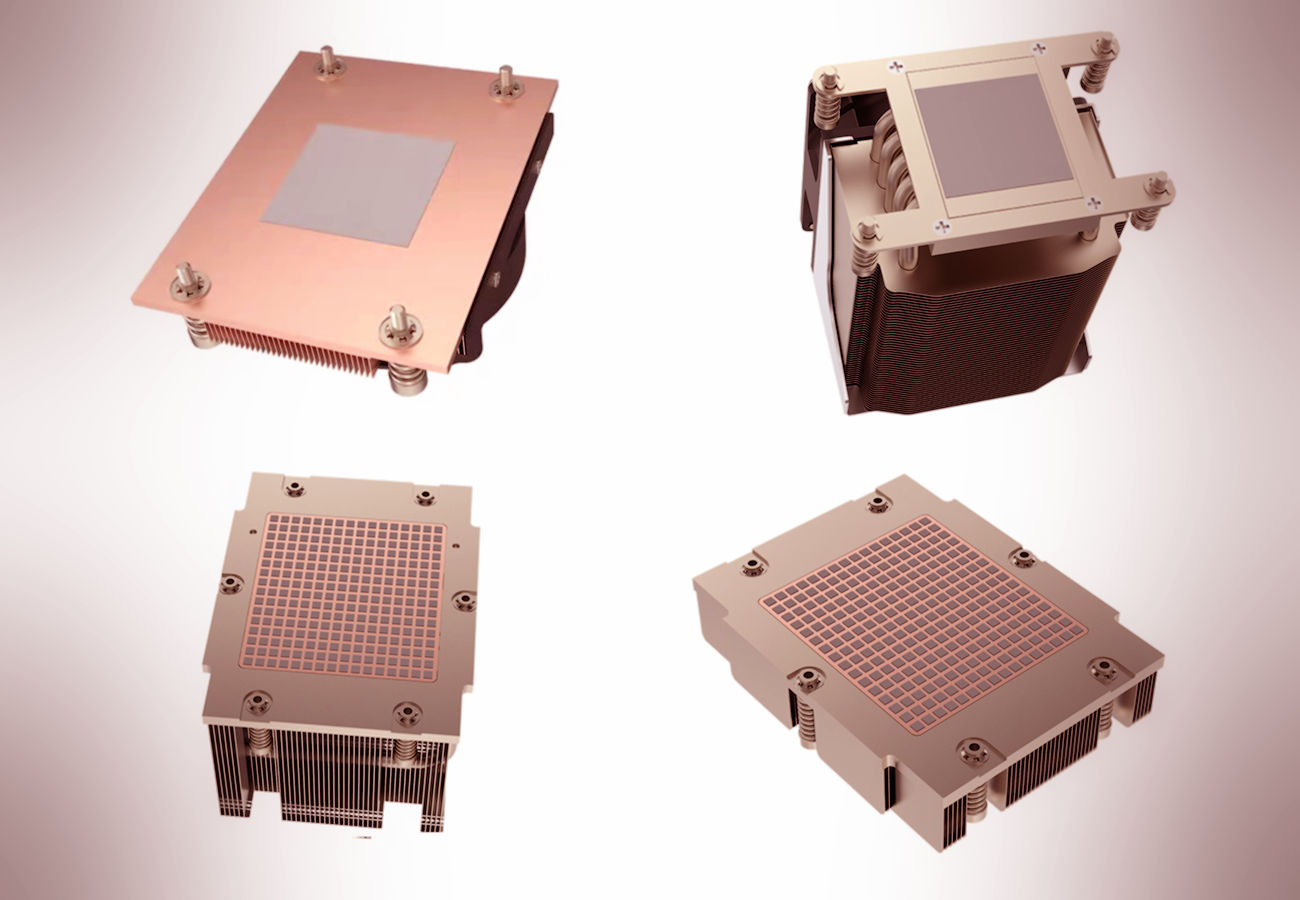

The processor with V-Cache is the same z-height as current Zen 3 products - both the core chiplet and the V-Cache are thinned to have an equal z-height as the IOD die for seamless integration

As the V-Cache is built over the L3 cache on the main CCX, it doesn't sit over any of the hotspots created by the cores and so thermal considerations are less of an issue. The support silicon above the cores is designed to be thermally efficient.

The V-Cache is a single 64 MB die, and is relatively denser than the normal L3 because it uses SRAM-optimized libraries of TSMC's 7nm process, AMD knows that TSMC can do multiple stacked dies, however AMD is only talking about a 1-High stack at this time which it will bring to market.

Niin, siis viittasit jossain lähes 3kk vanhassa viestissä?

Tuota ei mistään AMD:n omasta materiaalista suoraan saanut selville.

Hyvä kuitenkin että jollekin taholle on asia selitetty jossain ymmärrettävässä muodossa.

Tällä toteutuksella ainut mahdollinen heikennys tuohon lämmön siirtymiseen prosessoriytimistä liittyy sitten tuohon "fillerin" bondaukseen. Tuskin merkittävää vaikutusta, mihinkään.

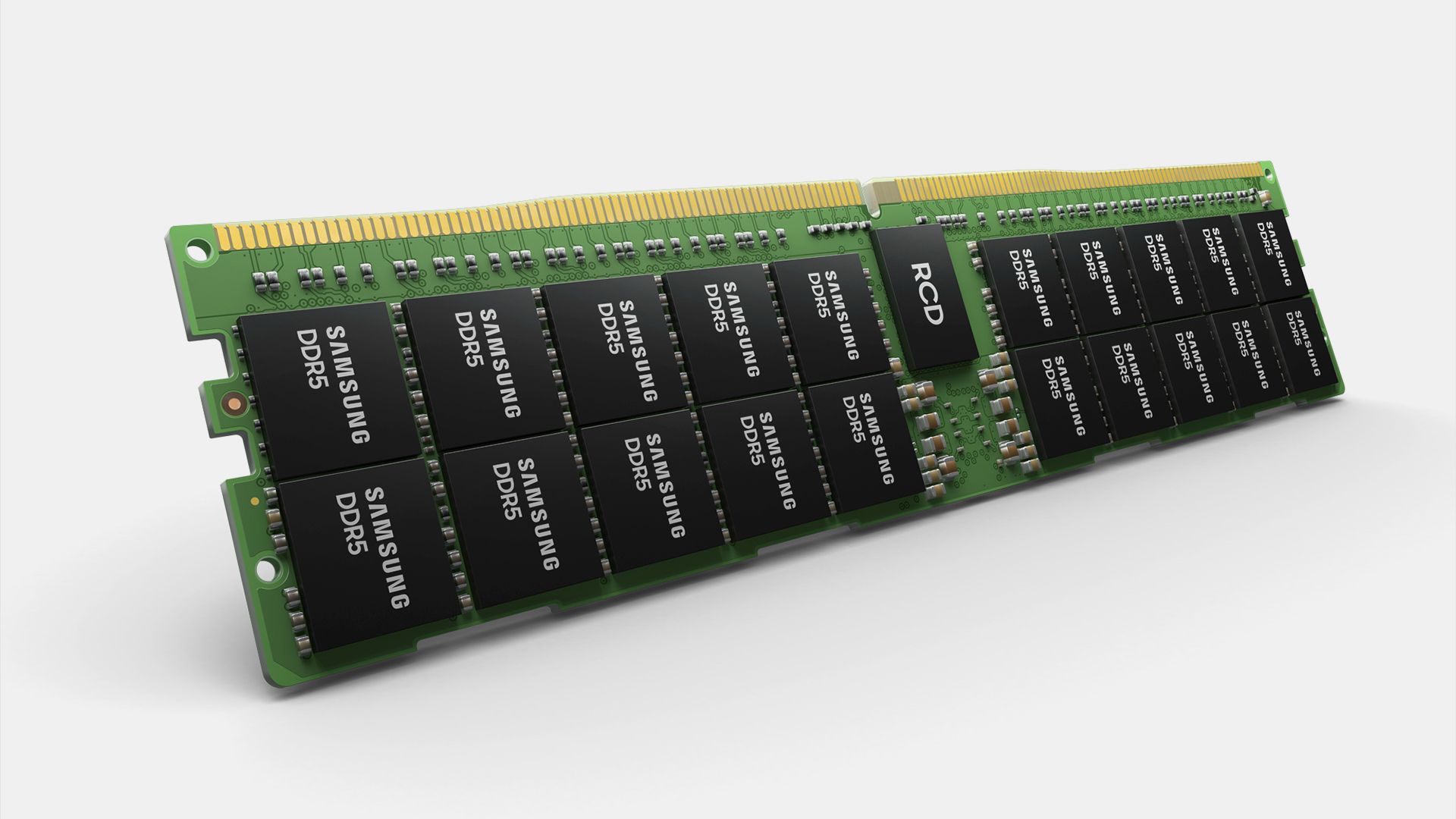

L3:n lämmöt tulevat tuon ylimääräisen välimuistin oman lämmöntuoton johdosta varmasti hieman nousemaan, mutta sekään ei varmasti ole mikään ongelma. Vermeerin 32MB L3:n vie 3.6GHz kelloilla about 3.6W tehoa

ja sen lämmöt on keskimäärin 40-50°C ytimen rasituslämpöjä alhaisemmat.

Lähdettä ei juuri nyt ole tuolle ylläolevalle tietysti antaa (eikä tule olemaankaan), joten merkataan paskapuheeksi.