- Liittynyt

- 21.06.2017

- Viestejä

- 7 327

TSMC ei pysty lupaamaan yhtään mitään sellaista mikä olisi AMDlle riskien arvoista, eikä TSMCn myöskään olisi mitään järkeä alkaa lupaamaan mitään kuuta taivaalta, niillä kyllä riittää "5nm" tekniikalleen asiakkaita mobiili-SoC-puolelta ihan tarpeeksi, piireissä joilla uudessa valmistustekniikassa on paljon enemmän järkeä.

Mitä nyt huawei ilmeisesti tippumassa pakotteiden takia pois, taisi jossain olla juttua että huihai on TSMC:n toiseksi suurin asiakas.

Servereihin huonommin kellottuvat piirit menisi ongelmitta.

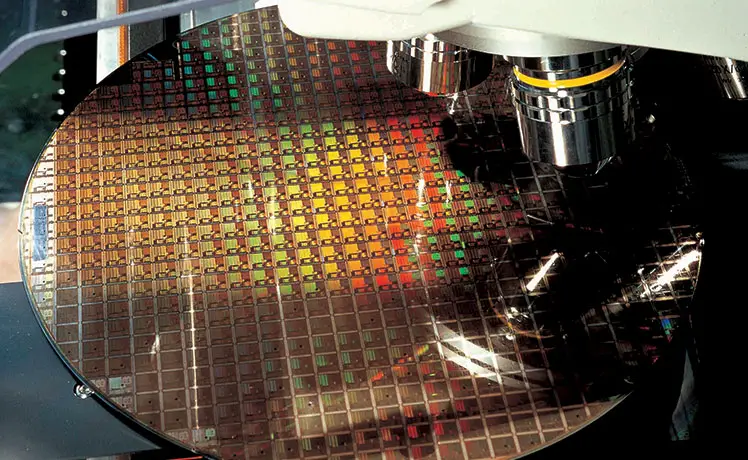

Early TSMC 5nm Test Chip Yields 80%, HVM Coming in H1 2020

Kuten tuossakin hiukan vihjaillaan niin joku Zen 2 chipletti olisi kokonsa puolesta aika houkuttelva tuohon alkutuotantoon, mutta jos performance kirjastoja tarttee niin sitten ei välttämättä. Eikös tommonen chipletti ole kuitenkin joka yksinkertaisempi rakenteeltaan kuin highend mobiili SoC? Ne alkaa olla jo aika monimutkaisia härveleitä ja eivät edes mitään erityisen pieniä kun vertaa Zen chipletteihin.

5nm ollu riskituotannossa jo puolisen vuotta ainakin kun lasketaan tuon artikkelin kirjoitus hetkestä ja näillä näppylöillä ollaan siirtymässä varsinaiseen tuotantoon. Eiköhän tässä kuukausien aikana ole saannotkin parantunut.

This process is going to be the next step for any customer currently on the N7 or N7P processes as it shares a number design rules between the two.

En sitten tiedä että miten paljon tuo merkkaa mutta luulisin että säästää aikaa jonkin verran.

Mutta pelkkää spekulointiahan tämä kaikki on, ei tätä tartte niin vakavasti ottaa