Ei.

Ensinnäkin, esim. TSMCn "7+" ja "5nm" prosessien EUV-litografia verrattuna aiempiin prosesseihin tarkoittaa aivan eri periaatteita sille, miten se valo generoidaan/ohjataan; EUVissa ei ole kyse pelkästään aallonpituuden pienentämisestä. En kutsuisi tätä pelkäksi "hifistelyksi".

Mutta toki kaikki on silti edelleen litografiaa, sillä hyvin korkealla tasolla "perusperiaate" on aivan sama. Mutta tämä vähän sama kuin että väitettäisiin, että mopo ja rekka-auto ovat vaan iteraatioita toisistaan koska molemmat liikkuvat pyörillä ja toimivat polttomoottorilla, "samalla perusperiaatteella".

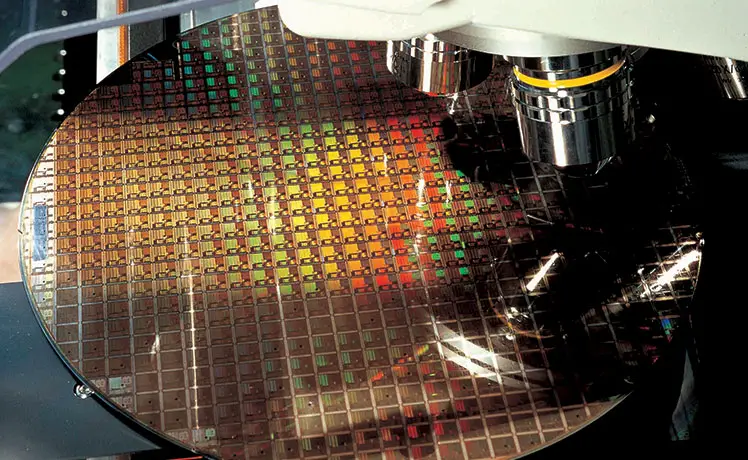

Toisekseen, GFn "14nm" ja "12nm" prosesseilla oli aivan samat oleelliset mitat (MMP ja CCP). Niiden välillä ei matalalla tasolla pienennetty yhtään mitään

siellä on vaan

1) (mitään pienentämättä) jotain pientä viilausta jossain jonka takia suorituskyky inasen parempi (yleensä/aiemmin tällaisen takia ei aleta/alettu kutsumaan prosessia pienemmällä numerolla, esim. intel lisää tällaisista vaan plussia prosessin nimen perään)

2) Samoihin aikoihin kun tehtiin tämä pieni optimointi, tuotiin uudet koko-optimoidut (ei suorituskyky-optimoidut) standardikirjastot joilla sai niitä käyttävän logiikan tiheämpään (ja joita ei käsittääkseni zen+ssa käytetty). En näe mitään varsinaista estettä sille, että näitä olisi voitu tuoda jo ilman niitä viilauksia mitä itse valmistusprosessiin tehtiin, tämä vaan bundlattiin sen valmistusprosessin pikkuviilauksen kylkeen ja markkinointi keksi että "kutsutaanpas sitä pienemmällä numerolla". Mutu: Voi toki olla, että ilman niitä valmistusprosessin pikkuviilauksia näiden pienempien standardikirjastojen suorituskyky olisi ollut sen verran huono, että harva olisi niitä halunnut käyttää.

wccftech.com

Zen 3 olisi TSMC:n N7P-prosessilla valmistettu. N7+ olisi vielä pykälää parempi 7 nm prosessi.

wccftech.com

Zen 3 olisi TSMC:n N7P-prosessilla valmistettu. N7+ olisi vielä pykälää parempi 7 nm prosessi.