finWeazel

Tukijäsen

- Liittynyt

- 15.12.2019

- Viestejä

- 14 074

AI puolen piiripulaan ja chipletteihin liittyen uutista. Nvidialla on piirejä tarpeeksi, mutta piirien paketointi on pullonkaula. Jos/Kun RDNA4 highend oli useampi compute piiri yhteen paketoituna niin tämä uutinen voi selittää highendin perumisen. AMD käyttää ostamansa kapasiteetin paremman marginaalin konesalipiireihin pelipiirien sijaan?

lähde: NVIDIA: GPU Supply Issues Involve Packaging, Not Chip Wafers

According to Boyle, the problem doesn't come from Nvidia miscalculating demand or wafer yield issues at its manufacturing partner, TSMC.

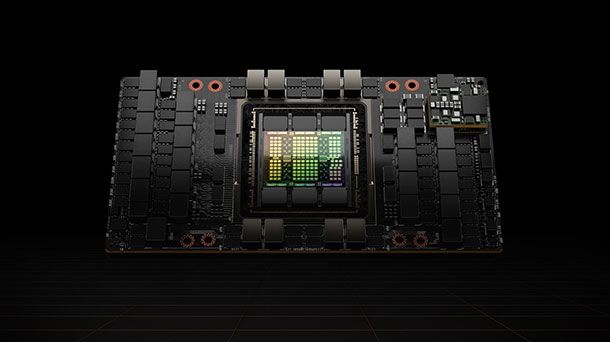

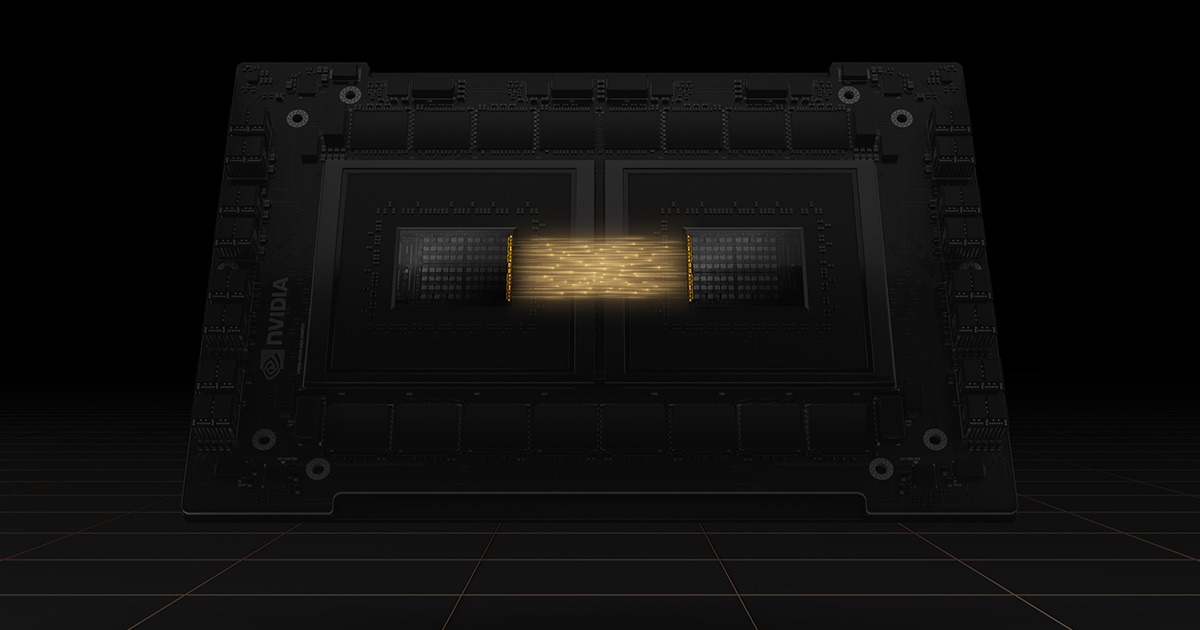

Instead, the bottleneck in manufacturing enough GPUs that can cater to both consumer and professional workloads (looking at you, AI boom) lies with the chip packaging steps that come after. Nvidia's H-class GPUs make use of TSMC's 2.5D Chip-on-Wafer-on-Substrate (CoWoS) packaging technology, a multi-step, high-precision engineering step whose complexity slows down the number of GPUs that can be assembled in a given timeframe. This can disproportionately impact supply; the delta between the number of GPUs required and those available

CoWoS bottleneck issue may be more severe than expected. TSMC itself has said that it expects it to take 1.5 years (and the completion of additional fabs and expansion of already-existing facilities) to bring the packaging process backlog back in line. This likely means that Nvidia will have to decide on what packaging capacity to allocate to which products - there's not enough time and capacity to package them all.

lähde: NVIDIA: GPU Supply Issues Involve Packaging, Not Chip Wafers

Viimeksi muokattu: