Grafiikkapuolella uskon kyllä, että Apple menee HBM2-muisteihin. Mahtaisikohan se toimia prosessorinkin kanssa? Olisi ainakin lopputuotteen yksinkertaisuuden kannalta hyväksi, kun olisi vain yhtä muistityyppiä ja yhteinen muistiavaruus.Uudet huhut bloombergin mukaan sanovat, että Apple olisi työstämässä 2021 loppuun mennessä 16 performance coren mobiiliprosessoria Macbook Prohon ja iMac-linjaan ja 32 coren versiota Mac Prohon. Ja vastaavasti nostaa GPU-corejen määrä 64-128:aan tehokäyttöä varten. M1:ssä GPU-coreja taitaa olla 8.

Jos huhussa on mitään perää, tulee Applelle kyllä melkoisen mielenkiintoisia muistikaistahaasteita, jo nykyinen 128-bittisen kanavan LPDDR4X on M1:n tehokäytöllä täysin tukossa - prosessori lienee suunniteltu muistiväylän ympärille maksimoiden käyttö. Lienee melkoisen hyvä kysymys, että millä suhteellisen virtapihillä tavalla saataisiin kaista vielä nelinkertaistettua ensin 16 coren versioon ja siitä vielä vielä ylöspäin työpöytämalleihin.

Jos muistikaista pidetään tarpeeksi leveänä, tuollaiset prosessorit taitaa jättää jälkeensä ihan kaiken mitä x86-raudalle saa kaupasta.

-

PikanavigaatioAjankohtaista io-tech.fi uutiset Uutisia lyhyesti Muu uutiskeskustelu io-tech.fi artikkelit io-techin Youtube-videot Palaute, tiedotukset ja arvonnat

Tietotekniikka Prosessorit, ylikellotus, emolevyt ja muistit Näytönohjaimet Tallennus Kotelot ja virtalähteet Jäähdytys Konepaketit Kannettavat tietokoneet Buildit, setupit, kotelomodifikaatiot & DIY Oheislaitteet ja muut PC-komponentit

Tekniikkakeskustelut Ongelmat Yleinen rautakeskustelu Älypuhelimet, tabletit, älykellot ja muu mobiili Viihde-elektroniikka, audio ja kamerat Elektroniikka, rakentelu ja muut DIY-projektit Internet, tietoliikenne ja tietoturva Käyttäjien omat tuotetestit

Softakeskustelut Pelit, PC-pelaaminen ja pelikonsolit Ohjelmointi, pelikehitys ja muu sovelluskehitys Yleinen ohjelmistokeskustelu Testiohjelmat ja -tulokset

Muut keskustelut Autot ja liikenne Urheilu TV- & nettisarjat, elokuvat ja musiikki Ruoka & juoma Koti ja asuminen Yleistä keskustelua Politiikka ja yhteiskunta Hyvät tarjoukset Tekniikkatarjoukset Pelitarjoukset Ruoka- ja taloustarviketarjoukset Muut tarjoukset

Kauppa-alue

Navigation

Install the app

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Huomio: This feature may not be available in some browsers.

Lisää vaihtoehtoja

Tyylin valinta

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Applen CPU:t -keskustelu (M1, M1 Pro, M1 Max...)

- Keskustelun aloittaja SheikYerbouti

- Aloitettu

Jos ytimien määrää nostaa kuvatusti, niin piirin kehä ja siten otollinen alue muistiohjaimille kasvaa aika rajusti. Eiköhän sinne saada tuplattua USB4 ohjaimet ja muistiväylät ilman kummempia ongelmia.

edit: ja ei toi nykyinen kaista ole iso ongelma kuin GPU:n osalta. Ryzen 5950x tulee yllättävän hyvin toimeen hieman matalemmalla kaistalla ja nelinkertaisella laskentakapasiteetilla.

edit: ja ei toi nykyinen kaista ole iso ongelma kuin GPU:n osalta. Ryzen 5950x tulee yllättävän hyvin toimeen hieman matalemmalla kaistalla ja nelinkertaisella laskentakapasiteetilla.

- Liittynyt

- 22.10.2016

- Viestejä

- 12 914

M1-tukee 4kb virtuaalimuistisivujakin.

Ilmeisesti, mutta ne voi olla "toisen luokan kansalaisia" joiden käytössä olessa voi aivan hyvin olla joko

1) pidempi viive L1D-välimuistiiin (esim. osoitteenmuunnos voidaan niille tehdä ennen välimuistin indeksointia)

2) 3/4 L1D-välimuistista kytkettynä pois päältä, siten että jokainen way on vaan 4 kiB.

Edelleenkin odotan lähdettä tälle että liukuhihna olisi lyhyemp, muutakin kuin omat mutuilusi.

Varmaa auktoritääristä lähdettä ei ole, koska Apple ei ole mitään dokumentteja julkaissut. Mutta tämä on aika selvää kun vertaa mittailtuja käskyjen viiveitä A13sta lähtien.

Ja liukuhihnan pituudella tarkoitan tässä enemmän sitä, kuinka paljon peräkkäistä logiikkaa kussakin vaiheessa on, kuin sitä mikä on vaiheiden kokonaismäärä.

Toinen meistä oikeasti töissään mm. optimoi prosessorien liukuhihnan rakennetta jotta niistä saadaan sekä halutut kellotaajuudet että myös mahdollisimman lyhet viiveet tärkeille käskyille, toinen ei ole tainnut tehdä koskaan mitään digitaalisuunnittelua tai matalan tason koodaamista.

AMD ei Zen3:een lisännyt rekisterifilen portteja koska se olisi rajoittanut kellotaajuutta. Applen coressa on tuplamäärä portteja tuplasti suuremmassa rekisterifilessä

Todellinen määrä rekisterinlukuporteissa on n. 1.5-kertainen, ei tuplasti suurempi. Applella lienee kokonaislukupuolella n. 21, AMDllä Zen2ssa/Zen3ssa n.14, mikäli mitään portteja ei ole jaettu eri yksiköiden välillä luottaen siihen, että jotain arvoja saadaan aina bypassilla.

- samoilla liukuhihanpituuksilla toteutettuna AMD:n prosessorikin olisi tiputtunut kellotaajuuksiaan reilusti. Mitä suurien rekisterifileiden käsittelyn optimointeihin tulee niin useimmissa innovaatioissa on mukana ylimääräisiä liukuhihnavaiheita rekisterin käsittelyyn, Applen tuotteista ei tosin paljoa tiedetä mitän siellä tehdään mutta se on selvää että jotain tehdään hyvin eritavalla kuin AMD/Intel toteutuksissa.

Rekisterifileen ja laskentayksiköiden väli on hyvin ongelmallinen paikka millekään ylimääräisille liukuhihnavaiheille CPUssa, koska komento rekisterien lukemiseen voidaan antaa vasta siinä vaiheessa, kun käsky skeduloidaan suoritukseen. Ja sitä, voiko käskyä skeduloida suoritukseen ei taas tiedetä kovin aikaisin. P4ssa kokeiltiin lisätä tähän väliin yksi liukuhihnavaihe lisää ja skeduloida käskyjä tietämättä, saako niitä oikeasti skeduloida, ja perua ja suorittaa käsky uudestaan myöhemmin, jos ei saanutkaan. Tämän vaikutus sekä virrankulutukseen että keskimääräiseen IPChen tosimaailman tilanteissa oli aika kauhea.

Se mikä sen Applen massiivisen rekisterifileen mahdollistaa on nimenomaan se, että ei tavoitella saman luokan kellotaajuuksia.

Näyttiksissä sitten tehdään erilaisia temppuja (esim. multibank-reksiterifilee jossa on yksi "ylimääräinen" liukuhihnavaihe puskuroimassa lukuja ja hanskaamassa bank conflikteja) rekisterifileen virran säästämiseksi, mutta tämä vaan ei ole oikein vaihtoehto CPUlla jossa viive skedulointipäätöksestä käskyn suoritukseen ei vaan saa olla pitkä. Näyttiksissä taas voidaan aivan hyvin suorittaa toista säiettä/warppia tässä välissä, kun niissä ei tavoitella suurta yhden säikeen suorituskykyä.

Viimeksi muokattu:

- Liittynyt

- 22.10.2016

- Viestejä

- 12 914

Artikkelista:

Olen ymmärtänyt M1:n omaavan n. tuplasti leveämmän decoden kuin AMD:n ja Intelin prossut.

Varsinainen decode on moderneissa x86ssa n. puolet(4-5), mutta moderneissa x86ssa on micro-op-välimuisti, josta suoritetaan suurin osa käskyistä, ja josta voi ladata 6-8 mikro-operaatiota kellojaksossa, joten siitä decodesta ei tule mitään pullonkaulaa joka olisi puolt Applen M1n leveydestä.

Rekisterien uudelleennimeämisen leveys taitaa sitten olla zen2lla ja zen3lla 6 käskyä/kellojakso.

Eli todellinen etupään leveysero on luokkaa 1.4-kertainen, ei kaksinkertainen.

Tuo wccftechin artikkeli on muutenkin ihan täyttä roskaa ja todella typerä apples to oranges-vertailu.

wccftech sanoi:It is worth noting that SMT philosophy is embedded in the design. The decode to uOP, and subsequent optimizations for scheduling through retirement (including intermediate issues instruction dependencies, pipe-line bubbles and flushing, etc.), are a large part of why x86 embraced SMT. RISC load/store architectures simply have less front-end decoding complexity, versus decoupled CISC, and thus are able to obtain better Instruction per Thread, per clock.

Höpöhöpö.

Se, että RISCllä on vähemmän kompleksisuutta pitää kyllä paikkaansa, mutta sen vaikutus IPChen on hyvin pieni.

Tosiasiassa suurin IPC-ero x86n ja perinteisen RISCin välillä tulee oleellisesti siitä, että x86 tekee enemän yhdessä käskyssä, joten perinteinen RISC suorittaa enemmän käskyjä saman asian tekemiseen, jolloin sillä kyllä on suurempi IPC muttei silti parempi suorituskyky.

Mutta ARM ei ole mikään perinteinen RISC muutenkaan.

SMT:n piti alunperin tulla ensimmäisenä Digitalin EV8-Alphaan joka olisi ollut RISC-prosessori, mutta se peruttiin kun Alpha tapettiin.

Sen jälkeen muita monisäikeistyksen muotoja tuli mm. Sunin UltraSparc T-sarjaan.

Ainoa asia mikä tekee x86sta "hyvin soveltuvan" monisäikeistykseen on sen pienehkö rekisterimäärä, joka tekee SMTstä hiukan halvempaa intelin prosessoreilla kuin RISC-prosessoreilla joissa on enemmän rekistereitä.

Ja tuo "SMT-enabled single-core" mitä nuo ehdottaa on aivan järjetön, typerä ja epäreilu tapa mitata suorituskykyä.

Se, montako ydintä jossain on on tosiasiassa täysin irrelevanttia. ydinkohtainen suorituskyky on täysin irrelevanttia.

Softassa on säikeitä. Joko vähän tai paljon niistä haluaa olla ajossa. Softa ei piittaa siitä, missä ne säikeet suoritetaan.

Silloin kun softassa on vain yksi säie ajossa(joko siinä ei ole muia säikeitä, tai muut säikeet odotaa jotain dataa tältä säikeeltä), sen ajamiseksi säikeitä, tarvitaan maksimaalinen yhden säikeen suorituskyky. Se, että ytimessä on SMT ei auta siinä yhden säikeen suoituskyvyssä yhtään.

Silloin kun softassa on enemmän säikeitä, on aivan sama, suoritetaanko ne yhdellä ytimellä SMTllä, vai monella ytimellä, vai yhdellä säikeellä peräkkäin. Tällöin on väliä ainoastaan sillä, mikä on kokonaissuorituskyky ja energiatehokkuus yhteensä koko systeemissä.

Viimeksi muokattu:

- Liittynyt

- 22.10.2016

- Viestejä

- 12 914

Uudet huhut bloombergin mukaan sanovat, että Apple olisi työstämässä 2021 loppuun mennessä 16 performance coren mobiiliprosessoria Macbook Prohon ja iMac-linjaan ja 32 coren versiota Mac Prohon. Ja vastaavasti nostaa GPU-corejen määrä 64-128:aan tehokäyttöä varten. M1:ssä GPU-coreja taitaa olla 8.

Jos huhussa on mitään perää, tulee Applelle kyllä melkoisen mielenkiintoisia muistikaistahaasteita, jo nykyinen 128-bittisen kanavan LPDDR4X on M1:n tehokäytöllä täysin tukossa - prosessori lienee suunniteltu muistiväylän ympärille maksimoiden käyttö. Lienee melkoisen hyvä kysymys, että millä suhteellisen virtapihillä tavalla saataisiin kaista vielä nelinkertaistettua ensin 16 coren versioon ja siitä vielä vielä ylöspäin työpöytämalleihin.

Jos muistikaista pidetään tarpeeksi leveänä, tuollaiset prosessorit taitaa jättää jälkeensä ihan kaiken mitä x86-raudalle saa kaupasta.

Eiköhän sinne samaan pakettiin ole melko helppo laittaa tuplasti suurempi määrä muistipiirejä, tuplaten samalla sekä kapasiteetti että kaista. Molempia kaipaa niissä järeämmissä malleissa.

Ainakaan täysin samalla tekniikalla ei onnistu, jos tarkoitus on korvata myös 64 gigan muistilla varustettu Macbook Pro 16", kun ei ole olemassa tarpeeksi suuria LPDDR4/LPDDR5-muistipiirejä, jotta neljällä muistipiirillä saataisiin 64 gigaa muistia. Sitten tietysti onnistuu, jos muistit otetaan prosessorista erilleen. Itse kyllä suhtaudun puhtaaseen LPDDR-ratkaisuun skeptisesti, jos näytönohjaimen suorituskyky on tarkoitus jopa nelinkertaistaa, kuten huhuissa on. Ei riitä silloin muistikaistan tuplaus.Eiköhän sinne samaan pakettiin ole melko helppo laittaa tuplasti suurempi määrä muistipiirejä, tuplaten samalla sekä kapasiteetti että kaista. Molempia kaipaa niissä järeämmissä malleissa.

Kyllä ainakin Micronilta saa LPDDR5-muisteja 16 gigatavun piireissä. Niitä neljä kappaletta ja saadaan 64 gigaa muistia. Eli jos tuplataan kaista tuplaamalla muistipiirien määrä ja siirrytään LPDDR4X:stä LPDDR5:een mistä saadaan toinen 50% lisää kaistaa, niin kyllä siinä ainakin melko lähellä nelinkertaistamista ollaan.Ainakaan täysin samalla tekniikalla ei onnistu, jos tarkoitus on korvata myös 64 gigan muistilla varustettu Macbook Pro 16", kun ei ole olemassa tarpeeksi suuria LPDDR4/LPDDR5-muistipiirejä, jotta neljällä muistipiirillä saataisiin 64 gigaa muistia.

user9999

Platinum-jäsen

- Liittynyt

- 17.10.2016

- Viestejä

- 3 304

Microsoft kanssa kiinnostunut ARM siruista.

www.tivi.fi

www.tivi.fi

www.cnbc.com

www.cnbc.com

Intel sai erittäin huonon joululahjan Microsoftilta

Myös Microsoft on Applen tavoin kääntämässä selkäänsä Intelille.

Intel falls on report Microsoft plans to design own chips for PCs and servers

Intel has famously had a long-running partnership with Microsoft as the primary processor maker for Windows PCs.

Tup3x

ツ

- Liittynyt

- 18.10.2016

- Viestejä

- 2 489

Kuluttajat voittavat jos PC puolen (käytännön) duopoli saadaan purettua. Mielenkiinnolla odotan sitä päivää, milloin desktop puolelle saadaan useamman eri valmistajan prosessoreita.Microsoft kanssa kiinnostunut ARM siruista.

Intel sai erittäin huonon joululahjan Microsoftilta

Myös Microsoft on Applen tavoin kääntämässä selkäänsä Intelille.www.tivi.fi

Intel falls on report Microsoft plans to design own chips for PCs and servers

Intel has famously had a long-running partnership with Microsoft as the primary processor maker for Windows PCs.www.cnbc.com

- Liittynyt

- 19.10.2016

- Viestejä

- 1 060

Suorituskykyä näistä ARMin suunnittelimista palvelinkäyttöön tarkoitetuista ARM ytimistä kyllä löytyy:

Haastavat suorituskyvyssä uusimmat Epycit ja Xeonit ja ovat niitä halvempia. Myöskin AWS instanneista Amazonin omaan ARM rautaan perustuvat ovat kaikkein halvimpia.

Miltä näyttää data center/pilvi/palvelin rauta 5-10 vuoden päästä, se onkin mielenkiintoista!

AnandTech Forums: Technology, Hardware, Software, and Deals

Seeking answers? Join the AnandTech community: where nearly half-a-million members share solutions and discuss the latest tech.

www.anandtech.com

Haastavat suorituskyvyssä uusimmat Epycit ja Xeonit ja ovat niitä halvempia. Myöskin AWS instanneista Amazonin omaan ARM rautaan perustuvat ovat kaikkein halvimpia.

Miltä näyttää data center/pilvi/palvelin rauta 5-10 vuoden päästä, se onkin mielenkiintoista!

Mielenkiintoista vertailua M1:n ja A14:n välillä.

www.extremetech.com

www.extremetech.com

Comparison of Apple M1, A14 Shows Differences in SoC Design - ExtremeTech

A new analysis of the M1 breaks down the die design versus the smartphone-class A14 SoC.

- Liittynyt

- 07.11.2016

- Viestejä

- 2 508

Tuli tässä mielessäni pohdittua, että saattaa tästä loppujen lopuksi tulla aikamoinen piikki Intelin suuntaan. Ei välttämättä Applen takia, vaan sitten parin vuoden päästä kun muut ARM-valmistajat ovat samalla tasolla tämän hetken kanssa, ja Microsoft on virallisesti myymässä Windows/ARM:ia, jossa toimii x86-64 softat emuloimalla nopeammin kuin intelin alemman hintaluokan prosuissa.

Enkä tässä tarkoita tämän foorumin high-end koneita, vaan normaaleja konttorirotan ja muun peruskäytön koneita.. Eiköhän noistakin tuoda eka generaatio markkinoille ison feikkikotelon kera kuten 1990-luvun markettihifisysteemit

Enkä tässä tarkoita tämän foorumin high-end koneita, vaan normaaleja konttorirotan ja muun peruskäytön koneita.. Eiköhän noistakin tuoda eka generaatio markkinoille ison feikkikotelon kera kuten 1990-luvun markettihifisysteemit

Milloin Mac Pro M prosessorilla on realistisesti markkinoilla? Seuraavan 3 vuoden aikana ehkä?

Olisin todella yllättynyt jos sitä ei julkaista ensi vuoden aikana. Apple tekee tämänlaiset muutokset vauhdilla.

- Liittynyt

- 18.10.2016

- Viestejä

- 4 931

Apple lupaili että tuo siirtymä Intel -> ARM olisi valmis kahden vuoden sisällä. Riippuen sitten miten nopeasti saavat noita kehitettyä niin ehkä ensi vuoden lopulla saattaa jo ensimmäinen Mac Pro (jotain huhuja ollut "Lite" mallista) olla julkaisuvalmiina.Milloin Mac Pro M prosessorilla on realistisesti markkinoilla? Seuraavan 3 vuoden aikana ehkä?

user9999

Platinum-jäsen

- Liittynyt

- 17.10.2016

- Viestejä

- 3 304

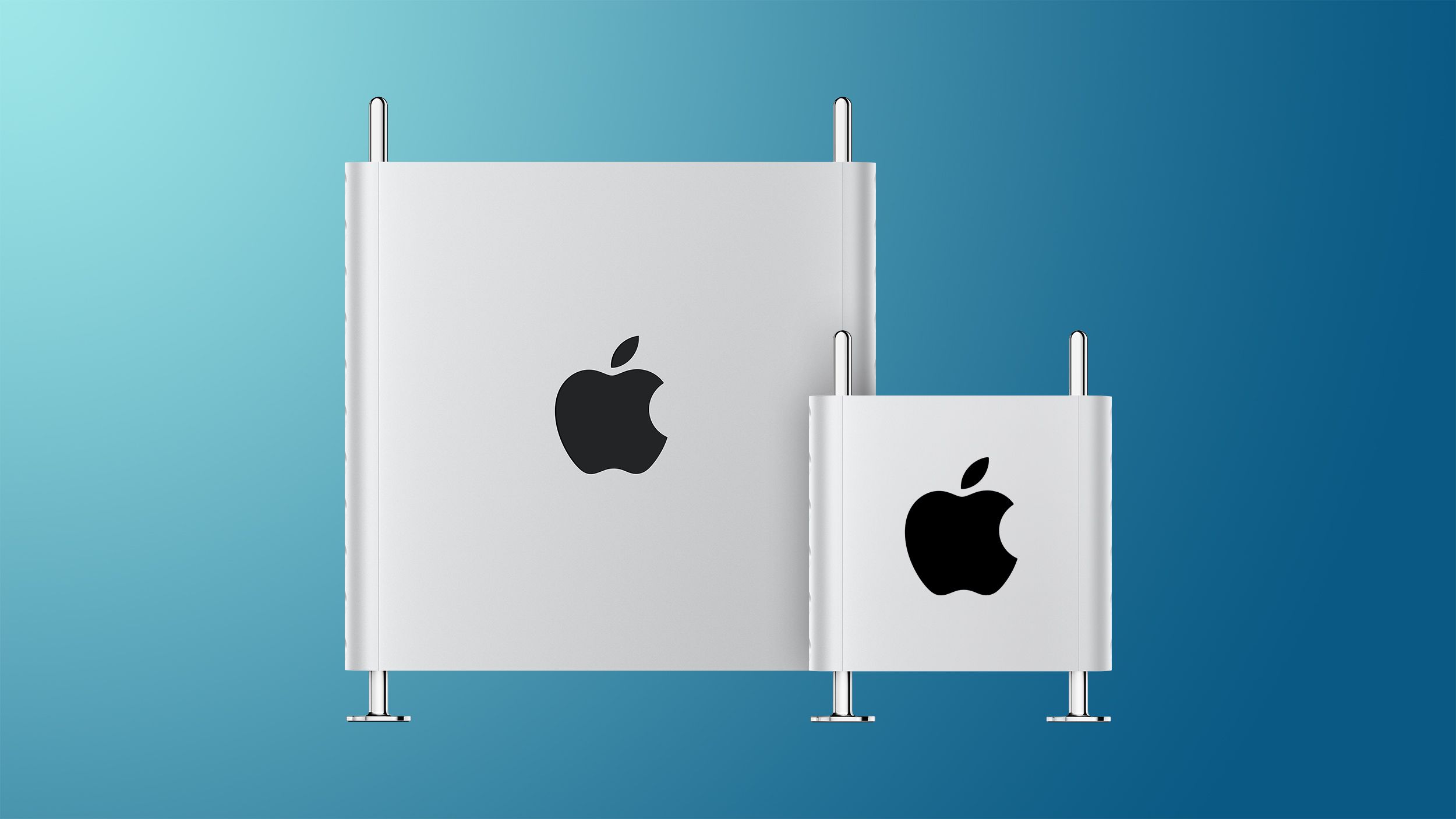

Alla huhua tuosta pienemmästä Mac Pro koneesta.

www.macrumors.com

www.macrumors.com

Apple Working on Redesigned Mac Pro With Smaller Form Factor and Apple Silicon Chip

As part of the transition to Apple Silicon, Apple is designing a new Mac Pro that has a smaller form factor, reports Bloomberg. The new Mac Pro is said to have a design that looks like the current design, but in a more compact enclosure that's "about half the size". It is not known if the new...

finWeazel

Tukijäsen

- Liittynyt

- 15.12.2019

- Viestejä

- 14 174

Menee varmaan ihan samalla tavalla nuo cpu:t kuin iphone/tableteissakin. m1x on kyllä melko peto paperilla. Hyvä juttu nuo low power coret. Ehkä tuollainen järeämpikin laite pysyisi peruskäytössä viileänä ja ei ime hetkessä akkua tyhjäksi? Lieköhän saavat gpu:lle miten virransäästön tehtyä? Äkkiseltään voisi kuvitella, että isompi gpu peruskäytössä voisi olla pienemmällä kellotaajuudella ja siten virtatehokkaampi kuin m1:ssa oleva kapeampi gpu? Hörppisi enemmän virtaa vain isomman kuorman alla?

Jännä nähdä nostavatko x-mallissa kellotaajuutta vai onko vain ytimiä lisää.

Jännä nähdä nostavatko x-mallissa kellotaajuutta vai onko vain ytimiä lisää.

finWeazel

Tukijäsen

- Liittynyt

- 15.12.2019

- Viestejä

- 14 174

Mac Pro huhua pukkaa. Härveli on huomattavasti pienempi kuin nykyinen mac pro. Omaa spekulointia. Olisikohan yksi tai kaksi giganttisen kokoista APUa pohjalla ja siili päällä. Ei enää erillisiä gpu/kiihdytinyksiköitä tarjolla?

www.macrumors.com

www.macrumors.com

Internally, Prosser says that the Mac Pro will be designed with the "compute unit on the bottom" and a "big heat sink on top."

Prosser has now said that the new Mac Pro will feature a design that looks like "three to four Mac minis stacked on top of each other,"

Prosser: 2021 iMac to Come in Five Colors, Apple Silicon Mac Pro to Resemble 'Stacked' Mac Minis

Hit-and-miss leaker Jon Prosser has today alleged that the upcoming 2021 iMac models will offer five color options, mirroring the colors of the fourth-generation iPad Air, and revealed a number of additional details about the Mac Pro with Apple Silicon. In a new video on YouTube channel...

user9999

Platinum-jäsen

- Liittynyt

- 17.10.2016

- Viestejä

- 3 304

Apple alkaa lopettaa noita Intel maccejä, Nyt vuorossa iMac Pro.

www.macrumors.com

www.macrumors.com

Apple Confirms iMac Pro Will Be Discontinued When Supplies Run Out, Recommends 27-Inch iMac

Apple on late Friday evening added a "while supplies last" notice to its iMac Pro product page worldwide, and removed all upgrade options for the computer, leaving only the standard configuration available to order for now. We've since confirmed with Apple that when supplies run out, the iMac...

- Liittynyt

- 25.10.2018

- Viestejä

- 672

Mitähän käytännön eroa noin muuten on vaikkapa intel i5 läppäriprossulla ja Apple M1 prossulla. Kun verrataan vaikka seuraavien läppärien prossuja. Muuten taitaa olla samanlaiset läppärit. Onko järkeä maksaa lähes 150€ extraa M1 vs i5?

www.gigantti.fi

www.gigantti.fi

www.gigantti.fi

www.gigantti.fi

Sori jos oli väärä ketju, mutta tuo M1 prossun ja i5 läppäriprossun ero nyt lähinnä kiinnostaa 8 core vs 4 core lisäksi.

MacBook Air 2020 13,3" 256 GB (tähtiharmaa) - Gigantti verkkokauppa

MacBook Air 2020 -kannettava kulkee vaivatta mukanasi. Laitteen erittäin kevyt runko sisältää yksityiskohtaisen Retina-näytön, 10.

MacBook Air 13 M1/8/256 2020 (tähtiharmaa) - Kannettavat tietokoneet

MacBook Air 13 M1 2020 -kannettavassa on uusi 8-ytiminen Apple M1 -siru, 13” Retina-näyttö, P3-väriavaruus, FaceTime HD -kamera ja Magic Keyboard -näppäimistö. Ostaessasi MacBook Air -kannettavan saat Apple TV+ -palvelun veloituksetta 3 kuukaudeksi.

Sori jos oli väärä ketju, mutta tuo M1 prossun ja i5 läppäriprossun ero nyt lähinnä kiinnostaa 8 core vs 4 core lisäksi.

Jos et mitään erikoista tee läppärillä, vaan se tulee perus surffailuun ja ehkä kevyeeseen kuvankäsittelyyn tmv. niin M1 tarjoaa täysin ylivertaista akkukestoa ja suorituskykyä. Jos vaikkapa koodaat tai muuta vähän erikoisempaa niin sit kannattaa ottaa selvää että toimiiko tarvitsemasi työkalut ja ympäristöt tolla M1 mäkillä.Mitähän käytännön eroa noin muuten on vaikkapa intel i5 läppäriprossulla ja Apple M1 prossulla. Kun verrataan vaikka seuraavien läppärien prossuja. Muuten taitaa olla samanlaiset läppärit. Onko järkeä maksaa lähes 150€ extraa M1 vs i5?

MacBook Air 2020 13,3" 256 GB (tähtiharmaa) - Gigantti verkkokauppa

MacBook Air 2020 -kannettava kulkee vaivatta mukanasi. Laitteen erittäin kevyt runko sisältää yksityiskohtaisen Retina-näytön, 10.www.gigantti.fi

MacBook Air 13 M1/8/256 2020 (tähtiharmaa) - Kannettavat tietokoneet

MacBook Air 13 M1 2020 -kannettavassa on uusi 8-ytiminen Apple M1 -siru, 13” Retina-näyttö, P3-väriavaruus, FaceTime HD -kamera ja Magic Keyboard -näppäimistö. Ostaessasi MacBook Air -kannettavan saat Apple TV+ -palvelun veloituksetta 3 kuukaudeksi.www.gigantti.fi

Sori jos oli väärä ketju, mutta tuo M1 prossun ja i5 läppäriprossun ero nyt lähinnä kiinnostaa 8 core vs 4 core lisäksi.

- Liittynyt

- 22.10.2016

- Viestejä

- 12 914

Mitähän käytännön eroa noin muuten on vaikkapa intel i5 läppäriprossulla ja Apple M1 prossulla. Kun verrataan vaikka seuraavien läppärien prossuja. Muuten taitaa olla samanlaiset läppärit. Onko järkeä maksaa lähes 150€ extraa M1 vs i5?

MacBook Air 2020 13,3" 256 GB (tähtiharmaa) - Gigantti verkkokauppa

MacBook Air 2020 -kannettava kulkee vaivatta mukanasi. Laitteen erittäin kevyt runko sisältää yksityiskohtaisen Retina-näytön, 10.www.gigantti.fi

MacBook Air 13 M1/8/256 2020 (tähtiharmaa) - Kannettavat tietokoneet

MacBook Air 13 M1 2020 -kannettavassa on uusi 8-ytiminen Apple M1 -siru, 13” Retina-näyttö, P3-väriavaruus, FaceTime HD -kamera ja Magic Keyboard -näppäimistö. Ostaessasi MacBook Air -kannettavan saat Apple TV+ -palvelun veloituksetta 3 kuukaudeksi.www.gigantti.fi

Sori jos oli väärä ketju, mutta tuo M1 prossun ja i5 läppäriprossun ero nyt lähinnä kiinnostaa 8 core vs 4 core lisäksi.

Helpompi olisi kysyä, että mitä niissä on yhteistä, ja siihen vastaus olisi: ainoa yhteinen asia on, että molemmilla voi ajaa Macos X:ää.

Kyse on täysin eri piireistä jotka on aivan erilaisia, ajaa eri käskykantaa jne, arkkitehtuuriltaan kaikilta tasoilta aivan erilaisia jne.

Tämä on nimenomaan oikea ketju, jos vaan lukisit ketjun alusta asti.

M1 on SoC-piiri, jossa on samassa paketissa

1) Muistit, melko nopealla muistirajapinnalla

2) Piilastu, jossa on sekä

a) 4 kpl Applen uusia Firestorm-ytimiä jotka ajavat ARMv8-käskykantaa ja joiden suorituskyky on todella hyvä (kellotaajusukohtainen suorituskyky melkein 1.5x parempi kuin Intelillä ja AMDllä mutta kellot hiukan alemmat) ja energiatehokkuus Inteliä ja AMDtä edellä

b) 4 kpl Applen "Icestorm"-pikkuytimiä jotka eivät ole suorituskyvyltään aivan mopoja mutta joiden energiatehokkuus on vielä paljon parempi

c) Integroitu näyttis joka on tehokkaampi kuin misssään Intelin tai AMDn PC-markkinoille myytävässä CPUn sisältävässä piirissä (AMDn konsolipiireissä on toki tehokkaampi näyttis ja erillisnäyttikset on toki tehokkaampia)

d) tekoälykiihdytin ja vaikka mitä muuta erikoiskiihdyttimiä.

150e on todella halpa hinta siitä suorituskyky- ja akunkestoerosta mitä tämä tarjoaa i5een nähden.

Haittapuolena on lähinä se, että näissä ei pyöri windows ja windows-softat, koska nämä eivät aja natiivisti x86-koodia. Näissä on kyllä MacosX:ssä binäärikäännössofta, jonka avulla melkein kaikki x86lle käännetty macos X-softa toimii (jopa melko hyvällä suorituskyvyllä).

Eli, tämä uusi malli ei enää kelpaa sellaiseksi pelikoneeksi, jonka boottaa windowsiin pelailua varten ja pelaa sillä windowsista kaikkia pelejä, sillä voi käytännössä pelata vaan niitä pelejä, joista on macos X-versio olemassa (ja yllättävän suuresta osasta parhaita pelejä on, esim. Blizzardin pelit, Paradoxin pelit, Civilizationit, War thunder, League of Legends jne)

Viimeksi muokattu:

No ei kai nyt sentään?c) Integroitu näyttis joka on tehokkaampi kuin misssään Intelin tai AMDn piirissä

Nopeampi kuin kummankaan yhdessäkään läppäriprossussa, mut kyllä niillä nopeampia piirejä löytyy ihan urakalla.

Mä luulen että nuo Intel-pohjaiset Macbookit ovat arvon puolesta lähes ongelmajätettä parin vuoden päästä (vaikka tietty Applen tuotteet pitävät arvonsa paremmin kuin PC-maailman laitteet). M1-mallit ovat niin paljon parempia. Tässä alkuvaiheessa ei löydy kaikista softista natiiviversioita, mutta tilanne paranee nopeasti.

Viimeksi muokattu:

- Liittynyt

- 22.10.2016

- Viestejä

- 12 914

No ei kai nyt sentään?

Nopeampi kuin kummankaan yhdessäkään läppäriprossussa, mut kyllä niillä nopeampia piirejä löytyy ihan urakalla.

Hups, tarkoitin siis CPUn sisältäviä yhdistelmäpiirejä. Pitänee editoida alkup kommenttia.

- Liittynyt

- 20.10.2018

- Viestejä

- 2 714

150€ panostus kannattaa jo ihan muutamastakin syystä:Mitähän käytännön eroa noin muuten on vaikkapa intel i5 läppäriprossulla ja Apple M1 prossulla. Kun verrataan vaikka seuraavien läppärien prossuja. Muuten taitaa olla samanlaiset läppärit. Onko järkeä maksaa lähes 150€ extraa M1 vs i5?

MacBook Air 2020 13,3" 256 GB (tähtiharmaa) - Gigantti verkkokauppa

MacBook Air 2020 -kannettava kulkee vaivatta mukanasi. Laitteen erittäin kevyt runko sisältää yksityiskohtaisen Retina-näytön, 10.www.gigantti.fi

MacBook Air 13 M1/8/256 2020 (tähtiharmaa) - Kannettavat tietokoneet

MacBook Air 13 M1 2020 -kannettavassa on uusi 8-ytiminen Apple M1 -siru, 13” Retina-näyttö, P3-väriavaruus, FaceTime HD -kamera ja Magic Keyboard -näppäimistö. Ostaessasi MacBook Air -kannettavan saat Apple TV+ -palvelun veloituksetta 3 kuukaudeksi.www.gigantti.fi

Sori jos oli väärä ketju, mutta tuo M1 prossun ja i5 läppäriprossun ero nyt lähinnä kiinnostaa 8 core vs 4 core lisäksi.

- Intel Maccien käyttöjärjestelmätuki tulee olemaan suppeampi tulevaisuudessa

- Lähes kaikki perussovellukset pyörivät jo M1 Maceissä, ja tuki kasvaa nopeasti erikoissovelluksiin.

- M1 on läppäreissä varsinkin todella kova mylly ja suorituskyvyltään reilusti tuota i5:sta parempi, mutta energiatehokkuus vasta onkin omassa luokassaan 20h akkukestonsa kanssa. Harvassa läppärissä tuollaisia akkukestoja.

- M-sarjan prosessorit ovat todennäköisesti Applen tulevaisuus, ja tuki on parempi.

Ja mikäli nyt meinaa 150€:n takia alkaa pihistellä, niin mieti asiaa vaikka näin, että todennäköisesti saat vuosien päästä 150€ enemmän jos myyt tuon M1 Macin käytettynä, verrattuna jos myisit Intel Macin jolle ei ole käyttöjärjestelmä tukea.

E: Muutenkin mäkeissä on yleensä hyvät jälleenmyyntiarvot. Esimerkiksi 2012 lopulla ostettu puolentoista tonnin mäkki vaihtoi omistajaa kahdeksan vuoden jälkeen vielä 350 euroa vastaan. Intelillä varustettujen mäkkien jälleenmyyntiarvo tosin tulee nyt putoamaan radikaalimmin, kun Applen omat prosessorit tulevat koko mallistoon ja käyttöjärjestelmät siirtyvät pääasiallisesti tukemaan niitä.

Viimeksi muokattu:

- Liittynyt

- 18.10.2016

- Viestejä

- 4 931

Jos vaan millään niin ehdottomasti kannattaa tuo lisäpanostus tuohon M1 versioon.Sori jos oli väärä ketju, mutta tuo M1 prossun ja i5 läppäriprossun ero nyt lähinnä kiinnostaa 8 core vs 4 core lisäksi.

Eikös tuossa 2020 vuoden Intel Airissa ollut vielä kaikenlisäksi ihan täysin riittämätön jäähdytys.

- Liittynyt

- 01.11.2016

- Viestejä

- 517

Jos vaan millään niin ehdottomasti kannattaa tuo lisäpanostus tuohon M1 versioon.

Eikös tuossa 2020 vuoden Intel Airissa ollut vielä kaikenlisäksi ihan täysin riittämätön jäähdytys.

Ei missään nimessä Inteliä jos M1 tarjolla. Laitteen jälleenmyyntiarvo, jäähdytys, akunkesto, suorituskyky kaikki M1 puolella. Itse juuri pohdin että laitanko oman vuoden vanhan MBP:n Applen palautusohjelmaan M1 MBP:sta vastaan. Siitä kun vielä saisi rahaa.

user9999

Platinum-jäsen

- Liittynyt

- 17.10.2016

- Viestejä

- 3 304

Apple on varannut 4nm tuotantokapasiteettiä TSMC:ltä.

www.macrumors.com

www.macrumors.com

Apple Orders 4nm Chip Production for Next-Generation Macs

Apple has booked the initial production capacity of 4nm chips with long-time supplier TSMC for its next-generation Apple silicon, according to industry sources cited in a new report today from DigiTimes. From today's report: Apple has already booked the initial capacity of TSMC's N4 for its...

- Liittynyt

- 22.10.2016

- Viestejä

- 12 914

Apple on varannut 4nm tuotantokapasiteettiä TSMC:ltä.

Apple Orders 4nm Chip Production for Next-Generation Macs

Apple has booked the initial production capacity of 4nm chips with long-time supplier TSMC for its next-generation Apple silicon, according to industry sources cited in a new report today from DigiTimes. From today's report: Apple has already booked the initial capacity of TSMC's N4 for its...www.macrumors.com

"4nm", heeetkonen. Tuollaista ei ollut vielä vähän aikaa sitten TSMCn roadmapissä. Eli menivät sitten uudelleenimeämään vähän viilatun version "5nm" prosessista "4nm" prosessiksi. Toisaalta ymmärrettävää, koska Samsungin "5nm" on selvästi isompi kuin TSMCn "5nm" vaikka TSMCn "5nm" sekin ansaitsisi vain nimen "5.8nm" jos verrataan skaalautumista "7m" prosessiin (joka sekin on jo todella pahasti deflatoitunut). Tässä prosessien nimien deflaatiossa ei meinaa millään pysyä perässä.

user9999

Platinum-jäsen

- Liittynyt

- 17.10.2016

- Viestejä

- 3 304

Seuraava Apple Silicon versio menossa tuotantoon. Onko se sitten M1X tai M2..

www.macrumors.com

www.macrumors.com

asia.nikkei.com

asia.nikkei.com

Apple's 'M2' Next-Gen Mac Chip Enters Mass Production, Expected to Debut in Redesigned MacBooks Later This Year

Apple's custom next-generation Mac processor entered mass production this month, claims a new report today from Nikkei Asia. Tentatively dubbed the "M2" after Apple's M1 chip, the processors take at least three months to produce and could begin shipping as early as July in time for incorporation...

Apple's follow-up to M1 chip goes into mass production for Mac

TSMC-made chipsets to replace Intel offerings in laptops set to launch in 2H

- Liittynyt

- 20.10.2016

- Viestejä

- 5 237

TSMC:n roadmapissa on nyt 4nm, 3nm ja 2nm, mitä sitten lienevätkään"4nm", heeetkonen. Tuollaista ei ollut vielä vähän aikaa sitten TSMCn roadmapissä. Eli menivät sitten uudelleenimeämään vähän viilatun version "5nm" prosessista "4nm" prosessiksi. Toisaalta ymmärrettävää, koska Samsungin "5nm" on selvästi isompi kuin TSMCn "5nm" vaikka TSMCn "5nm" sekin ansaitsisi vain nimen "5.8nm" jos verrataan skaalautumista "7m" prosessiin (joka sekin on jo todella pahasti deflatoitunut). Tässä prosessien nimien deflaatiossa ei meinaa millään pysyä perässä.

TSMC Roadmap Update: 4nm, 3nm (FinFet) in 2022; 2nm GAA in R&D | Hardware Times

TSMC is the world’s leading foundry, and that status is unlikely to change in the next 4-5 years. The company’s N5 (5nm EUV) node showcased in Apple’s M1 SoCs is the world’s most advanced process, roughly on par with Intel’s 7nm technology which will be launched two years from now (at the...

www.hardwaretimes.com

www.hardwaretimes.com

4nm prosessia verrataan N5 eikä esim. N5P-prosessiin, joten taitaa olla jälleen yksi (Applelle dedikoitu?) markkinointiprosessi.

- Liittynyt

- 22.10.2016

- Viestejä

- 12 914

TSMC:n roadmapissa on nyt 4nm, 3nm ja 2nm, mitä sitten lienevätkään

TSMC Roadmap Update: 4nm, 3nm (FinFet) in 2022; 2nm GAA in R&D | Hardware Times

TSMC is the world’s leading foundry, and that status is unlikely to change in the next 4-5 years. The company’s N5 (5nm EUV) node showcased in Apple’s M1 SoCs is the world’s most advanced process, roughly on par with Intel’s 7nm technology which will be launched two years from now (at the...www.hardwaretimes.com

4nm prosessia verrataan N5 eikä esim. N5P-prosessiin, joten taitaa olla jälleen yksi (Applelle dedikoitu?) markkinointiprosessi.

Kyllä se varmaan kaikille mullekin tulee. Voi olla että osa niistä muiden tuotteista joiden piti tulla "5nm" prosessilla tarkoittaa juuri tuota uutta uudelleennimettyä versiota ja muutkin joutuu päivittämään slidejään siitä, millä valmistustekniikalla heidän tuotteensa tullaan valmistamaan.

Mutta jännä tuo TSMCn mainostama "0x55x-45%(1.8x) tuon N5 vs N7 kohdalla pinta-alassa. Voi päteä jollekin yhdelle standardikomponentille, muttei todellakaan ole mikään yleinen tiheysparannus.

Mitään tarkkoja näkemäni lukuja en saa sanoa, mutta ne todelliset luvut mitä olen nähnyt saman ytimen synteesituloksista sekä TSMCn "7nm" prosessille että "5nm" prosessille antaa kyllä ihan eri luokan pienennyksiä pinta-alaan.

- Liittynyt

- 18.10.2016

- Viestejä

- 3 314

Diablo 2:R ei vaan tuettu Maceissa. Ei 32bit tukea. Peli vissiin vain 32bit ainakin toistaiseksi.Täällä menee samantien ostoon Ipad laite missä toimii Mac OS ja M1 tai paremmalla piirillä. Ei tarvii ku laittaa USB-C telakkaan kiinni niin voi pelata Wow TBC classiccia / Diablo 2 Rescurrected. Tämä olis boomer pelaajan unelma .

Hieman juttua Macin käyttiksen skeduloinnista. Apple M1:n koettu ripeys johtuu osittain siitä, että käyttöjärjestelmässä on priorisoitu käyttäjäkokemus ykköseksi maksimisuorituskyvyn kustannuksella (tosin miten mahtanee näkyä raskaammassa kuormituksessa). Itse olen vuosikaudet ihmetellyt Windowsin tahmaisuutta varsinkin heti bootin jälkeen, kun kaiken maailman virustutkat ja päivitystarkistukset pyörivät.

arstechnica.com

arstechnica.com

Apple’s M1 is a fast CPU—but M1 Macs feel even faster due to QoS

Howard Oakley did an excellent deep dive on M1 scheduling and performance.

arstechnica.com

arstechnica.com

Hieman juttua Macin käyttiksen skeduloinnista. Apple M1:n koettu ripeys johtuu osittain siitä, että käyttöjärjestelmässä on priorisoitu käyttäjäkokemus ykköseksi maksimisuorituskyvyn kustannuksella (tosin miten mahtanee näkyä raskaammassa kuormituksessa). Itse olen vuosikaudet ihmetellyt Windowsin tahmaisuutta varsinkin heti bootin jälkeen, kun kaiken maailman virustutkat ja päivitystarkistukset pyörivät.

Apple’s M1 is a fast CPU—but M1 Macs feel even faster due to QoS

Howard Oakley did an excellent deep dive on M1 scheduling and performance.arstechnica.com

Mikä ripeys? Himassa macbook pro M1 eikä tuo mitenkään erikoiselta tunnu verrattuna Win10 koneisiin. Itseasiassa hyrrää kyllä pyörittelee usein. Lisäksi jos käyttää chromea ja wordia niin akunkestokin on about vitsin luokkaa verrattuna revikoihin. Duunissa valitellaan et M1 Air on hidas.

finWeazel

Tukijäsen

- Liittynyt

- 15.12.2019

- Viestejä

- 14 174

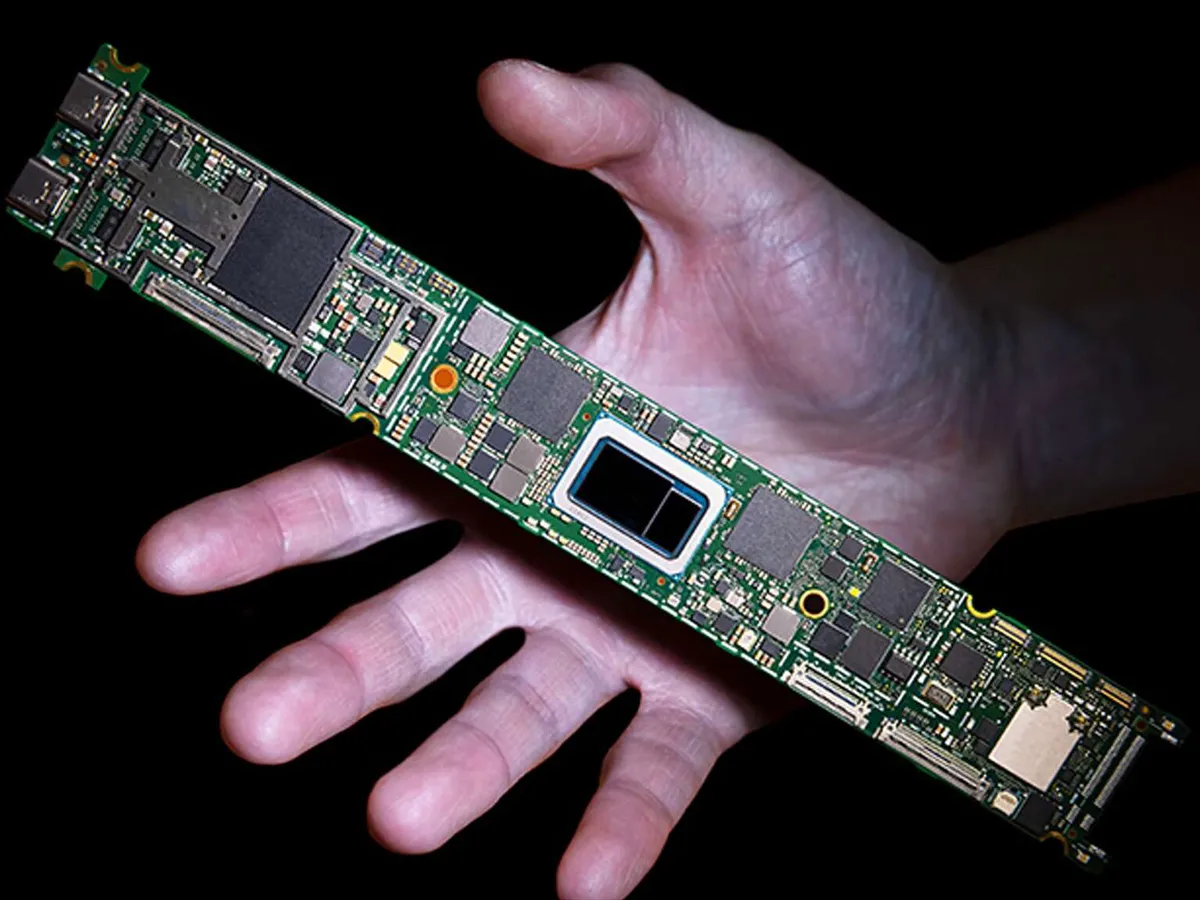

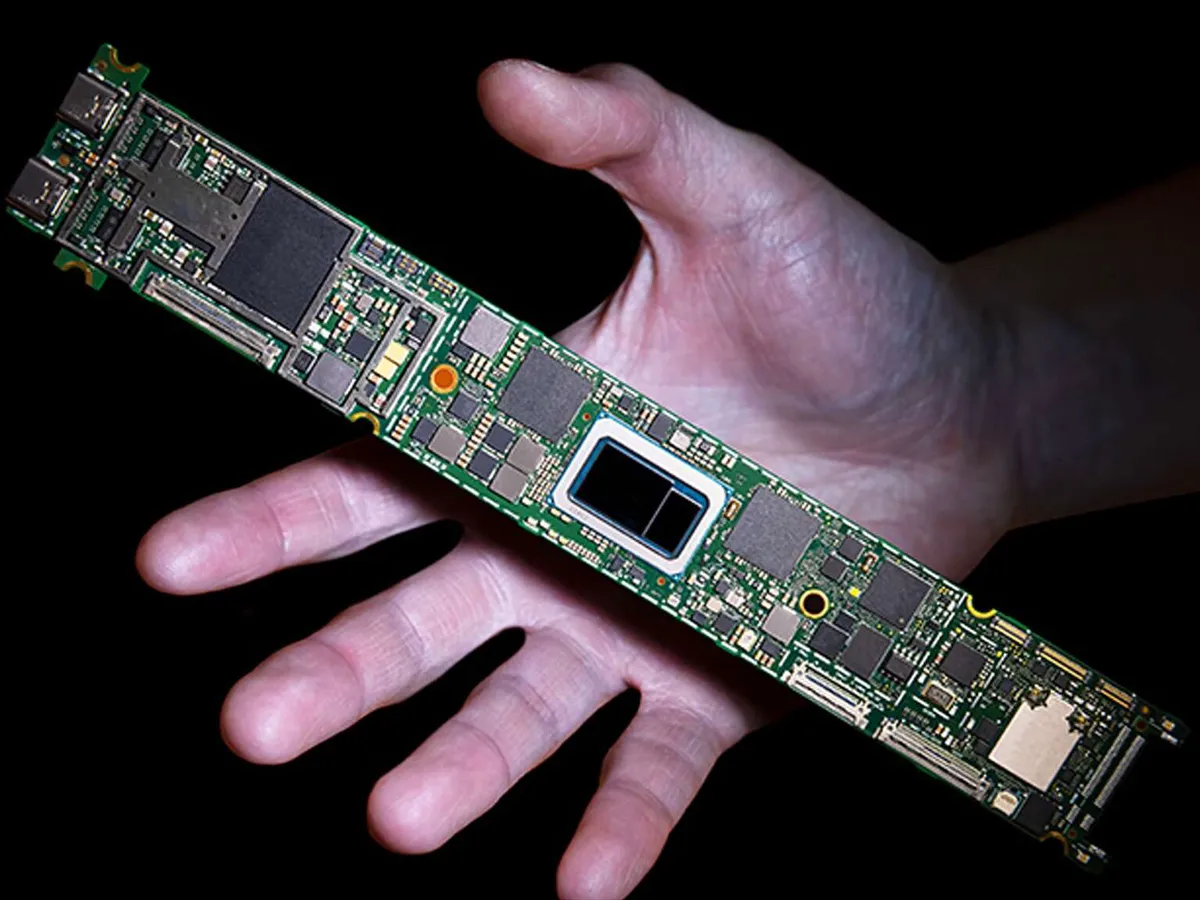

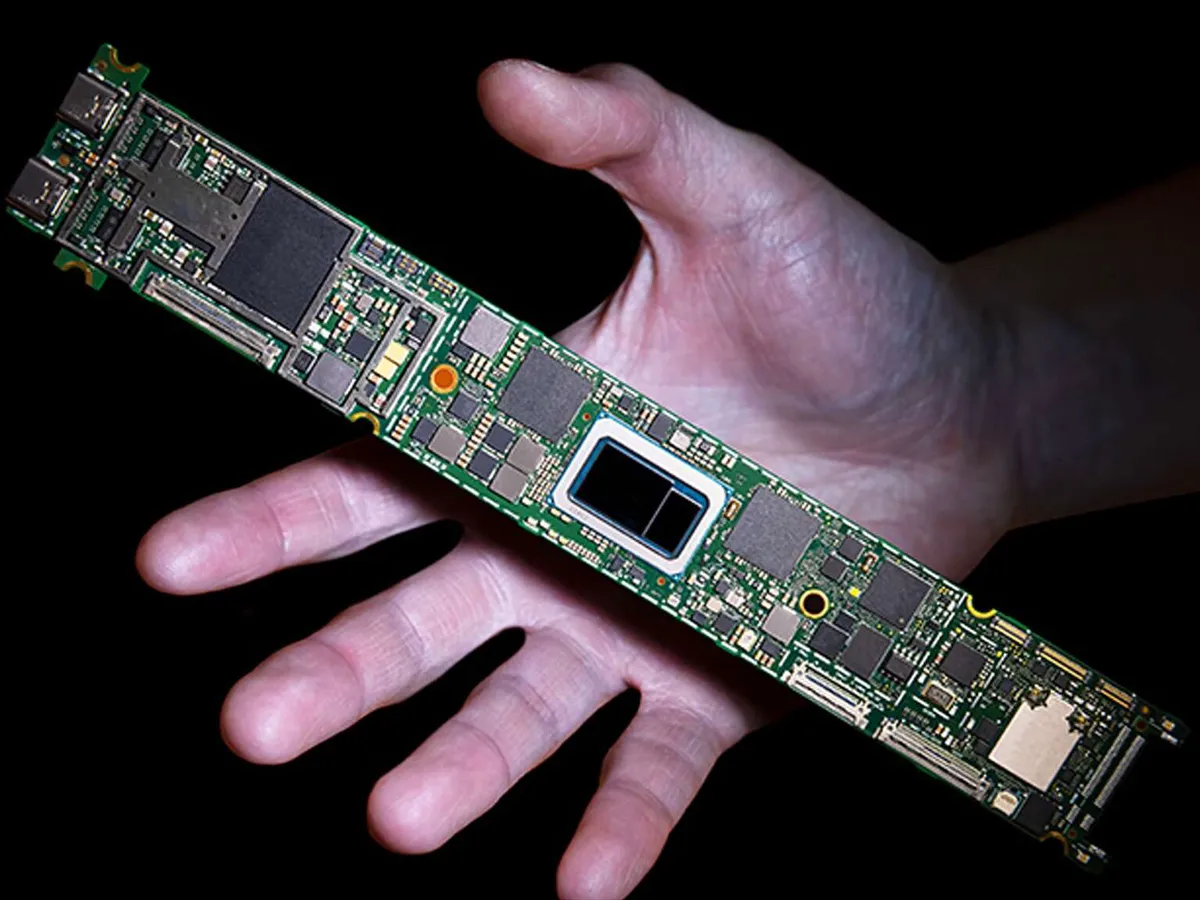

Uutta huhua seuraavista applen mobiili ja työpöytäpiireistä. Itse artikkelissa enemmänkin asiaa kuin mitä lainasin alle. 32+8 cpu corea tulossa tykeimpiin mac pro pöytäkoneisiin. Läppäreihin 8+2cpu core ratkaisu tulossa.

www.bloomberg.com

www.bloomberg.com

Codenamed Jade 2C-Die and Jade 4C-Die, a redesigned Mac Pro is planned to come in 20 or 40 computing core variations, made up of 16 high-performance or 32 high-performance cores and four or eight high-efficiency cores. The chips would also include either 64 core or 128 core options for graphics. The computing core counts top the 28 core maximum offered by today’s Intel Mac Pro chips, while the higher-end graphics chips would replace parts now made by Advanced Micro Devices Inc.

For a redesigned, higher-end MacBook Air planned for as early as the end of the year, Apple is planning a direct successor to the M1 processor. That chip, codenamed Staten, will include the same number of computing cores as the M1 but run faster. It will also see the number of graphics cores increase from seven or eight to nine or 10

For the new MacBook Pros, Apple is planning two different chips, codenamed Jade C-Chop and Jade C-Die: both include eight high-performance cores and two energy-efficient cores for a total of 10, but will be offered in either 16 or 32 graphics core variations

Apple Readies MacBook Pro, MacBook Air Revamps

Apple Inc. is preparing to release several new Mac laptops and desktops with faster processors, new designs and improved connectivity to external devices, accelerating the company’s effort to replace Intel Corp. chips and leapfrog rival PC makers.

- Liittynyt

- 17.10.2016

- Viestejä

- 14 102

Itselleni kiinnostavimmat julkaisut tulevat olemaan nuo 16 ja 32 graphic core variantit MBP:hen / iMaciin jne.

Niiden tarvitsema muistikaista on myös suuri mysteeri. Etenkin tuo isomman GPU:n variantti kaipaisi laskennallisesti 4x enemmän muistikaistaa kuin M1:sen GPU:t. Muistikaistan tuplaaminen LPDDR:llä on helppoa, mutta nelinkertaistaminen on hankalaa. Tulisiko sieltä 8x 32bit LPDDR5 piireillä läppäri ulos + kohtuu isot on-die cache?

Sinänsä Mac Pro-piirien muistiratkaisutkin tulevat olemaan kiinnostavia, mutta ne eivät tule vaikuttamaan omaan elämääni suoraan, niin en aio niistä stressata.

Niiden tarvitsema muistikaista on myös suuri mysteeri. Etenkin tuo isomman GPU:n variantti kaipaisi laskennallisesti 4x enemmän muistikaistaa kuin M1:sen GPU:t. Muistikaistan tuplaaminen LPDDR:llä on helppoa, mutta nelinkertaistaminen on hankalaa. Tulisiko sieltä 8x 32bit LPDDR5 piireillä läppäri ulos + kohtuu isot on-die cache?

Sinänsä Mac Pro-piirien muistiratkaisutkin tulevat olemaan kiinnostavia, mutta ne eivät tule vaikuttamaan omaan elämääni suoraan, niin en aio niistä stressata.

Huhuissa on ollut myös jopa 64 gigan maksimimuistimääriä, joka ei muistaakseni onnistu noilla samoilla piireillä kuin mitä M1:n kanssa on käytetty ilman muistikanavien nelinkertaistamista. Luultavasti siis tekevät jotain ihan muuta noiden kanssa, kenties jopa joku HBM ratkaisu.Itselleni kiinnostavimmat julkaisut tulevat olemaan nuo 16 ja 32 graphic core variantit MBP:hen / iMaciin jne.

Niiden tarvitsema muistikaista on myös suuri mysteeri. Etenkin tuo isomman GPU:n variantti kaipaisi laskennallisesti 4x enemmän muistikaistaa kuin M1:sen GPU:t. Muistikaistan tuplaaminen LPDDR:llä on helppoa, mutta nelinkertaistaminen on hankalaa. Tulisiko sieltä 8x 32bit LPDDR5 piireillä läppäri ulos + kohtuu isot on-die cache?

Sinänsä Mac Pro-piirien muistiratkaisutkin tulevat olemaan kiinnostavia, mutta ne eivät tule vaikuttamaan omaan elämääni suoraan, niin en aio niistä stressata.

- Liittynyt

- 17.10.2016

- Viestejä

- 14 102

LPDDR4x:istä pitäisi olla kyllä 16GB chippejä, jolloin muistiväylän tuplaamisella + piirien koon tuplaamisella pitäisi mahdollistua 64GB.Huhuissa on ollut myös jopa 64 gigan maksimimuistimääriä, joka ei muistaakseni onnistu noilla samoilla piireillä kuin mitä M1:n kanssa on käytetty ilman muistikanavien nelinkertaistamista. Luultavasti siis tekevät jotain ihan muuta noiden kanssa, kenties jopa joku HBM ratkaisu.

Silloin kaista kuitenkin vain kaksinkertaistuisi, siinä missä compute-teho on nelinkertaistumassa. Siksi mietin LPDDR5:sia.

user9999

Platinum-jäsen

- Liittynyt

- 17.10.2016

- Viestejä

- 3 304

Tuosta Mac Ministä on huhujen mukaan tulossa kovempi versio. Lähinnä korvaisi vielä myynnissä olevan Intel Minin, johon saa 64GB muistia.

www.macrumors.com

www.macrumors.com

Apple Working on High-End Mac Mini With Additional Ports and More Powerful Chip From Next-Gen MacBook Pro

Apple is working on a high-end version of the Mac mini, featuring a more powerful Apple silicon chip and extra ports, according to Bloomberg's Mark Gurman. In a wide-reaching report, Gurman explained that Apple is developing a more powerful version of the Mac mini, positioned as a high-end...

En itse ole noin isoja siruja missään nähnyt, mutta voihan noita jossain olla. Valmistajien julkisissa katalogeissa noita LPDDR4x piirejä on muutenkin vähänlaisesti ja koko valikoima lienee vain laitevalmistajien tiedossa. LPDDR5 piirejäkään en (erittäin) nopealla selailulla löytänyt kuin 12GB siruihin asti.LPDDR4x:istä pitäisi olla kyllä 16GB chippejä, jolloin muistiväylän tuplaamisella + piirien koon tuplaamisella pitäisi mahdollistua 64GB.

Silloin kaista kuitenkin vain kaksinkertaistuisi, siinä missä compute-teho on nelinkertaistumassa. Siksi mietin LPDDR5:sia.

- Liittynyt

- 17.10.2016

- Viestejä

- 14 102

Ehkä wikipediassa vaan sekoiltiin.En itse ole noin isoja siruja missään nähnyt, mutta voihan noita jossain olla. Valmistajien julkisissa katalogeissa noita LPDDR4x piirejä on muutenkin vähänlaisesti ja koko valikoima lienee vain laitevalmistajien tiedossa. LPDDR5 piirejäkään en (erittäin) nopealla selailulla löytänyt kuin 12GB siruihin asti.

"On 9 January 2017, SK Hynix announced 8 and 16 GB LPDDR4X packages.[21][22]"

Ei löydy katalogista ainakaan. Max. 12GB piirejä on tuotannossa. View LPDDR Products Catalog [746 KB]pdf filepdf file

user9999

Platinum-jäsen

- Liittynyt

- 17.10.2016

- Viestejä

- 3 304

Testasin kanssa tuota Apple M1 QoS juttua. Tuossa on menossa Time Machine varmistus verkkolevylle. Käyttää tuohon noita Efficiency coreja. Performance corejen räpsyt on kun avannut jonkun softan.Hieman juttua Macin käyttiksen skeduloinnista. Apple M1:n koettu ripeys johtuu osittain siitä, että käyttöjärjestelmässä on priorisoitu käyttäjäkokemus ykköseksi maksimisuorituskyvyn kustannuksella (tosin miten mahtanee näkyä raskaammassa kuormituksessa). Itse olen vuosikaudet ihmetellyt Windowsin tahmaisuutta varsinkin heti bootin jälkeen, kun kaiken maailman virustutkat ja päivitystarkistukset pyörivät.

Apple’s M1 is a fast CPU—but M1 Macs feel even faster due to QoS

Howard Oakley did an excellent deep dive on M1 scheduling and performance.arstechnica.com

M1 laitteissa on myös Power Nap ominaisuus, mutta se on aina päällä eli ei saa pois. Voi tehdä nukkuessaan varmuuskopioita.

Macin käyttöopas

Tutustu macOS:n uusiin ominaisuuksiin, opi pääsemään alkuun Macisi kanssa ja käyttämään sitä muiden Apple-laitteiden kanssa ja lue lisää siitä, kuinka voit hallita tietosuojaa ja suojausta macOS:ssä.

Viimeksi muokattu:

- Liittynyt

- 16.10.2016

- Viestejä

- 2 777

Apple Announces M1 Pro and M1 Max Chips Designed for New MacBook Pro

Apple at its "Unleashed" event today announced the M1 Pro and M1 Max processors, two custom-built successor chips to the original M1 Apple silicon chip. The new MacBook Pros are powered by the new chips, which deliver up to 70% faster CPU performance than the M1. The M1 Pro features up to 10 CPU...

The M1 Pro features up to 10 CPU cores, with eight high-performance and two energy-efficient cores. In terms of graphics, the M1 Pro has a 16-core GPU, which is up to twice as powerful as the M1. It has double the width of the memory interface with up to 32GB of unified memory.

The M1 Max builds on the M1 Pro and starts with doubles memory interface, up to 400 GB/s, up to 64GB of unified memory with 57 billion transistors. It has the same 10-core CPU, but a 32-core GPU that's up to seven times faster, and is similar performance to discrete graphics while using 70% less power.

Viimeksi muokattu:

Uutiset

-

OnePlus Suomen toiminta supistuu – valmistajan puhelimet käyneet Suomessa kuitenkin kaupaksi

11.5.2026 15:51

-

HyperX esitteli uuden peliohjaimen tehokäyttäjille ja edullisemman pään pelikuulokkeet

11.5.2026 14:12

-

Live: io-techin Tekniikkapodcast (18-19/2026)

8.5.2026 11:16

-

Tietoturvatutkija: Chrome asentaa salaa 4 Gt:n Gemini Nano -tekoälymallin

8.5.2026 00:38

-

Qualcomm julkaisi uudet Snapdragon 6 Gen 5- ja 4 Gen 5 -alustat edullisempiin mobiililaitteisiin

8.5.2026 00:06

Uusimmat viestit

-

-

Hiljainen, energiatehokas ja pieni pelitietokone valmiiksi koottuna?

- Viimeisin: Tigerman82

-

-

-