- Liittynyt

- 14.10.2016

- Viestejä

- 21 879

AMD esitteli eilen Zen 2 -arkkitehtuurin ja siihen perustuvan Rome-palvelinpiirin sekä Vega 20 -grafiikkapiirin, joka tuodaan näillä näkymin vain laskentakäyttöön tarkoitettuun Radeon Instinct -tuoteperheeseen. Kaikkia piirien ja arkkitehtuurien saloja yhtiö ei vielä paljastanut, mutta jo nyt kerrotuissa tiedoissa riittää pureskeltavaa.

Zen 2

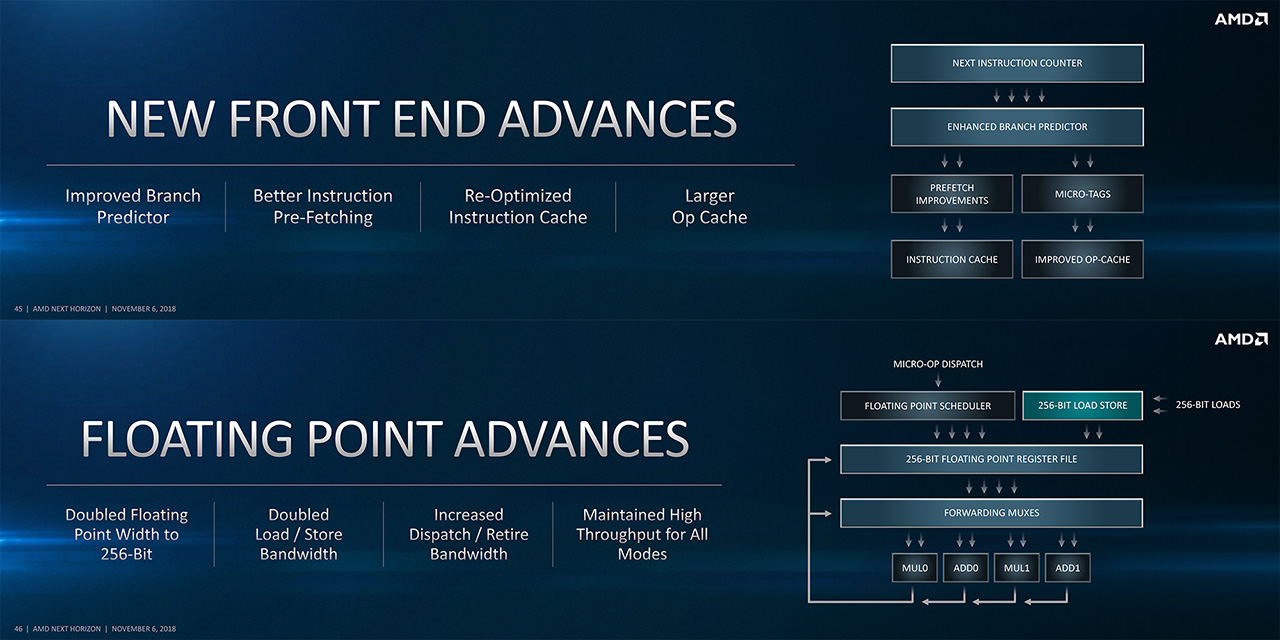

Zen 2 -arkkitehtuurin prosessoriytimiä on uudistettu monella tasolla. AMD:n mukaan parannuksia on tehty ainakin käskylaskuriin, haarautumisennustajaan, esilukuyksikköön (prefetch), käskyvälimuistiin (instruction cache) ja mikrokäskyvälimuistiin (micro op-cache). Muutosten tarkasta luonteesta kerrotaan vain mikrokäskyvälimuistin osalta, jonka kokoa on kasvatettu aiempaan nähden.

Liukulukupuolella AMD on kaksinkertaistanut yksiköiden leveyden 128 bitistä 256 bittiin. Samalla päivitettiin luonnollisesti myös lataus/tallennusyksikkö, joka on nyt niin ikään 256-bittinen. Myös lähetys/hylky-yksikön luvataan olevan aiempaa nopeampi.

Tietoturvaparannusten osalta AMD ei mennyt sen tarkempiin yksityiskohtiin, kuin kertoo Zen 2:n tarjoavan lisäsuojausta Spectre-haavoittuvuuksilta rautapäivitysten kautta. Spectren toista varianttia ei nykytiedon valossa voida korjata kuin ohjelmisto- tai käyttöjärjestelmätason päivityksillä, jotka on julkaistu jo aiemmin.

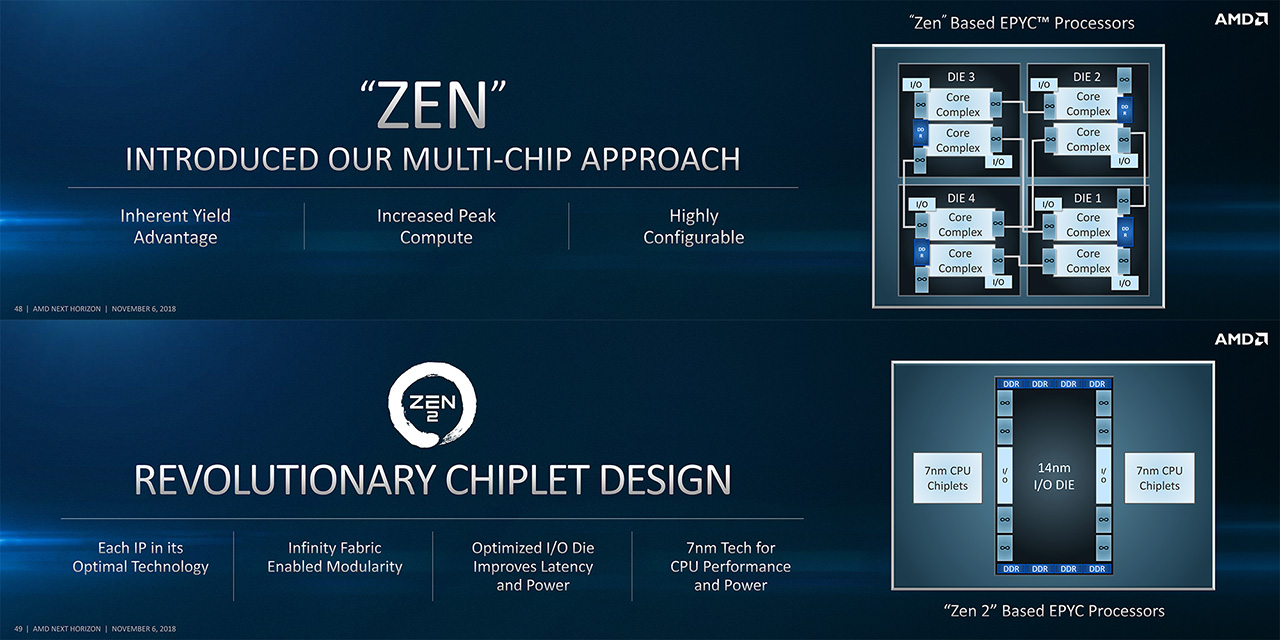

Zen 2 -arkkitehtuuri ottaa ainakin palvelinpuolella rajun askeleen pois prosessoreiden nykytrendeistä integroida enemmän ja enemmän yhteen siruun. AMD on päätynyt valmistamaan prosessoriytimet sisältävät ”pikkusirut” (chiplet) 7 nanometrin valmistusprosessilla ja irrottanut niin kutsutun uncoren erilliseksi 14 nanometrin prosessilla valmistettavaksi piiriksi.

Rome-palvelinpiirissä yhden I/O-piirin ympärillä on yhteensä kahdeksan prosessorisirua, joista kukin sisältää kaksi CCX-prosessorikompleksia eli kahdeksan prosessoriydintä. Oletettavasti prosessorisiruihin on lisäksi sijoitettu välimuistit L3-tasoon asti. Rome-prosessorissa on kahdeksan prosessorisirun myötä yhteensä 64 ydintä ja se kykenee SMT-teknologian avulla suorittamaan samanaikaisesti 128 säiettä.

I/O-sirusta AMD on paljastanut tähän mennessä sen verran, että se sisältää kahdeksan DDR4-muistiohjainta, kahdeksan Infinity Fabric -linkkiä sekä luonnollisesti prosessoreista aiemmin löytyneet I/O-linjat, kuten PCI Express, USB ja niin edelleen. AMD ei paljastanut I/O-linjojen määriä, mutta PCIe-tuki on nyt päivitetty PCI Express 4.0 -standardiin.

Zen-arkkitehtuurin tulevaisuudessa ei näillä näkymin tulla näkemään ensimmäisestä sukupolvesta tuttua +-versiota arkkitehtuureista, vaan Zen 2:n seuraaja tulee olemaan suoraan Zen 3. Zen 3:n kerrotaan olevan tällä hetkellä aikataulussaan ja se tullaan valmistamaan 7nm+-valmistusprosesilla, mikä viittaa TSMC:n EUV:ta hyödyntävään versioon 7 nanometrin prosessista. Myös Zen 4 on jo kehitteillä, mutta tulevien arkkitehtuurien aikataulusta AMD ei kertonut sen tarkemmin.

Rome-piireihin perustuvien Epyc-palvelinprosessoreiden toimitukset aloitetaan ensi vuoden alkupuolella.

Vega 20

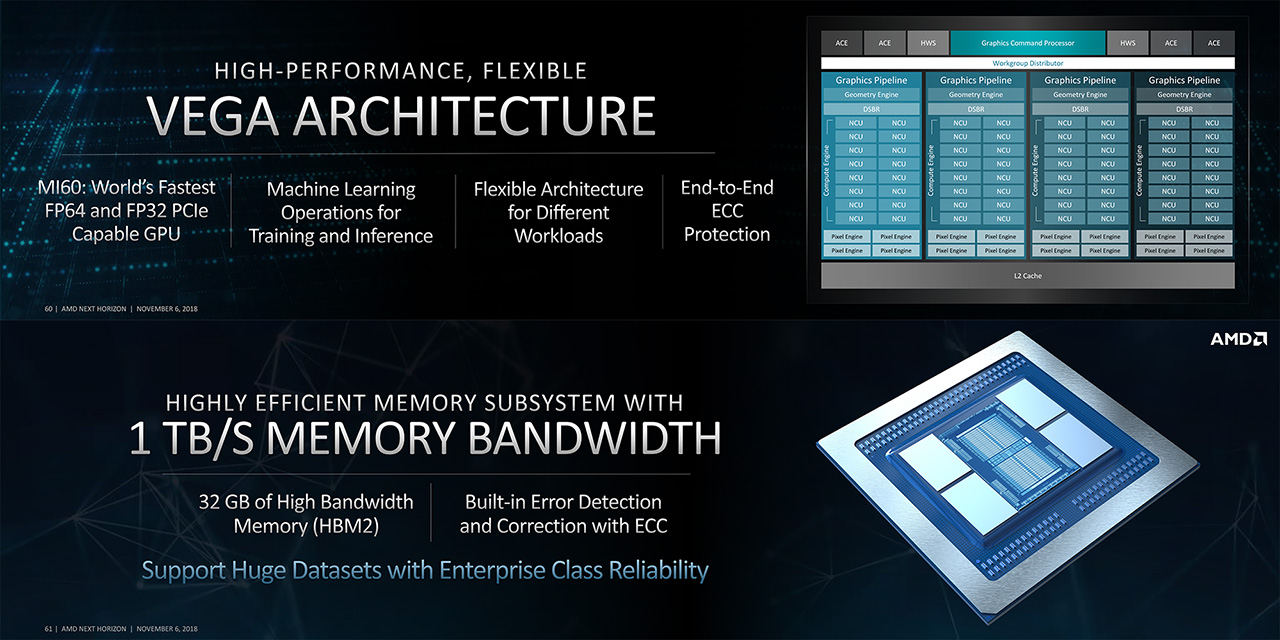

7 nanometrin valmistusprosessilla Vega 20 -grafiikkapiirin 13,2 miljardia transistoria on saatu mahdutettua 331 mm2:een. Ominaisuuksiensa osalta se on hyvin pitkälti huhujen mukainen ja Vega 10:n tapaan se sisältää edelleen esimerkiksi 64 Compute Unit -yksikköä eli 4096 stream-prosessoria. Stream-prosessoreita on kuitenkin päivitetty ja ne tarjoavat nyt ensimmäistä kertaa GCN-arkkitehtuurien historiassa sitten vuonna 2013 julkaistun Hawaii:n 1:2-suhteen suorituskykyä tuplatarkkuudella. Myös matalien tarkkuuksien tukea on paranneltu ja nopeutettu.

Huippumalli Radeon Instinct MI60 tarjoaa 300 watin TDP:llä laskentavoimaa 7,4 TFLOPSia FP64-tarkkuudella, 14,7 TFLOPSia FP32-tarkkuudella ja 29,5 TFLOPSia FP16-tarkkuudella, sekä 59 ja 118 TOPS:ia INT8- ja INT4-tarkkuuksilla. Vega 20:ssa on 4096-bittinen HBM2-muistiohjain, jonka jatkeena on 32 Gt ECC-virheenkorjausta tukevaa 2 Gbps:n HBM2-muistia, mikä tarkoittaa muistikaistan osalta teratavua sekunnissa. MI60:n rinnalle julkaistaan myös kevyempi Radeon Instinct MI50, mutta sen tarkempia tietoja ei julkistettu vielä.

AMD:n omien testien mukaan Radeon Instinct MI60 tarjoaa ResNet-50-testissä FP16-tarkkuudella noin 2,8-kertaista suorituskykyä Vega 10:een perustuvaan MI25-malliin verrattuna ja FP32-tarkkuudella lähes Tesla V100 PCIe:n tasoista suorituskykyä. SGEMM- ja DGEMM-testeissä MI60:n suorituskyky riittää Tesla V100 PCIe:n peittoamiseen pienehköllä marginaalilla.

Muita Vega 20:n uudistuksia ovat esimerkiksi PCI Express 4.0 -tuki ja Infinity Fabric -tuki näytönohjainten väliseen kommunikaatioon. PCI Express 4.0 tarjoaa prosessorin ja grafiikkapiirin välille maksimissaan 64 Gbps:n kaksisuuntaisen kaistanleveyden, kun näytönohjainten väliseen kommunikaatioon käytettävä Infinity Fabric tarjoaa kaistaa 100 Gbps. Grafiikkapiirin rautatason virtualisointi on tarjoaa kolmannen sukupolvensa myötä mahdollisuuden käyttää yhtä Radeon Instinct MI60 -näytönohjainta maksimissaan 16 virtuaalikoneen palvelemiseen ja yhdelle virtuaalikoneelle voidaan osoittaa maksimissaan kahdeksan omaa laskentakorttia.

Radeon Instinct MI60 -näytönohjaimen toimitukset aloitetaan vielä tämän vuoden puolella.

Päivitys: AMD on julkaissut virallisen videon Next Horizon -tapahtumastaan. Videolla on mittaa reilut kaksi tuntia.

Huom! Foorumiviestistä saattaa puuttua kuvagalleria tai upotettu video.

Linkki alkuperäiseen uutiseen (io-tech.fi)

Palautelomake: Raportoi kirjoitusvirheestä

Viimeksi muokattu: