- Liittynyt

- 14.10.2016

- Viestejä

- 25 069

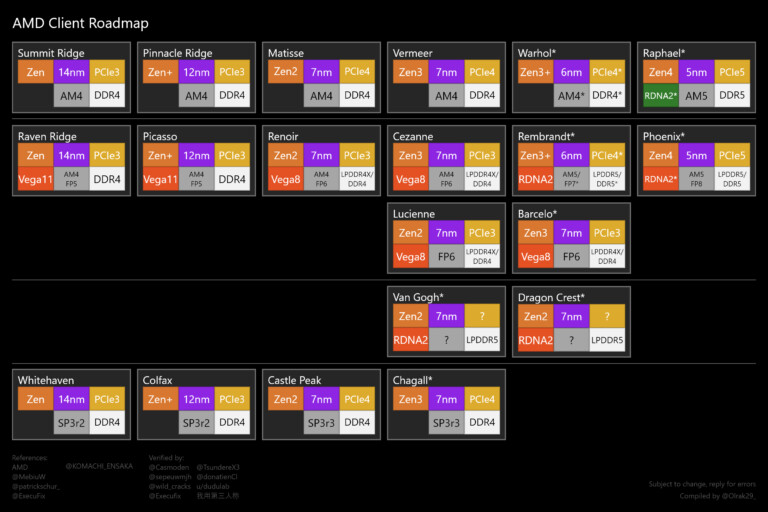

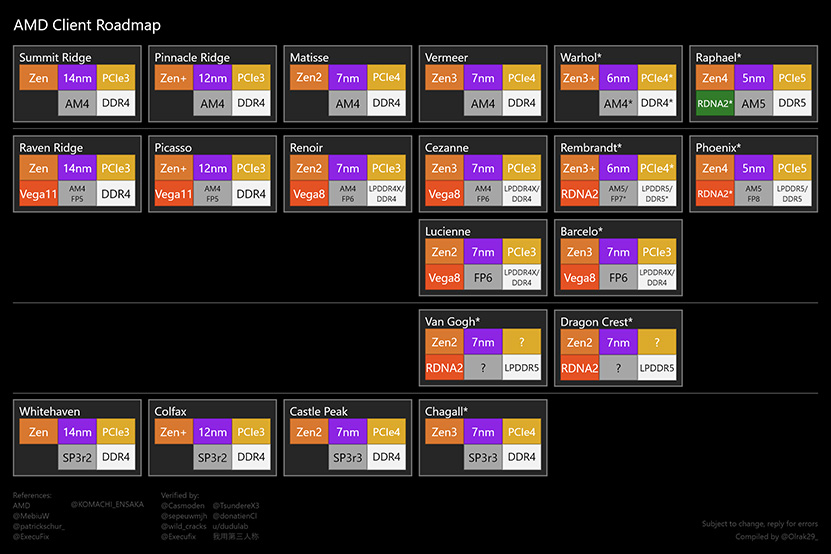

Ei me oltaisi uutisoitu siitä yli viikko sitten, ellei vuodoille joihin tuo perustuu olisi luottoaMahtaakohan tämä TPU:n julkaisema huhu pitää paikkaansa?

Huhun mukaan AM5-kantaisissa Ryzen kuluttajaprosessoreissa olisi kaikissa GPU mukana, ei siis vain OEM/läppäri APU-malleissa.

TPU arvioi, että AMD voisi 'helposti' integroida samalle kannalle sekä 8 coren CPU-chipletin, IO-sirun ja Navi 2 GPU chipletin.

Toiskohan DDR5 riittävästi suorituskykyä myös GPU:lle ilman, että CPU-puoli siitä liiemmin kärsisi?

Tokihan raskaimmat pelit pyöritettäisiin jatkossakin erillisnäytönohjaimella, mutta olisi se AMD:lle helpompaa, kun ei tarvitsisi APU-käyttöön tehdä omaa monoliittista piiriä.

Rumor: AMD Ryzen 7000 (Raphael) to Introduce Integrated GPU in Full Processor Lineup

The rumor mill keeps crushing away; in this case, regarding AMD's plans for their next-generation Zen designs. Various users have shared pieces of the same AMD roadmap, which apparently places AMD in an APU-focused landscape come their Ryzen 7000 series. we are currently on AMD's Ryzen...www.techpowerup.com

AMD:n eri vuodoista koostettu prosessori-roadmap paljastaa kaksi seuraavaa sukupolvea - io-tech.fi

Roadmapin mukaan myös perinteiset työpöytäprosessorit saavat grafiikkaohjaimen kahden sukupolven kuluttua.

Raphaelinkin tietoja vuoti jo aiemmin mutta tossa on koostettu se ja useita muitakin yksiin.

edit: Mitä noiden omaan spekulaatioon tulee, ennemmin uskoisin GPU:n olevan osa IO-sirua kuin erillinen siru