-

PikanavigaatioAjankohtaista io-tech.fi uutiset Uutisia lyhyesti Muu uutiskeskustelu io-tech.fi artikkelit io-techin Youtube-videot Palaute, tiedotukset ja arvonnat

Tietotekniikka Prosessorit, ylikellotus, emolevyt ja muistit Näytönohjaimet Tallennus Kotelot ja virtalähteet Jäähdytys Konepaketit Kannettavat tietokoneet Buildit, setupit, kotelomodifikaatiot & DIY Oheislaitteet ja muut PC-komponentit

Tekniikkakeskustelut Ongelmat Yleinen rautakeskustelu Älypuhelimet, tabletit, älykellot ja muu mobiili Viihde-elektroniikka, audio ja kamerat Elektroniikka, rakentelu ja muut DIY-projektit Internet, tietoliikenne ja tietoturva Käyttäjien omat tuotetestit

Softakeskustelut Pelit, PC-pelaaminen ja pelikonsolit Ohjelmointi, pelikehitys ja muu sovelluskehitys Yleinen ohjelmistokeskustelu Testiohjelmat ja -tulokset

Muut keskustelut Autot ja liikenne Urheilu TV- & nettisarjat, elokuvat ja musiikki Ruoka & juoma Koti ja asuminen Yleistä keskustelua Politiikka ja yhteiskunta Hyvät tarjoukset Tekniikkatarjoukset Pelitarjoukset Ruoka- ja taloustarviketarjoukset Muut tarjoukset

Kauppa-alue

Navigation

Install the app

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Huomio: This feature may not be available in some browsers.

Lisää vaihtoehtoja

Tyylin valinta

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

AMD CPU-spekulaatio (Zen6/Zen7 ...)

Mitä sitä turhaan julkaisemaan uusia malleja, kun nykyiset (kalliimmat) mallit lentävät hyllyiltä.Oli kyllä pettymys desktop käyttäjälle. Ei mitään puhetta uusista malleista esim 5700

Sitten kun ne alkavat olla hyllykamaa voidaan alkaa pohtia sitä.

- Liittynyt

- 17.10.2016

- Viestejä

- 1 434

5900 ja 5800 sentään uusia desktop malleja. Tais olla 65W tdp kuristettuja. Saa nähdä kulkeeko 5900 miten kellottamalla.

Sen lisäksi nähtävästi julkaistaan vain tray-mallina kuten esimerkiksi 3900 non-X jonka saatavuus oli mitä oli Verkkokauppa.comiin päätynyt satsi pois lukien.

www.engadget.com/amd-ryzen-7-5800-ryzen-9-5900-cpu-170006935.html

- Liittynyt

- 18.10.2016

- Viestejä

- 6 350

Reddit - Netin sydän

Huhu väittää, että AMD on lisäämässä Zen4 core compleksiin pienen apuprosessorin joka hoitaisi I/O:n tyylisiä hommia varsinaisen core complexin puolesta.

- Liittynyt

- 13.12.2016

- Viestejä

- 3 439

Siitä suolan kera huhuja. Zen4 huhujen mukaan 29% IPC parannus Zen3:een verrattuna, ja kokonaissuorituskyky jopa 40% parempi (kun huomioidaan myös boost kellot). Mutta AM5 kannalle olisi tulossa ensimmäisenä Zen3+, joka olisi hiukan parannettu Zen3 (3-4% IPC parannus?) parannetulla 7nm nodella valmistettuna.

AMD Zen 4 Reportedly Features a 29% IPC Boost Over Zen 3 | TechPowerUp

AMD Zen 4 Reportedly Features a 29% IPC Boost Over Zen 3 | TechPowerUp

- Liittynyt

- 22.10.2016

- Viestejä

- 12 908

Siitä suolan kera huhuja. Zen4 huhujen mukaan 29% IPC parannus Zen3:een verrattuna, ja kokonaissuorituskyky jopa 40% parempi (kun huomioidaan myös boost kellot). Mutta AM5 kannalle olisi tulossa ensimmäisenä Zen3+, joka olisi hiukan parannettu Zen3 (3-4% IPC parannus?) parannetulla 7nm nodella valmistettuna.

AMD Zen 4 Reportedly Features a 29% IPC Boost Over Zen 3 | TechPowerUp

Veikkaan, että tämä pätee vain numeronmurskausworkloadeilla, joissa käytetään AVX-512sta.

Tulkitsen tuota juttua siten, että AMDltä tulisi uusi IO-piiri, joka tukee DDR5sta, ja sen kanssa käytetään hiukan viilattuja (ei uutta layoutia) versioita Zen3-CCDstä. Esim korjattu joku bugi jonka takia joku aiemmin pois päältä ollut suorituskykyä parantava ominaisuus voidaan kytkeä päälle, tai joku käsky on ollut mikrokooditoteutuksena, tai aggressiivisemmat ajastukset joissain väimuisteissa tme. ja tämän yhdessä DDR5-muistin kanssa odotetaan tuovan tuon 4-7% IPC-parannuksen

Suhtaudun ehkä hiukan skeptisesti siihen että tämä voisi olla yleinen parannus normaaleilla softilla; Normaalit työpöytäsoftat ja pelit eivät ole juurikaan kaistarajoitteisia, ne voivat olla muistiVIIVErajoitteisia, eikä Zen3ssa muistaakseni ollut juurikaan sellaisia pullonkauloja/hitaita toteutuksia käskyille jotka vihjaisivat siihen että ne on workaroundeja bugeille. Tosin yksi zen2ssa ollut IPCtä parantava optimointi kyllä puuttui zen3sta, voi olla että se on ollut rikki ja on saatu korjattua ja tuodaan takaisin.

Viimeksi muokattu:

- Liittynyt

- 22.10.2016

- Viestejä

- 12 908

Reddit - Netin sydän

www.reddit.com

Huhu väittää, että AMD on lisäämässä Zen4 core compleksiin pienen apuprosessorin joka hoitaisi I/O:n tyylisiä hommia varsinaisen core complexin puolesta.

Siellä on jo vaikka kuinka monta pientä apuprosessoria, esim.

AMD Platform Security Processor - Wikipedia

Tuossa parentissa on muuten vähän ristiriitainen nimieäminen, "mini-prosessor" joka on pienempi kuin "microprocessor"

Ja Underfox on aikaisemminkin tulkinnut asioita päin mäntyä. Tyyppi on hyvä käyttämään hakua patenteille, mutta huonompi tulkitsemaan/ymmärtämään, mitä ne patentit tarkoittaa.

- Liittynyt

- 12.12.2016

- Viestejä

- 4 989

Suhtaudun ehkä hiukan skeptisesti siihen että tämä voisi olla yleinen parannus normaaleilla softilla; Normaalit työpöytäsoftat ja pelit eivät ole juurikaan kaistarajoitteisia, ne voivat olla muistiVIIVErajoitteisia, eikä Zen3ssa muistaakseni ollut juurikaan sellaisia pullonkauloja/hitaita toteutuksia käskyille jotka vihjaisivat siihen että ne on workaroundeja bugeille. Tosin yksi zen2ssa ollut IPCtä parantava optimointi kyllä puuttui zen3sta, voi olla että se on ollut rikki ja on saatu korjattua ja tuodaan takaisin.

Sillä, että uusi IO-piiri mahdollistaisi infinity fabricin toiminnan 1:1 suhteella muistikellojen kanssa edes DDR5 perusnopeudella 5600Mhz saavutettaisiin aika paljon suorituskykyä.

Tällä hetkellä saadaan aina lisää suorituskykyä IF:n nopeutta nostamalla aina sinne 2Ghz asti (=4000Mhz efektiivinen DDR-nopeus) minne se menee.

Toki sen nosto ei loputtomiin auta, mutta vakiotesteissä varmasti mukavasti saisi Zen 3 lisäpotkua kun selkeästi usein pullonkaulana oleva väylä saisi 50% lisää vauhtia

Ton lisäksi jos saadaan muualta vähän lisää potkua niin hyvältä näyttäisi

E: virransyötöstä, piirilevysuunnittelusta ja ylikellotuksesta ihan hyvin perillä oleva Buildzoid tosin on spekuloinut, että piirien sijaan se voi olla se piirilevy jolla piirit istuvat olla IF:n maksimikellojen suhteen rajoittava tekijä. Eli voi olla että siihen pitäisi vetää lisää tai parempia vetoja piirien väliin, jos halutaan lisää IF-kelloja. Tämä kuitenkin on spekulaatiota ja ongelma voi hyvinkin olla IO-piiri

- Liittynyt

- 20.10.2016

- Viestejä

- 5 235

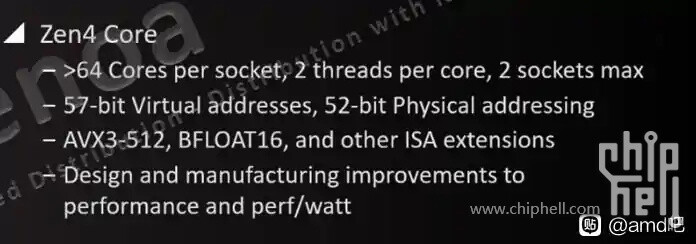

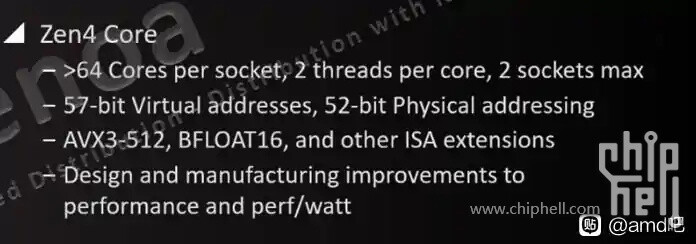

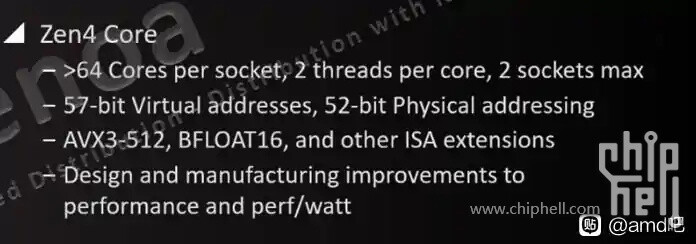

Zen 4 (EPYC Genoa) vuotoja:

wccftech.com

- 96-cores (192 threads) (max 12 chiplettiä / CPU vs 8/CPU @Zen3)

wccftech.com

- 96-cores (192 threads) (max 12 chiplettiä / CPU vs 8/CPU @Zen3)

- 12-channel DDR5-5200

- 128 PCIe 5.0 lanes (160 for 2P)

- 320W TDP (cTDP 400W)

- SP5 (LGA-6096) socket

Artikkelin ja oheisen kuvan mukaan olisi edelleen 8 corea/chiplet, mikä ei kuullosta aivan uskottavalta.

AMD on lupaillut enemmän coreja /chiplet, kun siirrytään 5mn prosessille.

Tokihan chipletit voisivat olla pienempiä, jolloin niitä saataisiin enemmän yhdelle kannalle (ja uusi SP5 -kanta on fyysisestikin suurempi), mutta tämä tarkoittaisi sitä, että kuluttajapuolella (AM5) jäätäisiin edelleen max. 16 coren prosessoreihin.

AMD EPYC Genoa CPU Platform Detailed - Up To 96 Zen 4 Cores, 192 Threads, 12-Channel DDR5-5200, 128 PCIe Gen 5 Lanes, SP5 'LGA 6096' Socket

Details of AMD's next-generation EPYC Genoa Server CPU lineup which will feature the Zen 4 core architecture have leaked out.

- 12-channel DDR5-5200

- 128 PCIe 5.0 lanes (160 for 2P)

- 320W TDP (cTDP 400W)

- SP5 (LGA-6096) socket

Artikkelin ja oheisen kuvan mukaan olisi edelleen 8 corea/chiplet, mikä ei kuullosta aivan uskottavalta.

AMD on lupaillut enemmän coreja /chiplet, kun siirrytään 5mn prosessille.

Tokihan chipletit voisivat olla pienempiä, jolloin niitä saataisiin enemmän yhdelle kannalle (ja uusi SP5 -kanta on fyysisestikin suurempi), mutta tämä tarkoittaisi sitä, että kuluttajapuolella (AM5) jäätäisiin edelleen max. 16 coren prosessoreihin.

- Liittynyt

- 22.10.2016

- Viestejä

- 12 908

Zen 4 (EPYC Genoa) vuotoja:

- 96-cores (192 threads) (max 12 chiplettiä / CPU vs 8/CPU @Zen3)

AMD EPYC Genoa CPU Platform Detailed - Up To 96 Zen 4 Cores, 192 Threads, 12-Channel DDR5-5200, 128 PCIe Gen 5 Lanes, SP5 'LGA 6096' Socket

Details of AMD's next-generation EPYC Genoa Server CPU lineup which will feature the Zen 4 core architecture have leaked out.wccftech.com

- 12-channel DDR5-5200

- 128 PCIe 5.0 lanes (160 for 2P)

- 320W TDP (cTDP 400W)

- SP5 (LGA-6096) socket

Artikkelin ja oheisen kuvan mukaan olisi edelleen 8 corea/chiplet, mikä ei kuullosta aivan uskottavalta.

AMD on lupaillut enemmän coreja /chiplet, kun siirrytään 5mn prosessille.

Onko lupaillut? Onko viitettä näihin lupauksiin?

Vai onko porukka vaan spekuloinut että niitä tulee?

Itse en muista tällaista lupausta nähneeni.

Tokihan chipletit voisivat olla pienempiä, jolloin niitä saataisiin enemmän yhdelle kannalle (ja uusi SP5 -kanta on fyysisestikin suurempi), mutta tämä tarkoittaisi sitä, että kuluttajapuolella (AM5) jäätäisiin edelleen max. 16 coren prosessoreihin.

Eikä tarkoita; Mikään ei estä tuomasta markkinoille kuluttajapiiriä kolmella CCDllä. Kun kanta menee joka tapauksessa uusiksi, se on helppo suunnitella siten että tilaa niille kolmelle CCDlle riittää, ja kuluttajakannat(AM5)-huippumallit voisi 24 ytimellä.

Mielestäni tämä on täysin uskottavaa;

TSMCn "5nm" prosessi on vain n. 1.4x-1.6x tiheämpi kuin TSMCn N7/N7P-prosessi (SRAM eli välimuistit n. 1.4x, puhdas logiikka n. 1.6, koko ydin L1-välimuisteineen jne n. 1.5x), ja jos siellä esim. SIMD-datapolku levennetään 512 bittiin, tarkoittaa se helposti selvästi lisää kokoa ytimelle. Tähän päälle kaikki pikkuviilaukset jolla ytimestä viilataan lisää IPCtä (kuten esimerkiksi suuremmat haarautumisenennustuksen kirjanpitotaulukot, mahdollisesti suurempi micro-op-välimuisti, hiukan enemmän fyysisiä rekistereitä ja suurempia puskureita monissa paikoissa yms. yms.)

Käytännössä yksi Zen4-ydin on helposti pinta-alaltaan yli 80% Zen3-ytimestä vaikka valmistustekniikka onkin uudempi, ja sama määrä L3-kakkua n 72% Zen3n L3-kakun koosta. Eli koko 8 ytimen CCD josta n. puolet on L3-kakkua ja puolet ytimiä veisi helposti n. 77% Zen3-CCDn pinta-alasta eli n. 84% Zen2-CCDn pinta-alasta.

"5nm" prosessi on jälleen (ainakin aluksi) pinta-alaa kohden myös selvästi kalliimpi kuin "7nm" joten tällainen 8 ytimen CCD olisi valmistuskustannuksiltaan melko samaa luokkaa kuin zen3-ccd, kun taas suurempi (10 tai 12 ytimen) CCD olisi selvästi kalliimpi valmistaa, ja heikentäisi katteita erityisesti esim. 6-ydin-malleista (jotka edelleen taitaa olla ne myydyimmät mallit).

Viimeksi muokattu:

- Liittynyt

- 17.10.2016

- Viestejä

- 2 011

Onko lupaillut? Onko viitettä näihin lupauksiin?

Vai onko porukka vaan spekuloinut että niitä tulee?

Itse en muista tällaista lupausta nähneeni.

Eikä tarkoita; Mikään ei estä tuomasta markkinoille kuluttajapiiriä kolmella CCDllä. Kun kanta menee joka tapauksessa uusiksi, se on helppo suunnitella siten että tilaa niille kolmelle CCDlle riittää, ja kuluttajakannat(AM5)-huippumallit voisi 24 ytimellä.

Mielestäni tämä on täysin uskottavaa;

TSMCn "5nm" prosessi on vain n. 1.4x-1.6x tiheämpi kuin TSMCn N7/N7P-prosessi (SRAM eli välimuistit n. 1.4x, puhdas logiikka n. 1.6, koko ydin L1-välimuisteineen jne n. 1.5x), ja jos siellä esim. SIMD-datapolku levennetään 512 bittiin, tarkoittaa se helposti selvästi lisää kokoa ytimelle. Tähän päälle kaikki pikkuviilaukset jolla ytimestä viilataan lisää IPCtä (kuten esimerkiksi suuremmat haarautumisenennustuksen kirjanpitoteulukot, mahdollisesti suurempi micro-op-välimuisti, hiukan enemmän fyysisiä rekiseritä ja suurempia puskureita monissa paikoissa yms. yms.)

Käytännössä yksi Zen4-ydin on helposti pinta-alaltaan yli 80% Zen3-ytimestä vaikka valmistustekniikka onkin uudempi, ja sama määrä L3-kakkua n 72% Zen3n L3-kakun koosta. Eli koko 8 ytimen CCD josta n. puolet on L3-kakkua ja puolet ytimiä veisi helposti n. 77% Zen3-CCDn pinta-alasta eli n. 84% Zen2-CCDn pinta-alasta.

"5nm" prosessi on jälleen (ainakin aluksi) pinta-alaa kohden myös selvästi kalliimpi kuin "7nm" joten tällainen 8 ytimen CCD olisi valmistuskustannuksiltaan melko samaa luokkaa kuin zen3-ccd, kun taas suurempi (10 tai 12 ytimen) CCD olisi selvästi kalliimpi valmistaa, ja heikentäisi katteita erityisesti esim. 6-ydin-malleista (jotka edelleen taitaa olla ne myydyimmät mallit).

Tekisi mieli vähän spekuloida, että tulisiko perinteinen erotus serveri ja työpöytä prossuihin takaisin (lähitulevaisuudessa), vai onko saannoissa niin kova etu chiplettien kanssa, että kannattaa ottaa muistiviiveissä takkiin.

- Liittynyt

- 20.10.2016

- Viestejä

- 5 235

No, ei AMD ole tarkkaan ottaen luvannut, että tulee enemmän coreja / chiplet. Tosin on luvannut, että enemmän coreja tulee (Lisa Su CES 2021). Joten tuo enemmän CCD:tä/kanta voi olla aivan yhtä potentiaalinen vaihtoehto.Onko lupaillut? Onko viitettä näihin lupauksiin?

Vai onko porukka vaan spekuloinut että niitä tulee?

Itse en muista tällaista lupausta nähneeni.

Eikä tarkoita; Mikään ei estä tuomasta markkinoille kuluttajapiiriä kolmella CCDllä. Kun kanta menee joka tapauksessa uusiksi, se on helppo suunnitella siten että tilaa niille kolmelle CCDlle riittää, ja kuluttajakannat(AM5)-huippumallit voisi 24 ytimellä.

Mielestäni tämä on täysin uskottavaa;

TSMCn "5nm" prosessi on vain n. 1.4x-1.6x tiheämpi kuin TSMCn N7/N7P-prosessi (SRAM eli välimuistit n. 1.4x, puhdas logiikka n. 1.6, koko ydin L1-välimuisteineen jne n. 1.5x), ja jos siellä esim. SIMD-datapolku levennetään 512 bittiin, tarkoittaa se helposti selvästi lisää kokoa ytimelle. Tähän päälle kaikki pikkuviilaukset jolla ytimestä viilataan lisää IPCtä (kuten esimerkiksi suuremmat haarautumisenennustuksen kirjanpitotaulukot, mahdollisesti suurempi micro-op-välimuisti, hiukan enemmän fyysisiä rekistereitä ja suurempia puskureita monissa paikoissa yms. yms.)

Käytännössä yksi Zen4-ydin on helposti pinta-alaltaan yli 80% Zen3-ytimestä vaikka valmistustekniikka onkin uudempi, ja sama määrä L3-kakkua n 72% Zen3n L3-kakun koosta. Eli koko 8 ytimen CCD josta n. puolet on L3-kakkua ja puolet ytimiä veisi helposti n. 77% Zen3-CCDn pinta-alasta eli n. 84% Zen2-CCDn pinta-alasta.

"5nm" prosessi on jälleen (ainakin aluksi) pinta-alaa kohden myös selvästi kalliimpi kuin "7nm" joten tällainen 8 ytimen CCD olisi valmistuskustannuksiltaan melko samaa luokkaa kuin zen3-ccd, kun taas suurempi (10 tai 12 ytimen) CCD olisi selvästi kalliimpi valmistaa, ja heikentäisi katteita erityisesti esim. 6-ydin-malleista (jotka edelleen taitaa olla ne myydyimmät mallit).

AMD CEO Lisa Su talks core counts, console launches, and Apple relationship

During CES 2021, AMD CEO Lisa Su spoke with a group of journalists about her views on processor core counts, console launches, and Apple.

There will be more core counts in the future. I would not say that somehow 16-core and 64-core are the limits. They will come as we scale other parts of the system as well.

...

Tosin (AM5) I/O-piirin Infinity Fabricin kapasiteettia jouduttaisiin kaiketi lisäämään 3 CCD:n tarpeita varten, jolloin siitä jäisi yhden ja kahden CCD:n tapauksessa aika iso osa hyödyntämättä.

Tokihan se I/O-piiri menee joka tapauksessa uusiksi DDR5 / PCIe 5.0:n myötäkin.

- Liittynyt

- 20.10.2016

- Viestejä

- 5 235

Uusien huhujen mukaan Zen4 tukee AVX-512:a

www.techpowerup.com

www.techpowerup.com

AMD "Zen 4" Microarchitecture to Support AVX-512

The next-generation "Zen 4" CPU microarchitecture powering AMD's 4th Gen EPYC "Genoa" enterprise processors, will support 512-bit AVX instruction sets, according to an alleged company slide leaked to the web on the ChipHell forums. The slide references "AVX3-512" support in addition to BFloat16...

- Liittynyt

- 18.10.2016

- Viestejä

- 6 350

Jos tuo on totta ja nopeus edes ok tasolla, niin Intelin on syytä rukoilla, että AMD ei onnistu kaivamaan jostain lisää piirituotantokapasiteettia. Muuten käy niin, että AMD juoksee ympyrää Intelin nopeimpien ympärillä ja se ei mahda sille mitäänUusien huhujen mukaan Zen4 tukee AVX-512:a

AMD "Zen 4" Microarchitecture to Support AVX-512

The next-generation "Zen 4" CPU microarchitecture powering AMD's 4th Gen EPYC "Genoa" enterprise processors, will support 512-bit AVX instruction sets, according to an alleged company slide leaked to the web on the ChipHell forums. The slide references "AVX3-512" support in addition to BFloat16...www.techpowerup.com

Ei se AVX-512 automaattisesti tee niistä nopeampia. Pitäisi tietää myös montako FMA-yksikkö niissä on.

Intelin puolellahan Tiger Lake ja Rocket Lake on yhdellä FMA-yksiköllä ja Cascade Lake kahdella yksiköllä, paitsi Xeon Silver ja Bronse on yhdellä yksiköllä. Käytännössähän tämä näkyy siinä, että HPC puolella neuvotaan olemaan ostamatta Xeon Silver ja Bronse kokoonpanoja, koska ne ovat tuhnuja juuri tuon yhden FMA-yksikön takia.

Vertailuksi Zen2/3 on AVX2 kahdella FMA-yksiköllä, joilla saadaan vastaava suorituskyky kuin AVX-512 yhdellä FMA-yksiköllä esim. matriisi-matriisi kertolaskussa. Lisäksi koska FMA-yksiköitä on kaksi, niin voidaan tehdä kaksi erillistä muistilatausta kellojaksossa, jota voidaan käyttää hyväksi koodia kirjoittaessa.

Toki AVX-512 sisältää käskyja, joita ei ole AVX2:ssa, jolloin toki saadaan lisää nopeutta.

Intelin puolellahan Tiger Lake ja Rocket Lake on yhdellä FMA-yksiköllä ja Cascade Lake kahdella yksiköllä, paitsi Xeon Silver ja Bronse on yhdellä yksiköllä. Käytännössähän tämä näkyy siinä, että HPC puolella neuvotaan olemaan ostamatta Xeon Silver ja Bronse kokoonpanoja, koska ne ovat tuhnuja juuri tuon yhden FMA-yksikön takia.

Vertailuksi Zen2/3 on AVX2 kahdella FMA-yksiköllä, joilla saadaan vastaava suorituskyky kuin AVX-512 yhdellä FMA-yksiköllä esim. matriisi-matriisi kertolaskussa. Lisäksi koska FMA-yksiköitä on kaksi, niin voidaan tehdä kaksi erillistä muistilatausta kellojaksossa, jota voidaan käyttää hyväksi koodia kirjoittaessa.

Toki AVX-512 sisältää käskyja, joita ei ole AVX2:ssa, jolloin toki saadaan lisää nopeutta.

- Liittynyt

- 18.10.2016

- Viestejä

- 6 350

Juu, ei teekään. AMD on jo nyt useimmissa kuormissa nopeampi ja tuollainen poistaisi ne loputkin käyttökohteet, johon Intel on ollut nopeampiEi se AVX-512 automaattisesti tee niistä nopeampia. Pitäisi tietää myös montako FMA-yksikkö niissä on.

Intelin puolellahan Tiger Lake ja Rocket Lake on yhdellä FMA-yksiköllä ja Cascade Lake kahdella yksiköllä, paitsi Xeon Silver ja Bronse on yhdellä yksiköllä. Käytännössähän tämä näkyy siinä, että HPC puolella neuvotaan olemaan ostamatta Xeon Silver ja Bronse kokoonpanoja, koska ne ovat tuhnuja juuri tuon yhden FMA-yksikön takia.

Vertailuksi Zen2/3 on AVX2 kahdella FMA-yksiköllä, joilla saadaan vastaava suorituskyky kuin AVX-512 yhdellä FMA-yksiköllä esim. matriisi-matriisi kertolaskussa. Lisäksi koska FMA-yksiköitä on kaksi, niin voidaan tehdä kaksi erillistä muistilatausta kellojaksossa, jota voidaan käyttää hyväksi koodia kirjoittaessa.

Toki AVX-512 sisältää käskyja, joita ei ole AVX2:ssa, jolloin toki saadaan lisää nopeutta.

mRkukov

Hrrrr...

- Liittynyt

- 17.10.2016

- Viestejä

- 8 120

Cipleteillä saadaan paljon paremmat saannot uusimmista ja heikompitasoisista valmistusprosesseista. Vaikka piipinta-ala olisi sama tais isompi niin pienemmissä palasissa saadaan enemmän toimivaa piiriä käyttöön. Uskoisin että chipleteistä ei olla ihan hetkeen luopumassa.Tekisi mieli vähän spekuloida, että tulisiko perinteinen erotus serveri ja työpöytä prossuihin takaisin (lähitulevaisuudessa), vai onko saannoissa niin kova etu chiplettien kanssa, että kannattaa ottaa muistiviiveissä takkiin.

Lisäksi jotain pitää valmistaa global founderilla. En tosin muista kuinka kauan.Cipleteillä saadaan paljon paremmat saannot uusimmista ja heikompitasoisista valmistusprosesseista. Vaikka piipinta-ala olisi sama tais isompi niin pienemmissä palasissa saadaan enemmän toimivaa piiriä käyttöön. Uskoisin että chipleteistä ei olla ihan hetkeen luopumassa.

- Liittynyt

- 12.12.2016

- Viestejä

- 4 989

Uskoisin että chipleteistä ei olla ihan hetkeen luopumassa.

En minäkään, mutta kyllähän AMD nytkin tuottaa monoliittisiä piirejä APU-prossujen muodossa. Pienoinen ongelma toki AMD:n kannalta on se, että se ajoi ydinkilvassa jo 16 ytimeen asti työpöydällä ja siinä mentäisiin melko hankalassa kokoluokassa monoliittisella piirillä.

Toisaalta DDR5 aikakausi mahdollistaa työpöydän ja HEDT-alustojen uusjaon, kun molemmat alustat menevät kuitenkin uusiksi.

Eli nyt kun AMD on tehnyt per sukupolvi:

-chiplet ytimet

-APU monoliittinen (todellisuudessa näitä on tehty nyt useampikin vedos per prossusukupolvi)

-pieni IO-piiri

-iso IO-piiri

Niin suunniteltavien piirien määrä ei muuttuisi kuin korvattaisiin pieni IO-piiri monoliittisellä prossulla. Suunnittelun kompleksisuus varmasti nousee, mutta AMD:n taloustilannekin on viime vuodet ollut paljon parempi kuin ennen Ryzeneitä, joten R&D budjettiakin pitäisi nyt olla

Tosin 16 ytimien työpöytäprossu ois vähän niin kuin tuotava kuitenkin seuraavaankin sukupolveen, kun Intelin Alder Lake suunnitelmat tiedetään. Eli eiköhän chipleteillä mennä

Lisäksi jotain pitää valmistaa global founderilla. En tosin muista kuinka kauan.

Tälle vuodelle on sopimus tarkoista ehdoista, mutta vielä kolme vuotta pitäisi tehdä JOTAIN, mutta mitä ja kuinka paljon niin siitä ei ole vielä sopimusta

- Liittynyt

- 17.10.2016

- Viestejä

- 2 011

...

Tälle vuodelle on sopimus tarkoista ehdoista, mutta vielä kolme vuotta pitäisi tehdä JOTAIN, mutta mitä ja kuinka paljon niin siitä ei ole vielä sopimusta

Voiskohan niitä xilinxin vehkeitä tehdä, sehän on pian AMDtä...

AMD:llä on jo se monoliittinen prossu APU:n muodossa. Pienillä ydinmäärillä sitä on ihan järkevää myydä myös työpöytäprosessoriksi. Mutta kun mennään hieman isompiin ydinmääriin, niin tuo Chiplet-malli toimii ihan hyvin. Suuremmat latenssit eivät näy menoa juuri haittaavan.En minäkään, mutta kyllähän AMD nytkin tuottaa monoliittisiä piirejä APU-prossujen muodossa. Pienoinen ongelma toki AMD:n kannalta on se, että se ajoi ydinkilvassa jo 16 ytimeen asti työpöydällä ja siinä mentäisiin melko hankalassa kokoluokassa monoliittisella piirillä.

Toisaalta DDR5 aikakausi mahdollistaa työpöydän ja HEDT-alustojen uusjaon, kun molemmat alustat menevät kuitenkin uusiksi.

Eli nyt kun AMD on tehnyt per sukupolvi:

-chiplet ytimet

-APU monoliittinen (todellisuudessa näitä on tehty nyt useampikin vedos per prossusukupolvi)

-pieni IO-piiri

-iso IO-piiri

Niin suunniteltavien piirien määrä ei muuttuisi kuin korvattaisiin pieni IO-piiri monoliittisellä prossulla. Suunnittelun kompleksisuus varmasti nousee, mutta AMD:n taloustilannekin on viime vuodet ollut paljon parempi kuin ennen Ryzeneitä, joten R&D budjettiakin pitäisi nyt olla

Mitä tulee noihin palvelinprosessoreihin, niin mikäli nuo huhut EPYC Genoasta pitävät paikkansa, on odotettavissa kaksi eri palvelinpuolelle tehtyä IO-piiriä: Ei ole mitään järkeä käyttää tuota 96 ytimen prosessoreissa tarvittavaa suurta ja monimutkaista IO-piiriä pienempien ydinmäärien palvelinprosessoreissa.

Ja muutoinkin tuo huhujen uusi SP5-socket on liian kallis ja suuri halvemman pään palvelinprosessoreille. Jokin "SP5-lite"-socket on varmasti myös tulollaan - esimerkiksi 8 muistikanavan tuella 12 sijaan. DDR5-kammoissahan on kaksi kanavaa per kampa, joten huhuttu SP5 socket vaatisi 6 kampaa täyteen muistinopeuteen.

Ei ihan noin mene kuitenkaan (?). Yhtä muistikanavaa käskytetään hieman samaan tapaan kuin rank interleavattua ddr4 kampaparia. 12 kanavainen muistiohjain haluaa kuitenkin edelleen 12 kampaa toimiakseen täydellä nopeudella.DDR5-kammoissahan on kaksi kanavaa per kampa, joten huhuttu SP5 socket vaatisi 6 kampaa täyteen muistinopeuteen.

Voin toki väärässäkin olla.

edit: DDR5 speksissä tosiaan puhutaan että kammoissa on kaksi kanavaa. Olisi kuitenkin vähintään outoa jos AMD laskisi uudella kannalla maksimimuistimäärää alemmas kuin nykyisillä malleilla. Luulenkin siis että tässä on joku kommunikointiin liittyvä ongelma ja joko kanavana pidetään ddr4 kanavan kokoista yksikköä, tai sitten kanavilla tarkoitetaan minimimäärää muistikampoja maksiminopeuteen.

Viimeksi muokattu:

- Liittynyt

- 20.10.2016

- Viestejä

- 5 235

Alkavat jo emolevyn fyysiset mitat tulla kohta vastaan:Ei ihan noin mene kuitenkaan (?). Yhtä muistikanavaa käskytetään hieman samaan tapaan kuin rank interleavattua ddr4 kampaparia. 12 kanavainen muistiohjain haluaa kuitenkin edelleen 12 kampaa toimiakseen täydellä nopeudella.

Voin toki väärässäkin olla.

edit: DDR5 speksissä tosiaan puhutaan että kammoissa on kaksi kanavaa. Olisi kuitenkin vähintään outoa jos AMD laskisi uudella kannalla maksimimuistimäärää alemmas kuin nykyisillä malleilla. Luulenkin siis että tässä on joku kommunikointiin liittyvä ongelma ja joko kanavana pidetään ddr4 kanavan kokoista yksikköä, tai sitten kanavilla tarkoitetaan minimimäärää muistikampoja maksiminopeuteen.

- 2P palvelinemo:

- 2x leveämpiä CPUita

- 2 DIMM/muistikanava x 12DIMM/kanava X 2 CPU = 48 DIMMiä.

Jos intel yrittää kilpailla 4P-emon kanssa, niin samaan muistiväylän leveyteen & muistikapasiteettiin/CPU tarvitaankin sitten 96 DIMMiä.

Alla olevassa kuvassa 4P emolevy ja 48 DIMM-paikkaa...

Ei se maksimimuistimäärä mihinkään ole laskemassa. DDR5-kampoja tulee aluksi ainakin 256 GB kokoisena ja nopeaan tahtiin ainakin 1 TB:n kampoina. 6 (= 12 väylää) x 2 kampaa per väylä x 1 TB tarkoittaisi jo 12 TB:n muistikapasiteettia. Jos ajatellaan asiaa toisin päin, niin se, että muistikampoja lisättäisin 12 kpl kerrallaan on aivan järjetön. Pienestäkin muistilaajennuksesta tulisi hyvin epäkäytännöllinen - puhumattakaan emolevyn rakenteesta.Ei ihan noin mene kuitenkaan (?). Yhtä muistikanavaa käskytetään hieman samaan tapaan kuin rank interleavattua ddr4 kampaparia. 12 kanavainen muistiohjain haluaa kuitenkin edelleen 12 kampaa toimiakseen täydellä nopeudella.

Voin toki väärässäkin olla.

edit: DDR5 speksissä tosiaan puhutaan että kammoissa on kaksi kanavaa. Olisi kuitenkin vähintään outoa jos AMD laskisi uudella kannalla maksimimuistimäärää alemmas kuin nykyisillä malleilla. Luulenkin siis että tässä on joku kommunikointiin liittyvä ongelma ja joko kanavana pidetään ddr4 kanavan kokoista yksikköä, tai sitten kanavilla tarkoitetaan minimimäärää muistikampoja maksiminopeuteen.

Nykyisissä EPYC-emoissa on yleensä 4 kampaa (1 kampa per väylä) tai 8 kampaa (2 kampaa per väylä) prosessorin molemmilla puolilla.

Tai sitten huhut ovat vain pielessä: Kuulostaisi loogiselta, että EPYC Genoassa olisi 16 muistiväylän muistiohjain ja kun väyliä on 2 kpl per DDR5-kampa, pysyisi kampojen määrä samana kuin nykyisin (eli 8 kpl per prosessori) yksi kampa per väylä-tapauksessa. Tuolla rakenteella ja päivänä yksi päästäisiin 8 (= 16 väylää) x 1 x 256 GB eli 2 TB:n muistikapasiteettiin ja kahden kamman per väylä tapauksessa 4 TB:n muistikapasiteettiin. 1TB:n kammoilla max 16 TB.

Viimeksi muokattu:

Eihän tossa 12 (puolikkaassa) kaistassa ole mitään järkeä, raaka tiedonsiirtonopeus on hädin tuskin parempi kuin nykyisellä kahdeksalla täysikokoisella. 4266MT/s muisteilla oltaisiin vasta samassa nopeudessa kuin nykyisillä 3200MT/s muisteilla. DDR5 serverikammat lähtenee 4800 nopeudesta liikkeelle ja tällöin yhtä ydintä kohden olisi uusilla 96 ytimisillä prossuilla n. 25% vähemmän muistikaistaa kuin 64 ytimisillä nykyprossuilla. En pidä mitenkään mahdollisena että DDR5 siirtymä sössittäisiin tuolla tavalla. Mihin edes sitä isompaa prosessorikantaa tarvittaisiin kun toi 12 (puolikasta) DDR5 muistikanavaa vie vähemmän pinnejä kuin nykyiset 8 kanavaa.Ei se maksimimuistimäärä mihinkään ole laskemassa. DDR5-kampoja tulee aluksi ainakin 256 GB kokoisena ja nopeaan tahtiin ainakin 1 TB:n kampoina. 6 muistisockettia x 2 kampaa per väylä x 1 TB tarkoittaisi jo 12 TB:n muistikapasiteettia. Jos ajatellaan asiaa toisin päin, niin se, että muistikampoja lisättäisin 12 kpl kerrallaan on aivan järjetön. Pienestäkin muistilaajennuksesta tulisi hyvin epäkäytännöllinen - puhumattakaan emolevyn rakenteesta. Nykyisissä EPYC-emoissa on yleensä 4 kampaa prosessorin molemmilla puolilla. 6 kampaa per puoli tekisi sekä muistiväylistä turhan pitkät, että emolevyn suunnittelun hyvin vaikeaksi.

Tai sitten huhut ovat vain pielessä: Kuulostaisi loogiselta, että EPYC Genoassa olisi 16 muistiväylän muistiohjain ja kun väyliä on 2 kpl per DDR5-kampa, pysyisi kampojen määrä samana kuin nykyisin (eli 8 kpl per prosessori).

Isompi prossukanta viittaa isompaan pinnimäärään ja isompi pinnimäärä useampaan muistiväylään. Myös pcie käyttöön menee varmasti osansa, mutta en ole kuullut että toi nykyinen 128 väylää olisi kovin ahdas ja pullonkaulat on usein jossain ihan muualla.

Siksi juuri huhu on todennäköisesti pielessä. 16 muistiväylää (2 väylää per kampa) kuulostaa loogisemmalta. Tällöin väylien määrä olisi sama kuin DDR4:n kanssa, kun huomioi DDR5:n väylien leveyden olevan puolet DDR4:n väylästä. Tällöin DDR-4800 nostaisi kokonaiskaistaa noin 87% verrattuna DDR4-3200:iin.Eihän tossa 12 (puolikkaassa) kaistassa ole mitään järkeä, raaka tiedonsiirtonopeus on hädin tuskin parempi kuin nykyisellä kahdeksalla täysikokoisella. 4266MT/s muisteilla oltaisiin vasta samassa nopeudessa kuin nykyisillä 3200MT/s muisteilla. DDR5 serverikammat lähtenee 4800 nopeudesta liikkeelle ja tällöin yhtä ydintä kohden olisi uusilla 96 ytimisillä prossuilla n. 25% vähemmän muistikaistaa kuin 64 ytimisillä nykyprossuilla. En pidä mitenkään mahdollisena että DDR5 siirtymä sössittäisiin tuolla tavalla. Mihin edes sitä isompaa prosessorikantaa tarvittaisiin kun toi 12 (puolikasta) DDR5 muistikanavaa vie vähemmän pinnejä kuin nykyiset 8 kanavaa.

Isompi prossukanta viittaa isompaan pinnimäärään ja isompi pinnimäärä useampaan muistiväylään. Myös pcie käyttöön menee varmasti osansa, mutta en ole kuullut että toi nykyinen 128 väylää olisi kovin ahdas ja pullonkaulat on usein jossain ihan muualla.

24 muistiväylää (2 väylää per kampa) eli muistin lisääminen 12 kampaa kerrallaan ei sekään kuulosta pätkääkään järkevältä.

Eikös se nouse tuossa vain 50%? Noh, joka tapauksessa tuolloinkaan ei ole vielä tarvetta sille huhutulle merkittävästi isommalle kannalle, sillä pinnien kokonaismäärä pysyy suht samana. Isomman kannan takia veikkaan vahvasti että muistipinnien lukumäärää nostetaan.Siksi juuri huhu on todennäköisesti pielessä. 16 muistiväylää (2 väylää per kampa) kuulostaa loogisemmalta. Tällöin väylien määrä olisi sama kuin DDR4:n kanssa, kun huomioi DDR5:n väylien leveyden olevan puolet DDR4:n väylästä. Tällöin DDR-4800 nostaisi kokonaiskaistaa noin 87% verrattuna DDR4-3200:iin.

DDR5 on muutoin tehokkaampi. Micron arvioi efektiivisen muistikaistan nousevan 87% DDR4-3200 --> DDR5-4800.Eikös se nouse tuossa vain 50%? Noh, joka tapauksessa tuolloinkaan ei ole vielä tarvetta sille huhutulle merkittävästi isommalle kannalle, sillä pinnien kokonaismäärä pysyy suht samana. Isomman kannan takia veikkaan vahvasti että muistipinnien lukumäärää nostetaan.

JEDEC finalizes DDR5 standard: Terabyte-sized DDR5-6400 modules incoming

DDR5 quadruples RAM capacity and doubles speed

- Liittynyt

- 18.10.2016

- Viestejä

- 1 613

Noinhan sen on aina pitänytkin mennä, kun julkaisusykli on 1,5 vuotta.AMD:n tuoreessa Epyc-julkkarissa kerrottiin, että Zen 4 tulee vasta 2022 puolella ulos. :|

- Liittynyt

- 22.10.2016

- Viestejä

- 12 908

AMD:n tuoreessa Epyc-julkkarissa kerrottiin, että Zen 4 tulee vasta 2022 puolella ulos. :|

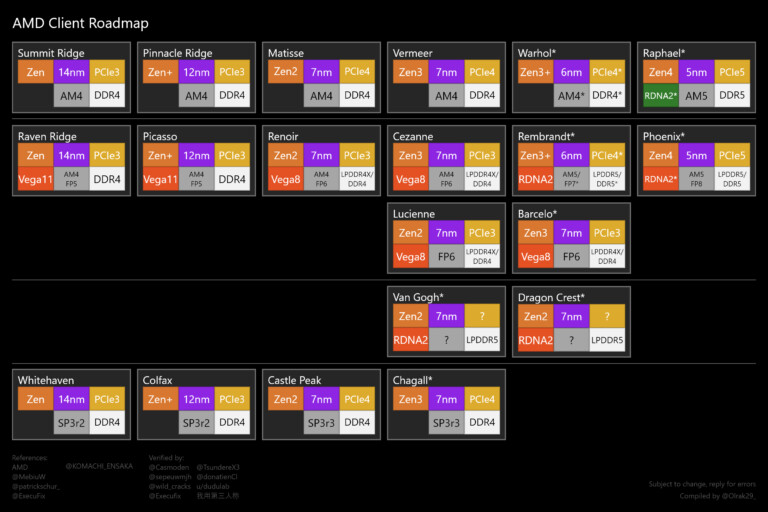

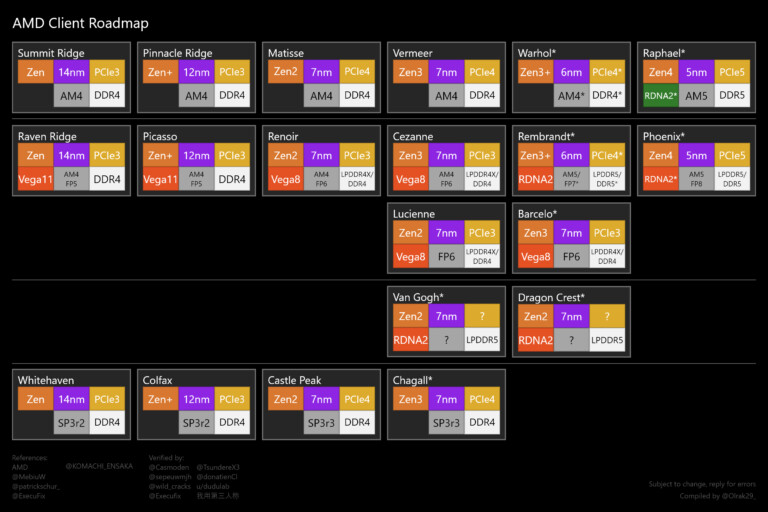

Tämän on voinut jo päätellä niistä roadmapeistä, joissa näkyy selvästi Warholia (zen3n "facelift-malllia" )tälle vuodelle.

Mutta nyt tämä on siis virallista.

Mutta siitä, mikä Warhol tarkkaanottaen on, ei kai ole aivan varmaa tietoa, tiedetään lähinnä vain, että se on Zen3 eikä zen4, eikä sitä ole tehty "5nm" tekniikalla.

Eli, avoimia kysymyksiä Warholin suhteen:

1) Tuleeko siinä uusi DDR5sta tukeva IO-piiri (jota voidaan sitten tulevaisuudessa käyttää myös zen4n kanssa) vai mennäänkö vielä vanhalla toissavuotisella/Zen2-aikaisella IO-piirillä?

2) Tehdäänkö Warhol "7nm" vai "6nm" tekniikalla?

3) Tuleeko siinä kuitenkin jotain hyvin pieniä viilauksia mikroarkkitehtuuriin?

Viimeksi muokattu:

- Liittynyt

- 17.10.2016

- Viestejä

- 10 877

AMD:n tuoreessa Epyc-julkkarissa kerrottiin, että Zen 4 tulee vasta 2022 puolella ulos. :|

Miettien että nyt on ensimmäinen neljännes jo vuodesta 2021 mennyt ja vieläkään eivät kaikki tilaajat ole saaneet Zen 3 prosessoreitaan olisi aika yllättävää jos nyt oikeasti alkaisi jo rummutus että ~6kk päästä tulisi Zen 4 uudella emolla ja DDR5 muisteilla ulos. Varsinkin kun katsoo DDR5 muistien saatavuutta kaupoista.

Eli ainakaan itse en ylläty, en edes siitä jos kävisi ilmi että Zen 4 tulisi lähellä vuoden 2022 loppua / joulumarkkinoille.

Voisi veikata, että AMD haluaisi vastata Intelin Alder Lakeen, ja tuoda samoihin aikoihin AMD:n oman DDR5-alustan eli AM5:n markkinoille. Zen 4 voisi sitten aikanaan tulla jo olemassa olevaan ekoympäristöön. Hyötynä vältettäisiin AM5+Zen4 -yhdistelmälanseerauksen mahdolliset sudenkuopat, kun voidaan keskittyä paremmin yhteen asiaan kerrallaan.

Päivitys alkaisi hiljalleen kiinnostella, mutta kiinnostus siirtyä heti kohta kuolevaan alustaan on noin 0. Voisin kuvitella monien ajattelevan samoin, mikä olisi lisäsyy pikaiselle AM5-lanseeraukselle.

Päivitys alkaisi hiljalleen kiinnostella, mutta kiinnostus siirtyä heti kohta kuolevaan alustaan on noin 0. Voisin kuvitella monien ajattelevan samoin, mikä olisi lisäsyy pikaiselle AM5-lanseeraukselle.

- Liittynyt

- 20.10.2016

- Viestejä

- 5 235

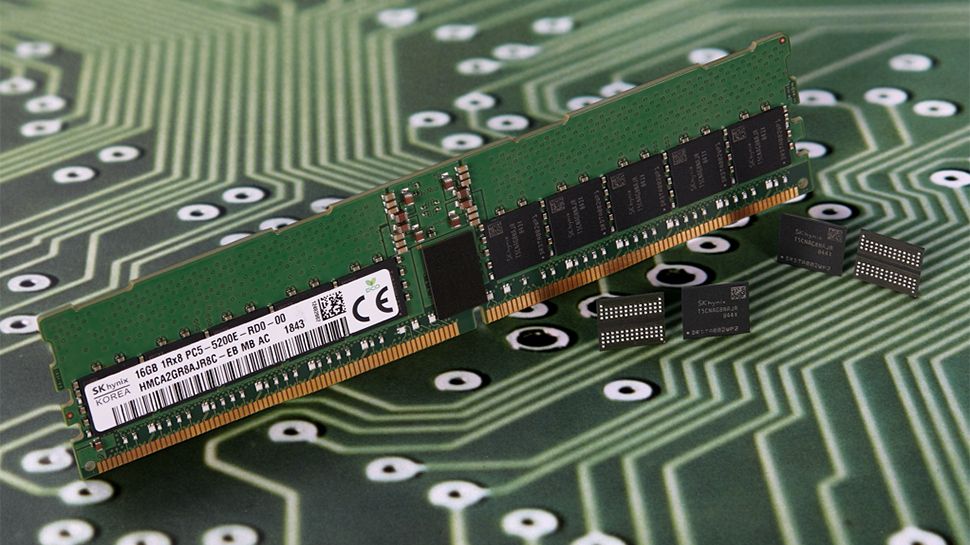

Minä veikkaisin, että ensimmäiset DDR5 -kammat maksavat (kamman muistimäärästä riippumatta) /kpl yhtä paljon kuin niitä tukevat prosessorit. Enkä tarkoita halvimpia sellaisia prosessoreita.Voisi veikata, että AMD haluaisi vastata Intelin Alder Lakeen, ja tuoda samoihin aikoihin AMD:n oman DDR5-alustan eli AM5:n markkinoille. Zen 4 voisi sitten aikanaan tulla jo olemassa olevaan ekoympäristöön. Hyötynä vältettäisiin AM5+Zen4 -yhdistelmälanseerauksen mahdolliset sudenkuopat, kun voidaan keskittyä paremmin yhteen asiaan kerrallaan.

Päivitys alkaisi hiljalleen kiinnostella, mutta kiinnostus siirtyä heti kohta kuolevaan alustaan on noin 0. Voisin kuvitella monien ajattelevan samoin, mikä olisi lisäsyy pikaiselle AM5-lanseeraukselle.

Kuluttajaemoille ei heti kannata DDR5:sta odotella ennen, kuin DDR5-piirien massatuotanto serverikäyttöön on päässyt kunnolla vauhtiin.

- Liittynyt

- 12.12.2016

- Viestejä

- 4 989

Kuluttajaemoille ei heti kannata DDR5:sta odotella ennen, kuin DDR5-piirien massatuotanto serverikäyttöön on päässyt kunnolla vauhtiin.

Alder Lake tulee tämän vuoden puolella, tämän hetken huhujen mukaan peräti jopa 6kk päästä.

Alder Lake tukee DDR5 ja tulee uudelle LGA 1700 kannalle, joka korvaa LGA 1200 alustan kuluttajamarkkinoilla.

- Liittynyt

- 20.10.2016

- Viestejä

- 5 235

Kyllä, todennäköisesti tulee.Alder Lake tulee tämän vuoden puolella, tämän hetken huhujen mukaan peräti jopa 6kk päästä.

Alder Lake tukee DDR5 ja tulee uudelle LGA 1700 kannalle, joka korvaa LGA 1200 alustan kuluttajamarkkinoilla.

Mutta kannattako odottaa sellaista Intelsteinia, joka ei itsekään tiedä, onko se Core, Atom, AVX-512 vai joku näiden kombinaatio.

DDR5:et kuitenkin maksavat järkyttävästi tuon tullessa markkinoille.

- Liittynyt

- 12.12.2016

- Viestejä

- 4 989

Kyllä, todennäköisesti tulee.

Mutta kannattako odottaa sellaista Intelsteinia, joka ei itsekään tiedä, onko se Core, Atom, AVX-512 vai joku näiden kombinaatio.

DDR5:et kuitenkin maksavat järkyttävästi tuon tullessa markkinoille.

Kohta puoleen pitäisi alkaa tulla jo ilmoitusta, että ei tule tänävuonna, jos ei ole tulossa. Normaalissa tuotejulkaisussa voi vinuttaa myöhästymisilmoitusta aika pitkälle, mutta tämä tulee nyt viimein sillä ikuisuuksia hierotulla 10nm prosessilla (toisella tai vaiko jopa kolmannella iteraatiolla siitä) ja jos tämäkään ei natsaa niin omistajille pitää kyllä hyvissä ajoin ilmoittaa asiasta.

Toimikoot vaikka keijupölyllä tai voimakristallien armosta, minua kiinnostaa pyhä kolminaisuus eli suorituskyky-virrankulutus-hinta. Muistit maksavat toki aivan varmasti paljon ja vähän päälle alkuunsa, mutta niin ne kysyntä ja tarjonta ja upotetut kustannukset toimivat.

Kuitenkin kannattaa odotella tuotetta markkinoille, mutta se on sitten eri tarina kannattaako siltä odotella millaista suorituskykyä. Itse odottelen parasta pelisuorituskykyä (minulle tärkein asia) ja kilpailullista suorituskykyä tuottavuudessa ja hinta sitten ratkaisee mikä on paras ostos syksyllä kellekin. Sitten AM5 kun tulee niin katsotaan kortit taas uusiksi, kunnes tulee seuraava Intel-julkaisu. Näin tämä sykli pyörii, ihmeitä ei kannata odotella koskaan, mutta kaikki uudet julkaisut ovat mahdollisuus.

- Liittynyt

- 20.10.2016

- Viestejä

- 4 429

Kuitenkin kannattaa odotella tuotetta markkinoille, mutta se on sitten eri tarina kannattaako siltä odotella millaista suorituskykyä. Itse odottelen parasta pelisuorituskykyä (minulle tärkein asia) ja kilpailullista suorituskykyä tuottavuudessa ja hinta sitten ratkaisee mikä on paras ostos syksyllä kellekin. Sitten AM5 kun tulee niin katsotaan kortit taas uusiksi, kunnes tulee seuraava Intel-julkaisu. Näin tämä sykli pyörii, ihmeitä ei kannata odotella koskaan, mutta kaikki uudet julkaisut ovat mahdollisuus.

Alder lake kiinnostaa siinä mielessä, että kiva nähdä viimein se 10nm työpöydällä ja nyt suunnitellun kokoisilla cacheilla, eikä leikatuilla, kuten Rocket Lakessa. Käytännössä en sitä tule kyllä ostamaan. Uuden muistisukupolven ensimmäiset kammat on aina hitaita ja ylihintaisia ja emoissa voi olla lastentauteja. Ynnä odottelisin, että littlebig tuki viilaantuu kaikessa rauhassa. 1gen on syy miksi AM5 ensimmäinen painos jää väliin. Ostohousut on siis jalassa kun on ddr5 plattojen toinen sukupolvi menossa, ihanpa sama onko se intel vai amd.

- Liittynyt

- 14.10.2016

- Viestejä

- 25 048

Onko tähän timestamppia?AMD:n tuoreessa Epyc-julkkarissa kerrottiin, että Zen 4 tulee vasta 2022 puolella ulos. :|

Tässä roadmap-osuus:Onko tähän timestamppia?

- Liittynyt

- 22.10.2016

- Viestejä

- 12 908

mutta tämä tulee nyt viimein sillä ikuisuuksia hierotulla 10nm prosessilla (toisella tai vaiko jopa kolmannella iteraatiolla siitä)

neljännellä.

Cannon lakessa oli eka iteraatio, Ice Lakessa toinen, Tiger Lakessa kolmas.

- Liittynyt

- 10.12.2020

- Viestejä

- 622

Nvidia Resizable BAR sivustolla näkyy yhteensopivuus listoilla Zen 3 Ryzen 3 5****.

Merkitään Zen 4 spekulaatioon, että siinä ehkä korjataan Zen kolmosesta löytynyt Spectre V4 kaltainen aukko. Jota ei löydy zen 1/+/2, ja jota ei luultavasti kolmoseen paikata suorituskykyongelman ja pienen riskin takia.

www.tomshardware.com

www.tomshardware.com

AMD's Zen 3 CPUs Are Susceptible To Spectre-Like Vulnerability (Updated)

Zen 3's weak spot

- Liittynyt

- 22.10.2016

- Viestejä

- 12 908

Merkitään Zen 4 spekulaatioon, että siinä ehkä korjataan Zen kolmosesta löytynyt Spectre V4 kaltainen aukko. Jota ei löydy zen 1/+/2, ja jota ei luultavasti kolmoseen paikata suorituskykyongelman ja pienen riskin takia.

AMD's Zen 3 CPUs Are Susceptible To Spectre-Like Vulnerability (Updated)

Zen 3's weak spotwww.tomshardware.com

Ei tuohon ole mahdollista tehdä mitään "korjausta" muutoin kuin kytkemällä kyseinen ominaisuus pois päältä, mikä huonontaa suorituskykyä.

Aina kun ennustetaan jotain, ennustus voi mennä pieleen. Se hanskataan oikein arkkitehtuurillisessa tilassa, mutta siitä jää aina jotain sivuvaikutuksia.

Ja tämän poiskytkeminen on jo mahdollista zen3lla.

Ja ottaen huomioon kuinka pieni riski on siihen, että tätä voidaan käyttää johonkin oikeasti käytännössä haitalliseen, se tullee zen4llakin olemaan oletuksena päällä.

Ei tuohon ole mahdollista tehdä mitään "korjausta" muutoin kuin kytkemällä kyseinen ominaisuus pois päältä, mikä huonontaa suorituskykyä

Aika näyttää voiko tai tarvitseeko tehdä mitään riskin pienentämikseksi tai eliminoimikseksi. Spectrestä ei kai ole tullut ongelmia toistaiseksi muutenkaan.

- Liittynyt

- 20.10.2016

- Viestejä

- 5 235

Mahtaakohan tämä TPU:n julkaisema huhu pitää paikkaansa?

Huhun mukaan AM5-kantaisissa Ryzen kuluttajaprosessoreissa olisi kaikissa GPU mukana, ei siis vain OEM/läppäri APU-malleissa.

TPU arvioi, että AMD voisi 'helposti' integroida samalle kannalle sekä 8 coren CPU-chipletin, IO-sirun ja Navi 2 GPU chipletin.

Toiskohan DDR5 riittävästi suorituskykyä myös GPU:lle ilman, että CPU-puoli siitä liiemmin kärsisi?

Tokihan raskaimmat pelit pyöritettäisiin jatkossakin erillisnäytönohjaimella, mutta olisi se AMD:lle helpompaa, kun ei tarvitsisi APU-käyttöön tehdä omaa monoliittista piiriä.

www.techpowerup.com

www.techpowerup.com

Huhun mukaan AM5-kantaisissa Ryzen kuluttajaprosessoreissa olisi kaikissa GPU mukana, ei siis vain OEM/läppäri APU-malleissa.

TPU arvioi, että AMD voisi 'helposti' integroida samalle kannalle sekä 8 coren CPU-chipletin, IO-sirun ja Navi 2 GPU chipletin.

Toiskohan DDR5 riittävästi suorituskykyä myös GPU:lle ilman, että CPU-puoli siitä liiemmin kärsisi?

Tokihan raskaimmat pelit pyöritettäisiin jatkossakin erillisnäytönohjaimella, mutta olisi se AMD:lle helpompaa, kun ei tarvitsisi APU-käyttöön tehdä omaa monoliittista piiriä.

Rumor: AMD Ryzen 7000 (Raphael) to Introduce Integrated GPU in Full Processor Lineup

The rumor mill keeps crushing away; in this case, regarding AMD's plans for their next-generation Zen designs. Various users have shared pieces of the same AMD roadmap, which apparently places AMD in an APU-focused landscape come their Ryzen 7000 series. we are currently on AMD's Ryzen...

Uutiset

-

Steam Controller julkaistaan 4. toukokuuta

28.4.2026 21:07

-

Microsoft lupaa käyttäjille entistä laajempaa hallintaa Windows 11 -päivityksiin

28.4.2026 20:14

-

Intelin edullisiin kannettaviin suunnattu Core 3 ensimmäisessä testivuodossa

28.4.2026 00:22

-

Live: io-techin Tekniikkapodcast (17/2026)

24.4.2026 09:12

-

Uusi artikkeli: Testissä Honor 600 Lite

24.4.2026 01:11