Selvästi et tiedä paljon aikaa vie yhden prossun testaaminen nykyisyydelläänkin?

Saatika että alan BIOSia päivittämään vanhemmaksi ja windows päivityksiä poistelemaan.

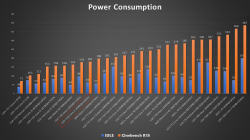

Kun nykyisyydelläänkin eka pitää löytää vakaat max kellot ja siihen menee jo prossusta/alustasta riippuen tunnista lähemmäs 6 tuntiin.

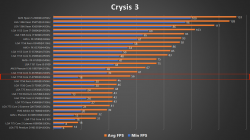

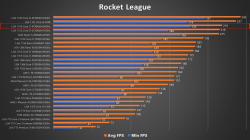

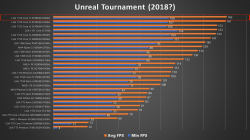

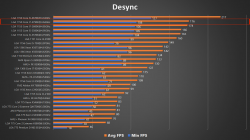

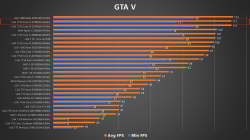

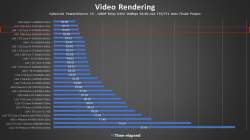

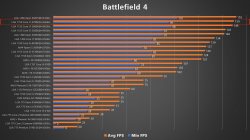

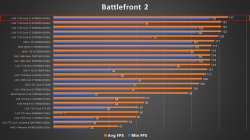

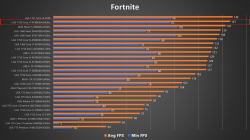

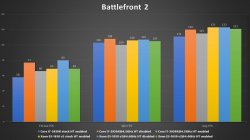

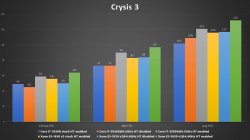

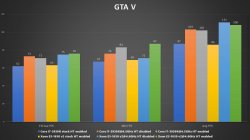

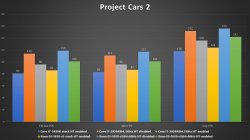

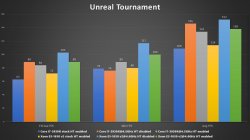

Siihen sitten päälle ajaa testit läpi noilla testeilläni joissa pelejä löytyy kivat 28kpl.

Sitten excel taulukoitten täyttämistä ja sitten videon kyyhääminen. Aikaa menee jo nyt niin paljon etten pysty lisäämään mitään.

Aluksi testasin vakiona ja kellotettuna, mutta vakiona olevat testit jätin pois kun ei vaan ole aikaa kun samaan aikaan testi kirjasto paisu.

Meinasinkin sitä määrää pienentää mutta pyydettiin että en tiputa niitä pelejä pois mitä olin tiputtamassa.

No ainakin on kattavat satsi eri tyypin pelejä ja kaikki aina käyttäytyvät erilailla eri arkkitehtuurejen kanssa.

Kun usein mitä näissä testeissä näkee niin max testataan n. viisi silloista AAA-peliä ja se siitä.

En halunnut lähteä siihen vaan yritän saada mahdollisimman paljon kaikkia indie tuotantoja mukaan.

Kun niistä nykyään ne hyvät pelit löytyy. AAA-pelit ovat olleet jo vuosia semmoista roskaa että niihin yritän olla koskematta.

Myöskin ei niin kivat kopiosuojaukset ovat estäneet etten BF1 tai BFV halua alkaa testamaan. Oli kiva kun BF1:stä lukittiin pois kun rautaa vaihto...

Toki se on 24h päästä taas on pelattava mutta antaa olla.

Ubisoftalla taas on niin monta kopiosuojausta päällekkäin millä tehdään pelit raskaiksi joten en niitten pelejä testaa saatika osta.

Kun en halua tukea tuota paskaa.

Hauskaa ollut noita testatessa ja laittaa tuloksia taulukkoon. Ja samalla huomata kuinka väärässä internet on ollut milloin mistäkin.

Tai silloin ehkä olleet oikeassa mutta nykyään tilalle on aivan toinen.

Paras esimerkki on ollut AMD:n FX prossut jotka ovat nykyään yllättävän hyviä jopa se kuuluisa Bulldozer.

Muuten tämmönen testi emolevy kirjasto löytyy että pääsee testamaan monien eri alustojen prossuja.

Twitteriin tulee myös aina postattua jotain noista testeistä:

SP's Tech Lab (@Santeri_Pusa) | Twitter