-

PikanavigaatioAjankohtaista io-tech.fi uutiset Uutisia lyhyesti Muu uutiskeskustelu io-tech.fi artikkelit io-techin Youtube-videot Palaute, tiedotukset ja arvonnat

Tietotekniikka Prosessorit, ylikellotus, emolevyt ja muistit Näytönohjaimet Tallennus Kotelot ja virtalähteet Jäähdytys Konepaketit Kannettavat tietokoneet Buildit, setupit, kotelomodifikaatiot & DIY Oheislaitteet ja muut PC-komponentit

Tekniikkakeskustelut Ongelmat Yleinen rautakeskustelu Älypuhelimet, tabletit, älykellot ja muu mobiili Viihde-elektroniikka, audio ja kamerat Elektroniikka, rakentelu ja muut DIY-projektit Internet, tietoliikenne ja tietoturva Käyttäjien omat tuotetestit

Softakeskustelut Pelit, PC-pelaaminen ja pelikonsolit Ohjelmointi, pelikehitys ja muu sovelluskehitys Yleinen ohjelmistokeskustelu Testiohjelmat ja -tulokset

Muut keskustelut Autot ja liikenne Urheilu TV- & nettisarjat, elokuvat ja musiikki Ruoka & juoma Koti ja asuminen Yleistä keskustelua Politiikka ja yhteiskunta Hyvät tarjoukset Tekniikkatarjoukset Pelitarjoukset Ruoka- ja taloustarviketarjoukset Muut tarjoukset

Kauppa-alue

Navigation

Install the app

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Huomio: This feature may not be available in some browsers.

Lisää vaihtoehtoja

Tyylin valinta

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Virallinen: AMD vs Intel keskustelu- ja väittelyketju

- Keskustelun aloittaja Sampsa

- Aloitettu

finWeazel

Tukijäsen

- Liittynyt

- 15.12.2019

- Viestejä

- 14 174

pdep on hyödyllinen sam:in kanssa, kun se mahdollistaa tietynlaisen datan mankeloinnin cpu:lla tehokkaasti ennen gpu:n muistiin siirtämistä. Pakollinen se ei ole, mutta hyödyllinen. Mitään iloahan pdep:sta ei ole ellei pelienginet sitä käytä datan käpistelyyn. Tuolla saa vähän säästettyä gpu:ta oleellisempiin taskeihin ja cpu:n käyttöastetta ylöspäin.

- Liittynyt

- 23.05.2017

- Viestejä

- 1 446

Katohan kun "ei säikeet riitä enää mihinkään" 9600k riittääkin ihan kivasti tässä.CP 2077 kurittaa prosessoreita mukavasti, vanhat 4c prossut hyytyy pahasti.

- Liittynyt

- 12.01.2017

- Viestejä

- 3 228

Tarkoitatko kivasti riittämisellä sitä, että se häviää minimeissä (1%) vain 1 fps:n verrattuna halvempaan ikätoveriinsa Ryzen 3600:een? Vai sitä, että 35 fps:n minimi on ihan kivasti pelikelpoinen? Säikeiden riittämättömyys näkyy ensimmäisenä minimeissä ja sitä myöten min/avg - suhteen romahtamisena. Pelikokemuksen sulavuuden rikkoo juuri heikko minimi, joten siihen kannattaa kiinnittää huomiota muutenkin.Katohan kun "ei säikeet riitä enää mihinkään" 9600k riittääkin ihan kivasti tässä.

Min/avg, %:

9600K (6/6) 58,6 %

9900K (8/16) 65,9 %

10600K (6/12) 64,3 %

10700K (8/16) 66,6 %

10900K (10/20) 66,3 %

Huomaatko noista luvuista 9600K:n alkaneen kärsiä vähistä säikeistä?

Otetaan malliksi esiin vielä enemmän kärsinyt malli:

4670K (4/4) 44,7 %

Entäpä core-hirmu:

5950X (16/32) 71,1 %

Kyseinen peli näyttäisi suosivan Inteliä. Esim. 5800X vs. 10700K ja 5600X vs. 10600K näyttäisi poikkeavan hatusta heittämällä 10 % laajan pelijoukon keskiarvoista. 5900X vs. 10900K ei ole yhtä suurta poikkeamaa, mutta se johtuu kahdesta lisäytimestä ja pelin erinomaisesta moniydintuesta.

Joko keskityit katselemaan vain keskimääräistä ruudunpäivitystä, tai sitten vertasit 9600K:ta vain Ryzeneihin, jolloin pelin Intelille suosiollisuus pääsi hämäämään. Katso mieluummin minimeitä ja vertaa useampisäikeisiin Inteleihin, niin näet selvemmin 6/6 -coren heikkouden tuossa pelissä.

Minimit:

9600K/9900K, 35 fps/53 fps (+51 %)

Ei noilla kahdella prossulla ilmestyessään ollut tuollaista 51 % eroa minimeissä. Valitettavasti 9600K alkaa uusien pelien myötä jäämään "ydinhirmujen" jalkoihin yhä enemmän. Sitten se näkyy ja tuntuu vielä tätäkin enemmän, kun se uusi peli sattuukin olemaan AMD-ystävällinen. Silloin ikätoverit 3600 ja 3700X jättävät ison hajuraon, jos nytkin niiden minimit olivat 36 fps ja 46 fps vs. 9600K:n 35 fps.

Viimeksi muokattu:

Proscribo

Kiitos.

- Liittynyt

- 16.10.2016

- Viestejä

- 1 204

Eikö olisi riittänyt mainita, että 6 vuotta vanha Haswell-E 8c/16t 5960X on hyvällä erolla 9600K:n edellä.Tarkoitatko kivasti riittämisellä sitä, että se häviää minimeissä (1%) vain 1 fps:n verrattuna halvempaan ikätoveriinsa Ryzen 3600:een? Vai sitä, että 35 fps:n minimi on ihan kivasti pelikelpoinen? Säikeiden riittämättömyys näkyy ensimmäisenä minimeissä ja sitä myöten min/avg - suhteen romahtamisena. Pelikokemuksen sulavuuden rikkoo juuri heikko minimi, joten siihen kannattaa kiinnittää huomiota muutenkin.

Min/avg, %:

9600K (6/6) 58,6 %

9900K (8/16) 65,9 %

10600K (6/12) 64,3 %

10700K (8/16) 66,6 %

10900K (10/20) 66,3 %

Huomaatko noista luvuista 9600K:n alkaneen kärsiä vähistä säikeistä?

Otetaan malliksi esiin vielä enemmän kärsinyt malli:

4670K (4/4) 44,7 %

Entäpä core-hirmu:

5950X (16/32) 71,1 %

Kyseinen peli näyttäisi suosivan Inteliä. Esim. 5800X vs. 10700K ja 5600X vs. 10600K näyttäisi poikkeavan hatusta heittämällä 10 % laajan pelijoukon keskiarvoista. 5900X vs. 10900K ei ole yhtä suurta poikkeamaa, mutta se johtuu kahdesta lisäytimestä ja pelin erinomaisesta moniydintuesta.

Joko keskityit katselemaan vain keskimääräistä ruudunpäivitystä, tai sitten vertasit 9600K:ta vain Ryzeneihin, jolloin pelin Intelille suosiollisuus pääsi hämäämään. Katso mieluummin minimeitä ja vertaa useampisäikeisiin Inteleihin, niin näet selvemmin 6/6 -coren heikkouden tuossa pelissä.

Minimit:

9600K/9900K, 35 fps/53 fps (+51 %)

Ei noilla kahdella prossulla ilmestyessään ollut tuollaista 51 % eroa minimeissä. Valitettavasti 9600K alkaa uusien pelien myötä jäämään "ydinhirmujen" jalkoihin yhä enemmän. Sitten se näkyy ja tuntuu vielä tätäkin enemmän, kun se uusi peli sattuukin olemaan AMD-ystävällinen. Silloin ikätoverit 3600 ja 3700X jättävät ison hajuraon, jos nytkin niiden minimit olivat 36 fps ja 46 fps vs. 9600K:n 35 fps.

- Liittynyt

- 23.05.2017

- Viestejä

- 1 446

No totta ihmeessä vertaan lähinnä ryzenin 3600 malliin.Tarkoitatko kivasti riittämisellä sitä, että se häviää minimeissä (1%) vain 1 fps:n verrattuna halvempaan ikätoveriinsa Ryzen 3600:een? Vai sitä, että 35 fps:n minimi on ihan kivasti pelikelpoinen? Säikeiden riittämättömyys näkyy ensimmäisenä minimeissä ja sitä myöten min/avg - suhteen romahtamisena. Pelikokemuksen sulavuuden rikkoo juuri heikko minimi, joten siihen kannattaa kiinnittää huomiota muutenkin.

Min/avg, %:

9600K (6/6) 58,6 %

9900K (8/16) 65,9 %

10600K (6/12) 64,3 %

10700K (8/16) 66,6 %

10900K (10/20) 66,3 %

Huomaatko noista luvuista 9600K:n alkaneen kärsiä vähistä säikeistä?

Otetaan malliksi esiin vielä enemmän kärsinyt malli:

4670K (4/4) 44,7 %

Entäpä core-hirmu:

5950X (16/32) 71,1 %

Kyseinen peli näyttäisi suosivan Inteliä. Esim. 5800X vs. 10700K ja 5600X vs. 10600K näyttäisi poikkeavan hatusta heittämällä 10 % laajan pelijoukon keskiarvoista. 5900X vs. 10900K ei ole yhtä suurta poikkeamaa, mutta se johtuu kahdesta lisäytimestä ja pelin erinomaisesta moniydintuesta.

Joko keskityit katselemaan vain keskimääräistä ruudunpäivitystä, tai sitten vertasit 9600K:ta vain Ryzeneihin, jolloin pelin Intelille suosiollisuus pääsi hämäämään. Katso mieluummin minimeitä ja vertaa useampisäikeisiin Inteleihin, niin näet selvemmin 6/6 -coren heikkouden tuossa pelissä.

Minimit:

9600K/9900K, 35 fps/53 fps (+51 %)

Ei noilla kahdella prossulla ilmestyessään ollut tuollaista 51 % eroa minimeissä. Valitettavasti 9600K alkaa uusien pelien myötä jäämään "ydinhirmujen" jalkoihin yhä enemmän. Sitten se näkyy ja tuntuu vielä tätäkin enemmän, kun se uusi peli sattuukin olemaan AMD-ystävällinen. Silloin ikätoverit 3600 ja 3700X jättävät ison hajuraon, jos nytkin niiden minimit olivat 36 fps ja 46 fps vs. 9600K:n 35 fps.

Noita ostettiin ihan tuskana nimenomaan pelikäyttöön.

Ei kait sitä voi ihan tosissaan verrata tuplasti tai triplasti kalliimpiin kiviin.

- Liittynyt

- 12.01.2017

- Viestejä

- 3 228

Ok, verrataan siihen. Syyskuussa 2019 Ryzen 3600:n tullessa 9600K maksoi noin 40-50 € enemmän kuin 3600, eli se oli noin 20 % kalliimpi tuote. Lisäksi nopeita muisteja halutessaan siihen piti ostaa kalliimpi Z-sarjan emolevy, kun Ryzenille riitti edullinen B450. Kyseinen Intel oli siis kalliimpi vaihtoehto, mutta toisaalta nimenomaan pelikäytössä hinnalle sai vastinetta 5-10 % paremman suorituskyvyn muodossa. IO-techin revikan mukaan minimeissä ero oli jopa 10-20 % Intelin hyväksi, jos CSGO:ta ei lasketa. Tuo oli tilanne 2019 syksyllä. AMD:n valttina oli SMT, mistä oli apua hyötyohjelmissa.No totta ihmeessä vertaan lähinnä ryzenin 3600 malliin.

Noita ostettiin ihan tuskana nimenomaan pelikäyttöön.

Ei kait sitä voi ihan tosissaan verrata tuplasti tai triplasti kalliimpiin kiviin.

Nyt Cyberpunkin myötä voimasuhteet alkavat kääntyä myös peleissä. Halvempi AMD 3600 oli jo karvan verran parempi minimeissä, vaikka peli selvästi suosii Inteliä. Suosimisen määrä on noin 10 %, minkä näkee, kun vertaa 6- ja 8-ydin 10xxxK vs. 5x00X. Tuossa pelissä Intel voittaa 5 %, kun taas eri pelien keskiarvossa AMD voittaa noin 5 %. Jos lasketaan tuo Intelille suosiollisuus pois, niin minimeiksi saadaan 35 vs. 36 sijaan 35 fps (9600K) vs. 40 fps (3600). Tuossa olisi voimasuhteet neutraalissa pelissä, joka olisi yhtä vaativa kuin Cyberpunk. Yhtäkkiä se halvempi ja julkaisuhetkellään heikompi peliprossu alkaakin olla vahvempi, eikä tähän mennyt kuin reilu vuosi.

@Proscribo Olisi riittänyt 5960X:n maininta, jos olisin halunnut tarkastella vain onko pelissä hyvä moniydintuki, mutta senhän nyt näki heti, että on hyvä tuki. Halusin sen sijaan katsoa, tuleeko tuossa pelissä kunnon romahtaminen min/avg -suhteessa jo 6/6 -ytimisellä, kuten jo aiemmin on nähty 4/4:lle tapahtuvan. Cyberpunkissa tuo suhde on Intelillä noin 66 %, jos prossussa on säikeitä riittävästi. Rajatapaus on 6/12, jolla suhde on 64 %. Pelinopeus toki paranee lisäytimillä, mutta vasta tuon alle mentäessä minimi alkaa suhteellisestikin romahtaa. Siinä 6/6:ssa oli 58,6 % ja 4/4:ssä 44,7 %.

Tarkoitatko kivasti riittämisellä sitä, että se häviää minimeissä (1%) vain 1 fps:n verrattuna halvempaan ikätoveriinsa Ryzen 3600:een? Vai sitä, että 35 fps:n minimi on ihan kivasti pelikelpoinen? Säikeiden riittämättömyys näkyy ensimmäisenä minimeissä ja sitä myöten min/avg - suhteen romahtamisena. Pelikokemuksen sulavuuden rikkoo juuri heikko minimi, joten siihen kannattaa kiinnittää huomiota muutenkin.

Min/avg, %:

9600K (6/6) 58,6 %

9900K (8/16) 65,9 %

10600K (6/12) 64,3 %

10700K (8/16) 66,6 %

10900K (10/20) 66,3 %

Huomaatko noista luvuista 9600K:n alkaneen kärsiä vähistä säikeistä?

Otetaan malliksi esiin vielä enemmän kärsinyt malli:

4670K (4/4) 44,7 %

Entäpä core-hirmu:

5950X (16/32) 71,1 %

Kyseinen peli näyttäisi suosivan Inteliä. Esim. 5800X vs. 10700K ja 5600X vs. 10600K näyttäisi poikkeavan hatusta heittämällä 10 % laajan pelijoukon keskiarvoista. 5900X vs. 10900K ei ole yhtä suurta poikkeamaa, mutta se johtuu kahdesta lisäytimestä ja pelin erinomaisesta moniydintuesta.

Joko keskityit katselemaan vain keskimääräistä ruudunpäivitystä, tai sitten vertasit 9600K:ta vain Ryzeneihin, jolloin pelin Intelille suosiollisuus pääsi hämäämään. Katso mieluummin minimeitä ja vertaa useampisäikeisiin Inteleihin, niin näet selvemmin 6/6 -coren heikkouden tuossa pelissä.

Minimit:

9600K/9900K, 35 fps/53 fps (+51 %)

Ei noilla kahdella prossulla ilmestyessään ollut tuollaista 51 % eroa minimeissä. Valitettavasti 9600K alkaa uusien pelien myötä jäämään "ydinhirmujen" jalkoihin yhä enemmän. Sitten se näkyy ja tuntuu vielä tätäkin enemmän, kun se uusi peli sattuukin olemaan AMD-ystävällinen. Silloin ikätoverit 3600 ja 3700X jättävät ison hajuraon, jos nytkin niiden minimit olivat 36 fps ja 46 fps vs. 9600K:n 35 fps.

Mitä vittua mä just katsoin??

Aivot ei prosessoi enää tässä vaiheessa iltaa, mutta maestrolle kysymys,

Pärjääkö 8700k:lla vielä 2-021? Hieman tulkinnan varaa oli noissa 3600/5600 taulukoissa.

Pystytkö testaamaan DLSS2.0 + RTX 4k:lle? varmaan prossulta ottaa erimäärän resursseja?Sigun ekalla kokoonpanolla kokeilin 1080p ja DLSS performance, kaikki asetukset tapissa paitsi RTX off, ja FPS oli jatkuvasti 100+ kun ajelin ympäri kaupunkia. Ei mitään pelkoa, että 6/12 prossu hyytyisi tässä pelissä.

Hieman huolettaa nuo monet ilmoitukset prosessorin kuormituksesta 4k resoluutiolla.

- Liittynyt

- 12.01.2017

- Viestejä

- 3 228

Eiköhän sillä vielä viisi vuotta pärjäile, jos ei ole liian vaativa. Toki paremmat nopeudet ja sulavuuden saa >=8/16 -ytimisellä. Veikkaan 6/12:n min/avg -suhteen heikkenevän 1-2 vuoden sisällä samaan jamaan kuin mitä 6/6 on nyt.Aivot ei prosessoi enää tässä vaiheessa iltaa, mutta maestrolle kysymys,

Pärjääkö 8700k:lla vielä 2-021? Hieman tulkinnan varaa oli noissa 3600/5600 taulukoissa.

- Liittynyt

- 17.10.2016

- Viestejä

- 2 962

Pystytkö testaamaan DLSS2.0 + RTX 4k:lle? varmaan prossulta ottaa erimäärän resursseja?

Hieman huolettaa nuo monet ilmoitukset prosessorin kuormituksesta 4k resoluutiolla.

En pysty, kun silloin näytönohjain rajoittaa prossun menoa. Resoluution nosto ei lisää prosessorin kuormitusta muutenkaan. RTX voisi ehkä lisätä, mutta sitä on vaikea testata, kun RTX päällä näytönohjaimesta loppuu puhti kauan ennen prossua.

- Liittynyt

- 12.12.2016

- Viestejä

- 5 000

Eiköhän sillä vielä viisi vuotta pärjäile, jos ei ole liian vaativa. Toki paremmat nopeudet ja sulavuuden saa >=8/16 -ytimisellä. Veikkaan 6/12:n min/avg -suhteen heikkenevän 1-2 vuoden sisällä samaan jamaan kuin mitä 6/6 on nyt.

4c/4t prossut alkoi yskimään ekan kerran joskus 2015 (moninpeleissä, mm. BF sarjassa, mut sit esim BF One pyöri paremmin niillä kuin nelonen ja hardline), että ois aika ihme jos nyt jäisi 12t prossut jalkoihin vuosi sen perään kun 6t alkaa olla liian vähän...

- Liittynyt

- 23.05.2017

- Viestejä

- 1 446

Mitä ihme sekoilua. 6core 6thread kivet on kuolleita. Ja silti niillä pelaa. Käsittämätöntä sekoilua, että jotkut markkinat muka yht äkkiä muuttuisi raudan mukana. No ei muutu.Ok, verrataan siihen. Syyskuussa 2019 Ryzen 3600:n tullessa 9600K maksoi noin 40-50 € enemmän kuin 3600, eli se oli noin 20 % kalliimpi tuote. Lisäksi nopeita muisteja halutessaan siihen piti ostaa kalliimpi Z-sarjan emolevy, kun Ryzenille riitti edullinen B450. Kyseinen Intel oli siis kalliimpi vaihtoehto, mutta toisaalta nimenomaan pelikäytössä hinnalle sai vastinetta 5-10 % paremman suorituskyvyn muodossa. IO-techin revikan mukaan minimeissä ero oli jopa 10-20 % Intelin hyväksi, jos CSGO:ta ei lasketa. Tuo oli tilanne 2019 syksyllä. AMD:n valttina oli SMT, mistä oli apua hyötyohjelmissa.

Nyt Cyberpunkin myötä voimasuhteet alkavat kääntyä myös peleissä. Halvempi AMD 3600 oli jo karvan verran parempi minimeissä, vaikka peli selvästi suosii Inteliä. Suosimisen määrä on noin 10 %, minkä näkee, kun vertaa 6- ja 8-ydin 10xxxK vs. 5x00X. Tuossa pelissä Intel voittaa 5 %, kun taas eri pelien keskiarvossa AMD voittaa noin 5 %. Jos lasketaan tuo Intelille suosiollisuus pois, niin minimeiksi saadaan 35 vs. 36 sijaan 35 fps (9600K) vs. 40 fps (3600). Tuossa olisi voimasuhteet neutraalissa pelissä, joka olisi yhtä vaativa kuin Cyberpunk. Yhtäkkiä se halvempi ja julkaisuhetkellään heikompi peliprossu alkaakin olla vahvempi, eikä tähän mennyt kuin reilu vuosi.

@Proscribo Olisi riittänyt 5960X:n maininta, jos olisin halunnut tarkastella vain onko pelissä hyvä moniydintuki, mutta senhän nyt näki heti, että on hyvä tuki. Halusin sen sijaan katsoa, tuleeko tuossa pelissä kunnon romahtaminen min/avg -suhteessa jo 6/6 -ytimisellä, kuten jo aiemmin on nähty 4/4:lle tapahtuvan. Cyberpunkissa tuo suhde on Intelillä noin 66 %, jos prossussa on säikeitä riittävästi. Rajatapaus on 6/12, jolla suhde on 64 %. Pelinopeus toki paranee lisäytimillä, mutta vasta tuon alle mentäessä minimi alkaa suhteellisestikin romahtaa. Siinä 6/6:ssa oli 58,6 % ja 4/4:ssä 44,7 %.

- Liittynyt

- 25.10.2018

- Viestejä

- 672

Intel Rocket Lake-S Core i9-11900K CPU allegedly boost up to 5.3 GHz - VideoCardz.com

Intel’s Core i9-11900K specifications The flagship Rocket Lake-S CPU has already leaked earlier this month through Ashes of the Singularity benchmark website. It was revealed back then that the CPU carries a base clock of 3.5 GHz. Unfortunately, the software does not report on maximum turbo...

Kellottuu varmaan samaan mitä 10900k ja ipc parannus eli jytky tulossa. Jos esim on 10% ipc parannus niin vastaisi 5.8 ghz 10900kta (kellotettuna 5.3 ghz). Toki 2 corea vähemmän, mutta 8 core se optimein pelaamisen kannalta.

Kannattaa pitää se mopon keula ihan vain maassa, kunnes luotettavat kolmannet osapuolet ovat ajaneet kattavat testit ko prosessorilla.

Intel Rocket Lake-S Core i9-11900K CPU allegedly boost up to 5.3 GHz - VideoCardz.com

Intel’s Core i9-11900K specifications The flagship Rocket Lake-S CPU has already leaked earlier this month through Ashes of the Singularity benchmark website. It was revealed back then that the CPU carries a base clock of 3.5 GHz. Unfortunately, the software does not report on maximum turbo...videocardz.com

Kellottuu varmaan samaan mitä 10900k ja ipc parannus eli jytky tulossa. Jos esim on 10% ipc parannus niin vastaisi 5.8 ghz 10900kta (kellotettuna 5.3 ghz). Toki 2 corea vähemmän, mutta 8 core se optimein pelaamisen kannalta.

- Liittynyt

- 15.04.2018

- Viestejä

- 2 342

Vaikka tulisi tuollaiset ja tehot skaalautuisi hyvin, niin mielestäni 8/16 prossu ei saisi maksaa yli 500€. Jos hinta ei nelosella ala, sanoisin tuhnuksi.

Intel Rocket Lake-S Core i9-11900K CPU allegedly boost up to 5.3 GHz - VideoCardz.com

Intel’s Core i9-11900K specifications The flagship Rocket Lake-S CPU has already leaked earlier this month through Ashes of the Singularity benchmark website. It was revealed back then that the CPU carries a base clock of 3.5 GHz. Unfortunately, the software does not report on maximum turbo...videocardz.com

Kellottuu varmaan samaan mitä 10900k ja ipc parannus eli jytky tulossa. Jos esim on 10% ipc parannus niin vastaisi 5.8 ghz 10900kta (kellotettuna 5.3 ghz). Toki 2 corea vähemmän, mutta 8 core se optimein pelaamisen kannalta.

- Liittynyt

- 18.10.2016

- Viestejä

- 6 357

250W? Nyt ihan oikeasti... Tuo menohan on samaa luokkaa kuin pulttaisi lentokoneeseen pari suihkumoottoria lisää polttoainetta syömään, että se kulkisi hiukan lujempaa kuin kilpailijan versio ja väittäisi sitten sitä suureksi suunnitteluvoitoksi.

Intel Rocket Lake-S Core i9-11900K CPU allegedly boost up to 5.3 GHz - VideoCardz.com

Intel’s Core i9-11900K specifications The flagship Rocket Lake-S CPU has already leaked earlier this month through Ashes of the Singularity benchmark website. It was revealed back then that the CPU carries a base clock of 3.5 GHz. Unfortunately, the software does not report on maximum turbo...videocardz.com

Kellottuu varmaan samaan mitä 10900k ja ipc parannus eli jytky tulossa. Jos esim on 10% ipc parannus niin vastaisi 5.8 ghz 10900kta (kellotettuna 5.3 ghz). Toki 2 corea vähemmän, mutta 8 core se optimein pelaamisen kannalta.

- Liittynyt

- 21.06.2017

- Viestejä

- 7 593

Intel Rocket Lake-S Core i9-11900K CPU allegedly boost up to 5.3 GHz - VideoCardz.com

Intel’s Core i9-11900K specifications The flagship Rocket Lake-S CPU has already leaked earlier this month through Ashes of the Singularity benchmark website. It was revealed back then that the CPU carries a base clock of 3.5 GHz. Unfortunately, the software does not report on maximum turbo...videocardz.com

Kellottuu varmaan samaan mitä 10900k ja ipc parannus eli jytky tulossa. Jos esim on 10% ipc parannus niin vastaisi 5.8 ghz 10900kta (kellotettuna 5.3 ghz). Toki 2 corea vähemmän, mutta 8 core se optimein pelaamisen kannalta.

Ettei olisi yksisarvinen, eli toisinsanoen paperijulkaisu.

Jos toi 4,6-4,8GHz all core hörppää jo ne 250W, niin kaikkien ytimien 5,x GHz lienee aika älytön potentiaaliselta kulutukseltaan. Peleissä ja muissa kevyissä kuormissa tilanne ei tietty ole niin paha kuin mitä luvut antavat ymmärtää. Järkevä all core kellotus jäänee nyt viimeistään väliin intelinkin alustalla.Ettei olisi yksisarvinen, eli toisinsanoen paperijulkaisu.Medialle jaetaan sämplet että saadaan oma tuote listan kärkeen, mutta todellisuudessa myydään i7 mallia joka ei välttämättä pärjää. Toihan on yhen coren boosti ja all corea on tarttenu 10900K:n verrattuna tiputtaa 100MHz ja corejakin on 2 vähemmän, tuskin siis löytyy montaa yksilöä joka all corella tuohon kykenee.

- Liittynyt

- 12.01.2017

- Viestejä

- 3 228

Sen 4c/4t yskimisen alkamisesta lähtien pari ensimmäistä vuotta oli 4c/8t -stagnaatiota, joten aika kului, eikä ollut järkeä mennä yli 4/8 -tason. Vasta 2017 tuli parempaa kuluttajakannoille. En osaa sanoa minä vuonna 6/6 on alkanut yskimään, mutta ainakin tuon Cyberpunkin min/avg -suhteesta sen näkee.4c/4t prossut alkoi yskimään ekan kerran joskus 2015 (moninpeleissä, mm. BF sarjassa, mut sit esim BF One pyöri paremmin niillä kuin nelonen ja hardline), että ois aika ihme jos nyt jäisi 12t prossut jalkoihin vuosi sen perään kun 6t alkaa olla liian vähän...

Se 6/12 vastaa suorituskyvyltään suunnilleen 8/8:a. Näin ajatellen hyppy 6/6 -> 6/12 (8/8) = +33 %. Edellinen hyppy oli suurempi: 4/4 -> 6/6 = +50 %. Siksi edelliseen yskimisväliin kului luonnollisesti pidempi aika. Siihen kun ynnää parin vuoden pysähtyneisyyden ja sen, että nyt kaupasta saa kukkurakaupalla ytimiä osti sitten PC:n tai konsolin, niin seuraava yskimisväli ei tule olemaan viittä vuotta. Muuten olisin sanonut

2-3 v, mutta ydintarjonnan takia sanon 1-2 v.

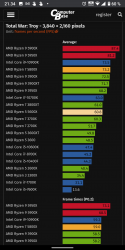

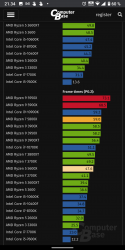

Ohessa saksalaisten testaamana Total War: Troy@2160p. Intelin 6/12:t saivat minimeiksi (P0,2) 35-37 fps, kun Intelin 10/20 sai 59 fps. Siinä on tuntuva ero, mutta minimin ja keskimääräisen suhde ei ole pahemmin vielä heikentynyt ollen vain pari %-yksikköä isompien takana. Jos veikkaukseni mukaisesti 1-2 vuoden kuluessa tuo suhde laskee yhtä heikoksi kuin 6/6:lla on nyt, niin 6/12:n minimit ovat Troyn kaltaisissa peleissä kutakuinkin puolet 10/20:sta.

Min/avg:

10600K (6/12) 79 %

10700K (8/16) 81 %

10900K (10/20) 81 %

En ole puhunut mistään jalkoihin jäämisestä. Kyllä 6/12:lla pelailee tuon 1-2 vuoden jälkeenkin. Ja kuten aiemmin sanoin, jopa viisikin vuotta, jos ei ole liian vaativa pelaaja. Kuitenkaan uutena en tonnin pelikoneeseen ostaisi 6/12-prossua, jos olisin ostoksilla 1-2 vuoden päästä. Silloin odotettavissa oleva käyttöikä olisi jo aivan liian lyhyt.

Palataan asiaan 1-2 vuoden kuluttua, että onko silloin 6/12:n min/avg -suhde jossain pelissä yli 10 % heikompi kuin isommilla, kuten tilanne 6/6:lla on nyt Cyberissä. Jos on, niin olin oikeassa siinä mitä väitin.

"Veikkaan 6/12:n min/avg -suhteen heikkenevän 1-2 vuoden sisällä samaan jamaan kuin mitä 6/6 on nyt."

Liitteet

Se on se PL2-lukema. i9-10900K:lla on sama PL2-arvo. Sillä teholla menee maksimissaan 56 sekuntia putkeen. Nähtäväksi jää, että onko sitä kestoa pidennetty, mutta veikkaisin että ei, ellei muuta tietoa tule.250W? Nyt ihan oikeasti... Tuo menohan on samaa luokkaa kuin pulttaisi lentokoneeseen pari suihkumoottoria lisää polttoainetta syömään, että se kulkisi hiukan lujempaa kuin kilpailijan versio ja väittäisi sitten sitä suureksi suunnitteluvoitoksi.

- Liittynyt

- 19.10.2016

- Viestejä

- 30

Paitsi että ei kurita AMD:n prossuja tarpeeksi. Tuohon on varmaan tulossa päivitys.CP 2077 kurittaa prosessoreita mukavasti, vanhat 4c prossut hyytyy pahasti.

Cyberpunk 2077 Bug Bulldozes AMD Ryzen: Here's a Fix, Tested

Paitsi että ei kurita AMD:n prossuja tarpeeksi. Tuohon on varmaan tulossa päivitys.

Cyberpunk 2077 Bug Bulldozes AMD Ryzen: Here's a Fix, Tested

Ja modina, ettei tarvitse hexalla leikkiä ja häkätä jokaisen päivityksen yhteydessä uudestaan:

- Liittynyt

- 22.10.2016

- Viestejä

- 12 914

Paitsi että ei kurita AMD:n prossuja tarpeeksi. Tuohon on varmaan tulossa päivitys.

Cyberpunk 2077 Bug Bulldozes AMD Ryzen: Here's a Fix, Tested

"Hienoa", kuinka AMDn markkinoinnin typerä n. kymmenen vuoden takainen päätös päätös mainostaa Bulldozerissa kahta ytimen(modulen) clusteria "ytimenä" jotta saadaan mainostaa suurempia "ydinmääriä", puree AMDn uudempia tuotteita jalkaan vielä 9 yli vuotta Bulldozerin julkaisua myöhemminkin.

Aina kun tehdään jotain häröjä ratkaisuita, pitäisi miettiä vähän enemmän että millainen yhteensopivuuspainolasti tästä on tulevaisuudessa tulossa.

- Liittynyt

- 21.06.2017

- Viestejä

- 7 593

r/pcgaming - Comment by u/CookiePLMonster on ”Cyberpunk 2077 used an Intel C++ compiler which hinders optimizations if run on non-Intel CPUs. Here's how to disable the check and gain 10-20% performance.”

7,272 votes and 1,096 comments so far on Reddit

Taitaa olla GPUOpen koodin puki kyseessä.

- Liittynyt

- 20.10.2016

- Viestejä

- 2 156

Aina kun tehdään jotain häröjä ratkaisuita, pitäisi miettiä vähän enemmän että millainen yhteensopivuuspainolasti tästä on tulevaisuudessa tulossa.

Tosin jos haluat kehitystä tuon silmällä pitäen, niin kehitys tulisi hidastumaan ihan älyttömästi kun pitäisi kaikki mahdolliset vaihtoehdot ottaa huomioon tulevista tuotteista jotka eivät ole edes piirustuspöydällä.

- Liittynyt

- 19.10.2016

- Viestejä

- 30

Pitää näin offtopikkina sanoa, että sinun asioita lukeneena nostan hattua korkealle, koska tietämyksesi prosessoreista ja niiden toiminnasta on huikea. x86 -platformi on vanha, ja siihenhän on lisätty purkkaa purkan perään."Hienoa", kuinka AMDn markkinoinnin typerä n. kymmenen vuoden takainen päätös päätös mainostaa Bulldozerissa kahta ytimen(modulen) clusteria "ytimenä" jotta saadaan mainostaa suurempia "ydinmääriä", puree AMDn uudempia tuotteita jalkaan vielä 9 yli vuotta Bulldozerin julkaisua myöhemminkin.

Aina kun tehdään jotain häröjä ratkaisuita, pitäisi miettiä vähän enemmän että millainen yhteensopivuuspainolasti tästä on tulevaisuudessa tulossa.

Intelin prosessiongelmat ilmeisesti jatkuvat...

www.notebookcheck.net

www.notebookcheck.net

Edit: Mielenkiintoista mutta surullista tietoa tuokin, että Alder Lake-S:nkin tuotantomäärät tulevat olemaan pienehköjä, koska 10 nm prosessin valmistuskapasiteetti ei riitä.

Kapasiteettiongelmat varmaan selittävät sitä, että miksi 8-ytimistä Tiger Lakea ei ole vielä markkinoilla, vaikka siitä on ollut liikkeellä huhuja jo jonkin aikaa.

Tough times ahead for Intel: industry insiders spill the beans on subpar 10 nm yields, server CPU plus 7 nm delays, production outsourcing and more

Industry insiders reveal that Intel's current 10 nm yields are nowhere near viable for “full production” and even with the SuperFin tech, 10 nm production may never match that of the 14 nm nodes. Plus we get more details about the performance issues with the upcoming server-grade CPUs, even more...

www.notebookcheck.net

www.notebookcheck.net

Edit: Mielenkiintoista mutta surullista tietoa tuokin, että Alder Lake-S:nkin tuotantomäärät tulevat olemaan pienehköjä, koska 10 nm prosessin valmistuskapasiteetti ei riitä.

Kapasiteettiongelmat varmaan selittävät sitä, että miksi 8-ytimistä Tiger Lakea ei ole vielä markkinoilla, vaikka siitä on ollut liikkeellä huhuja jo jonkin aikaa.

Viimeksi muokattu:

latee77

RTX ON

- Liittynyt

- 18.02.2017

- Viestejä

- 5 980

Ei ole tarkoitus väitellä, mutta kun 8700K on vaihtumassa hiljakseen 5900X niin mahtaako mokomaa edes huomata muussa kuin jossain pelien vähemmissä fps droppauksissa ja ehkä tulevissa CPU:ta vaativimpien pelien parempana FPS:sänä, vai tuntuuko ytimien lisäys ihan nettiselauksessa tai koneen / ohjelmien käynnistysnopeuksissakin? Tuskin kun jo NVMe levyllä kaikki softat alkaa olla.

5900X toki parempi peliprossu kuin 8700K mutta 4K resoilla ja 3090 kanssa ei taida edes vielä tulla pullon kaulaksi tuo 8700K. Ellei nyt Cyperpunk ole se eka tekele. Parin vuoden päästä oletan että tilanne on toinen.

5900X toki parempi peliprossu kuin 8700K mutta 4K resoilla ja 3090 kanssa ei taida edes vielä tulla pullon kaulaksi tuo 8700K. Ellei nyt Cyperpunk ole se eka tekele. Parin vuoden päästä oletan että tilanne on toinen.

- Liittynyt

- 21.08.2018

- Viestejä

- 5 521

Cyperpunkissa varmasti havaittavaa hyötyä 1080/1440p myös Marvel Avengers ainakin 10900K käytti prossua 80% joten oletan että siinäkin huomais jotain (Tosin pelissä nämä Intelin vesi/tuhoutumis efektit jotka ei vissiin ole käytössä Amd.lla? en ole kokeillut Amd raudalla peliä.)Ei ole tarkoitus väitellä, mutta kun 8700K on vaihtumassa hiljakseen 5900X niin mahtaako mokomaa edes huomata muussa kuin jossain pelien vähemmissä fps droppauksissa ja ehkä tulevissa CPU:ta vaativimpien pelien parempana FPS:sänä, vai tuntuuko ytimien lisäys ihan nettiselauksessa tai koneen / ohjelmien käynnistysnopeuksissakin? Tuskin kun jo NVMe levyllä kaikki softat alkaa olla.

5900X toki parempi peliprossu kuin 8700K mutta 4K resoilla ja 3090 kanssa ei taida edes vielä tulla pullon kaulaksi tuo 8700K. Ellei nyt Cyperpunk ole se eka tekele. Parin vuoden päästä oletan että tilanne on toinen.

DLSS avulla tuntuu että saa enemmän hyötyä prossusta kun se mahdollistaa astetta paria kovemmat Fps jolloin prosessorilta vaaditaan myös että pysyy ns.mukana.

latee77

RTX ON

- Liittynyt

- 18.02.2017

- Viestejä

- 5 980

Cyperpunkissa varmasti havaittavaa hyötyä 1080/1440p myös Marvel Avengers ainakin 10900K käytti prossua 80% joten oletan että siinäkin huomais jotain (Tosin pelissä nämä Intelin vesi/tuhoutumis efektit jotka ei vissiin ole käytössä Amd.lla? en ole kokeillut Amd raudalla peliä.)

DLSS avulla tuntuu että saa enemmän hyötyä prossusta kun se mahdollistaa astetta paria kovemmat Fps jolloin prosessorilta vaaditaan myös että pysyy ns.mukana.

Jos DLSS hyötyy prossusta niin aika kova setti olisi AMD moniydin kivi ja sille kaveriksi Nvidian piirturi. Tuo DLSS alkaa olla ihan must have -juttu jos 4K:lla tähtää korkeisiin fps lukemiin.

- Liittynyt

- 21.08.2018

- Viestejä

- 5 521

Ainakin niin kauan kunnes on niin kovaa rautaa että pyörisi natiivisti kovemmillakin asetuksilla +60fps.Jos DLSS hyötyy prossusta niin aika kova setti olisi AMD moniydin kivi ja sille kaveriksi Nvidian piirturi. Tuo DLSS alkaa olla ihan must have -juttu jos 4K:lla tähtää korkeisiin fps lukemiin.

Mutta pelejä pilataan sitten tuollaisella TAA kaltaisilla sumennuksilla niin DLSS stuntuu oikealta ratkaisulta käyttää.

latee77

RTX ON

- Liittynyt

- 18.02.2017

- Viestejä

- 5 980

Ainakin niin kauan kunnes on niin kovaa rautaa että pyörisi natiivisti kovemmillakin asetuksilla +60fps.

Mutta pelejä pilataan sitten tuollaisella TAA kaltaisilla sumennuksilla niin DLSS stuntuu oikealta ratkaisulta käyttää.

4K:lla ei sumenna yhtään kuvaa DLSS päällä, ellei niitä hurjimpia käytä. Mahtaakohan tuohon vaikuttaa tosiaan resot ja muu rauta / asetukset mutta ainakin kolmella pelillä toiminut oikein terävästi mitä tullut kokeiltua (CoD, Cyperpunk, Death stranding).

Kun on näitä 4K 144Hz+ näyttöjä niin pitää varmaan olla vielä seuraavassakin näyttissukupolvessa joku jippo että rullaa kaikilla herkuilla kovaa, pelitkin raskaantuu samaa vauhtia.

- Liittynyt

- 20.10.2016

- Viestejä

- 5 237

Ei mene Intelin 10nm SuperFin -prosessilla vieläkään hyvin:

- Alkuaikojen alle 25% saannoista on vähitellen kivuttu juuri ja juuri 50% yli.

- Ja tällöinkin on kyse jollakin tasolla käyttökelpoisten piirien saannosta - ei täysin virheettömistä piireistä kuten esimerkiksi sellaisista CPU:sta, joissa kaikki ytimet olisivat käyttökelpoisia.

- Suorituskykykin on varsin heikko. Socket -kohtainen suorituskyky nousee, mutta niin nousee virrankulutuskin.

- Intel jouluu laskemaan suurimpien myyntiin tulevien uusien Xeon -prosessoreiden ydinmäärää 38->36.

- OEM-tilauksista voidaan toimittaa vain pieni murto-osa

- Ice Lake on pettymus. Sapphire Rapids tulee olemaan paljon parempi, mutta tulee vasta Q2 22.

- 10 nm työpöytäprosessori (Alder Lake-S) on periaatteessa tulossa, mutta todennäköisesti sitä ei tulla tuomaan myyntiin kapasiteettirajoitteiden vuoksi (Xeoneja priorisoidaan).

- Intel etsii uutta toimitusjohtajaa CEO. Useita vaihtoehtoja on, mahdollisesti kolme kahdidaattia vielä jäljellä

Että silleen.

www.techpowerup.com

www.techpowerup.com

10 nm in "full production" and "shipping for revenue" since late 2018. Charlie still doesn't think it's viable. Much more real than it once was though, but not good enough.

- Alkuaikojen alle 25% saannoista on vähitellen kivuttu juuri ja juuri 50% yli.

- Ja tällöinkin on kyse jollakin tasolla käyttökelpoisten piirien saannosta - ei täysin virheettömistä piireistä kuten esimerkiksi sellaisista CPU:sta, joissa kaikki ytimet olisivat käyttökelpoisia.

- Suorituskykykin on varsin heikko. Socket -kohtainen suorituskyky nousee, mutta niin nousee virrankulutuskin.

- Intel jouluu laskemaan suurimpien myyntiin tulevien uusien Xeon -prosessoreiden ydinmäärää 38->36.

- OEM-tilauksista voidaan toimittaa vain pieni murto-osa

- Ice Lake on pettymus. Sapphire Rapids tulee olemaan paljon parempi, mutta tulee vasta Q2 22.

- 10 nm työpöytäprosessori (Alder Lake-S) on periaatteessa tulossa, mutta todennäköisesti sitä ei tulla tuomaan myyntiin kapasiteettirajoitteiden vuoksi (Xeoneja priorisoidaan).

- Intel etsii uutta toimitusjohtajaa CEO. Useita vaihtoehtoja on, mahdollisesti kolme kahdidaattia vielä jäljellä

Että silleen.

Intel's Manufacturing Outlook for the Future Doesn't Inspire Confidence in Successful Competition, According to Susquehanna Call

Susquehanna is a global trading firm which has various interests in silicon manufacturing - and part of that interest is naturally materialized in Intel. In a recent group call from the firm, some details on Intel's manufacturing and product design woes came to light, which point towards even...

10 nm in "full production" and "shipping for revenue" since late 2018. Charlie still doesn't think it's viable. Much more real than it once was though, but not good enough.

- Superfin is unquestionably far better than base 10 nm. Better in just about every way. Yields are better, but still on the low side.

- CNL had a yield of <25% even with iGPU disabled (seems a bit high to me but huh).

- 10 nm SF yields are far better but not as good as 14 (no surprises there). Past 50%.

- Not enough 10 nm capacity to handle the entire product stack yet. Charlie doesn't like Rocket Lake, considers the backport "painfully stupid". Will be huge and a power hog.

- 14 nm shortage caused by the fact that Intel had to bloat up die sizes.

- OEMs told they were to get a "small fraction" of orders of TGL. Improvements to yield won't fully help because no. of wafer starts is still low.

- He doesn't think 10 nm will ever exceed 14 nm capacity-wise.

- Ice Lake delayed again due to a bug, but this is a good thing. Looking like it'll come mid-late Q2 to early Q3 (although Charlie originally said March + 1.5-2 month delay?).

- Performance looks pretty poor. Akin to CL-SP actually - performance per socket remains the same but power rises. Core count for shipping parts dropped from 38 -> 36.

- Ice Lake is disappointing. Sapphire Rapids is way better. Comes in Q2 22.

- SPR was originally supposed to launch in Q2 21 to ship for Aurora but... yeah. Even then it was basically going to be a broken, alpha product which would be refined over multiple tapeouts.

- Once SPR fully rolls out and is fully sorted out it'll actually be pretty solid.

- The problem with SPR is timeline. ICL-SP was supposed to compete with Rome (and it would still lose even with the on-paper and significantly better specs than reality). Milan is going to likely beat SPR... over a year earlier and before ICL-SP rolls out. By the time SPR releases, Genoa will be here or right around the corner. Genoa was supposed to compete with GNR which is late 2023 now.

- If both companies iterate perfectly on their roadmaps as planned (much easier on AMD's side right now), Intel can not catch up to AMD until late 2024 or early 2025.

- AMD's biggest problem? Unsurprisingly - capacity.

- 7nm is significantly more delayed than the 6-12 months first claimed. PVC is in-hands basically now and it was the first 7nm product. Now it's on TSMC. Sometime December this year anyway.

- Intel may not know how much of a delay we're looking at with 7.

- Charlie thinks there are several problems with 7, not just 1. However, Charlie hasn't heard anything absolutely solid on the specifics here.

- Doesn't think Intel could sell fabs. Too many things problems involved. Fabs would need to be evaluated for the buyers needs etc etc.

- Foveros is more suited to low-power chips than servers/high power.

- Question about why ARM is more competitive in recent attempts vs previous attempts - Answer: more developed eco-system, lack of real glass-jaws compared to previous designs. Amazon is a bit more of a special case because they can design chips to exactly what they need with all the strengths and benefits that suit them best.

- Intel are going to out-source CPUs, but what and where is still being debated internally. Decision will be made in Q1 between SS and TSMC for different products. Nothing is set in stone yet.

- Intel are looking for a new CEO. There are multiple candidates, one has been shot down, 3 potential left. They are hoping to make the decision in Q1, probably after the Jan call. Does seem like Bob's going either way.

- Question: Will Intel do anything else with the backported core? A: I hope not.

- Intel won't outsource everything to TSMC because TSMC doesn't have the capacity. Intel grabbing capacity shouldn't take capacity away from AMD - TSMC should prioritise customers with long-term plans to stay with them.

- There is a 10 nm desktop product coming (Alder Lake-S) but Charlie doubts there will be much capacity for it due to it being needed elsewhere.

Viimeksi muokattu:

- Liittynyt

- 28.12.2016

- Viestejä

- 90

Jos tämä pitää edes osin paikkansa, niin ei kyllä hyvältä näytä. Räpiköinti jatkuisi ainakin 2024 loppuun ennen kuin saisivat AMD:n kiinni. Tämäkin VAIN JOS kaikki menee suunnitellusti. Ennusteet milloin prosessit saadaan valmiiksi eivät ole olleet kovin kohdillaan viime vuosina.Ei mene Intelin 10nm SuperFin -prosessilla vieläkään hyvin:

- Alkuaikojen alle 25% saannoista on vähitellen kivuttu juuri ja juuri 50% yli.

- Ja tällöinkin on kyse jollakin tasolla käyttökelpoisten piirien saannosta - ei täysin virheettömistä piireistä kuten esimerkiksi sellaisista CPU:sta, joissa kaikki ytimet olisivat käyttökelpoisia.

- Suorituskykykin on varsin heikko. Socket -kohtainen suorituskyky nousee, mutta niin nousee virrankulutuskin.

- Intel jouluu laskemaan suurimpien myyntiin tulevien uusien Xeon -prosessoreiden ydinmäärää 38->36.

- OEM-tilauksista voidaan toimittaa vain pieni murto-osa

- Ice Lake on pettymus. Sapphire Rapids tulee olemaan paljon parempi, mutta tulee vasta Q2 22.

- 10 nm työpöytäprosessori (Alder Lake-S) on periaatteessa tulossa, mutta todennäköisesti sitä ei tulla tuomaan myyntiin kapasiteettirajoitteiden vuoksi (Xeoneja priorisoidaan).

- Intel etsii uutta toimitusjohtajaa CEO. Useita vaihtoehtoja on, mahdollisesti kolme kahdidaattia vielä jäljellä

Että silleen.

Intel's Manufacturing Outlook for the Future Doesn't Inspire Confidence in Successful Competition, According to Susquehanna Call

Susquehanna is a global trading firm which has various interests in silicon manufacturing - and part of that interest is naturally materialized in Intel. In a recent group call from the firm, some details on Intel's manufacturing and product design woes came to light, which point towards even...www.techpowerup.com

moukula

Team Linux

- Liittynyt

- 17.10.2016

- Viestejä

- 2 940

Jos tämä pitää edes osin paikkansa, niin ei kyllä hyvältä näytä. Räpiköinti jatkuisi ainakin 2024 loppuun ennen kuin saisivat AMD:n kiinni. Tämäkin VAIN JOS kaikki menee suunnitellusti. Ennusteet milloin prosessit saadaan valmiiksi eivät ole olleet kovin kohdillaan viime vuosina.

Meinaatko että saisivat kiinni tämän nykytilanteen vai että saisivat kiinni AMD:n siinä pisteessä kun sekin on päivittänyt tuotteensa ja valmistustekniikkansa (varmaan jo pariin otteeseen siinä välissä)?

- Liittynyt

- 22.10.2016

- Viestejä

- 12 914

Ei mene Intelin 10nm SuperFin -prosessilla vieläkään hyvin:

Sellainen huomio, että tässä ei ole kyse mistään Intelin virallisesta tiedonannosta vaan jonkun ihan kolmannen osapuolen väitteistä. Eli huomattava osa näistä ei (välttämättä) pidä paikkaansa.

Lähinnä tuntuu että on joku tyyppi "Charlie" (Charlie Demerjian, joka on jonkun internet-huhusiten (Semiaccurate.com?) pitäjä) jolla on kasa internet-juoruja ja tässä ne on laitettu samaan nippuun.

Ja tässä sekoitetaan aivan täysin intelin toisen sukupolven "10nm" prosessia (käytössä ice lakessa) ja intelin 3. sukupolven "10nm" prosessia("Superfin"), käytössä Tiger Lakessa

Puhuaan "Superfinin ongelmista" mutta kun mikään Ice Lake ei ole valmistettu tuolla "superfin"-prosessilla"

- Intel jouluu laskemaan suurimpien myyntiin tulevien uusien Xeon -prosessoreiden ydinmäärää 38->36.

Hyvin harvassa tämän kokoluokan piirissä muutenkaan on kaikki ytimet enabloituna. Ja tässäkin voi olla kyse väärinymmärryksestä; Intelillä ei välttämättä ole koskaan ollutkaan aikomusta tuoda niitä "täysiä piirejä" markkinoille, mutta nyt kun on tullut tietoa että tulee maksimissaan 36-ytiminen SKU, "Charlie" on luullut, että jotain on nyt pudotettu.

- OEM-tilauksista voidaan toimittaa vain pieni murto-osa

- Ice Lake on pettymus. Sapphire Rapids tulee olemaan paljon parempi, mutta tulee vasta Q2 22.

- 10 nm työpöytäprosessori (Alder Lake-S) on periaatteessa tulossa, mutta todennäköisesti sitä ei tulla tuomaan myyntiin kapasiteettirajoitteiden vuoksi (Xeoneja priorisoidaan).

- Intel etsii uutta toimitusjohtajaa CEO. Useita vaihtoehtoja on, mahdollisesti kolme kahdidaattia vielä jäljellä

Että silleen.

Intel's Manufacturing Outlook for the Future Doesn't Inspire Confidence in Successful Competition, According to Susquehanna Call

Susquehanna is a global trading firm which has various interests in silicon manufacturing - and part of that interest is naturally materialized in Intel. In a recent group call from the firm, some details on Intel's manufacturing and product design woes came to light, which point towards even...www.techpowerup.com

- Ice Lake delayed again due to a bug, but this is a good thing. Looking like it'll come mid-late Q2 to early Q3 (although Charlie originally said March + 1.5-2 month delay?).

Ice Lake (läppärimalli) on ollut yli vuoden markkinoilla j niitä on myyty suuria määräiä.

Tarkoittaa siis vain serverimallia tässä.

knz0

300 yard drive

- Liittynyt

- 02.11.2016

- Viestejä

- 1 356

Ongelma on siinä että jutun lähteenä on Charlie Demerjian, joka on tunnettu Intel-vihaaja ja huonolla taustatutkimuksella varustettujen juoruartikkeileiden kynääjä. Ei siitä ole kuin kaksi vuotta kun heppu uutisoi että Intel olisi kuoppaamassa 10nm prosessinsa kokonaan. En siis asettaisi näille jutuille hirveästi paino-arvoa.

Charlie kuuluu tältä osin samaan kastiin kuin MLID, Adored ja Not an Apple Fan. Charlien erona on se, että hän veloittaa jutuistaan 1000 dollarin vuosittaisen tilausmaksun, kun taas pelaa Youtube-clickbaitpeliä. Lisäksi Charlien track record on loppujen lopuksi ehkä hieman parempi ja hänellä on pääsy esim osakeanalyytikkojen korville.

Charlie kuuluu tältä osin samaan kastiin kuin MLID, Adored ja Not an Apple Fan. Charlien erona on se, että hän veloittaa jutuistaan 1000 dollarin vuosittaisen tilausmaksun, kun taas pelaa Youtube-clickbaitpeliä. Lisäksi Charlien track record on loppujen lopuksi ehkä hieman parempi ja hänellä on pääsy esim osakeanalyytikkojen korville.

- Liittynyt

- 17.10.2016

- Viestejä

- 2 012

Ongelma on siinä että jutun lähteenä on Charlie Demerjian, joka on tunnettu Intel-vihaaja ja huonolla taustatutkimuksella varustettujen juoruartikkeileiden kynääjä. Ei siitä ole kuin kaksi vuotta kun heppu uutisoi että Intel olisi kuoppaamassa 10nm prosessinsa kokonaan. En siis asettaisi näille jutuille hirveästi paino-arvoa.

Charlie kuuluu tältä osin samaan kastiin kuin MLID, Adored ja Not an Apple Fan. Charlien erona on se, että hän veloittaa jutuistaan 1000 dollarin vuosittaisen tilausmaksun, kun taas pelaa Youtube-clickbaitpeliä. Lisäksi Charlien track record on loppujen lopuksi ehkä hieman parempi ja hänellä on pääsy esim osakeanalyytikkojen korville.

Intelhän on kuoppaamassa 10nm prosessin ennen koko portfolion siirtämistä sille, tilalle on tulossa 10nm superfin.

Tuollaiset toimenpiteet nopeasti jäävät osatotuuksiksi ja helposti viestistä jää eloon vain "kuopataan 10nm".

Mihinkään muuhun en ota kantaa, en ole seurannut kaverin touhuja.

- Liittynyt

- 28.12.2016

- Viestejä

- 90

Meinaatko että saisivat kiinni tämän nykytilanteen vai että saisivat kiinni AMD:n siinä pisteessä kun sekin on päivittänyt tuotteensa ja valmistustekniikkansa (varmaan jo pariin otteeseen siinä välissä)?

Viittasin että saavat kilpailevat prosessit vastakkain kaikissa segmenteissä (Intel 7nm, AMD Zen4 5nm).

10nm kohdalla tämä alkaa olla jo myöhäistä. Tuossa nyt maaltaan kuvaa siitä, että myös 7nm on myöhästymässä edellisestä arviosta 2022-2023. Ongelmana tuossa tietysti on se, että AMD on jo siirtynyt/siirtymässä TSMC 3nm jos se valmistuu suunnitellusti 2022.

Mielestäni on selvää, että Intel ei pääse tasoihin ja AMD vain jatkaa tämän kuilun kasvattamista.

Intelin puolella tarvitaan nyt oikeasti peliliikkeitä laivan kääntämiseksi.

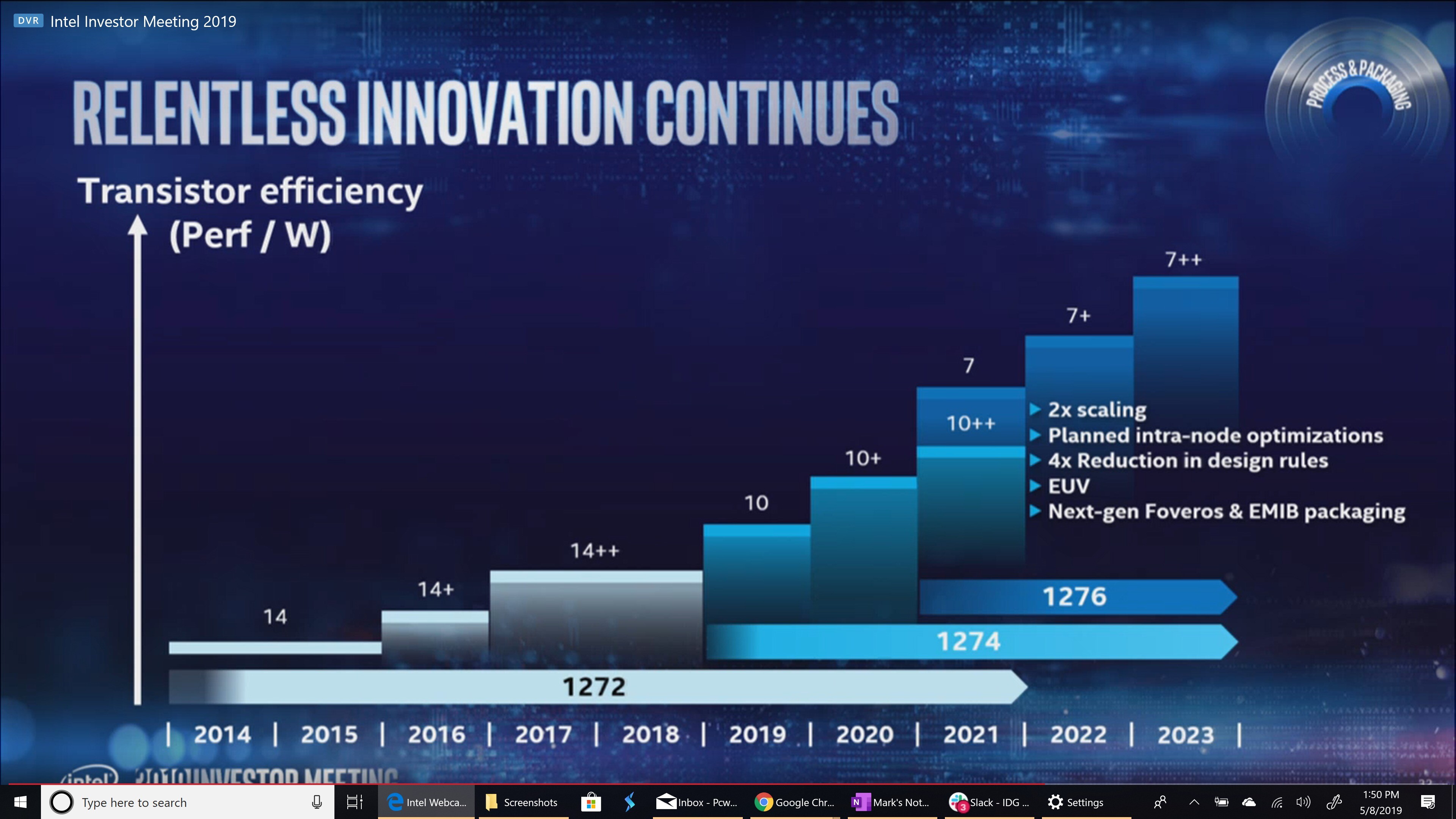

Kutsuuko Intel 10nm Superfiniä 10nm+:ksi vai 10nm++:ksi?Ja tässä sekoitetaan aivan täysin intelin toisen sukupolven "10nm" prosessia (käytössä ice lakessa) ja intelin 3. sukupolven "10nm" prosessia("Superfin"), käytössä Tiger Lakessa

Puhuaan "Superfinin ongelmista" mutta kun mikään Ice Lake ei ole valmistettu tuolla "superfin"-prosessilla"

- Liittynyt

- 22.10.2016

- Viestejä

- 12 914

Viittasin että saavat kilpailevat prosessit vastakkain kaikissa segmenteissä (Intel 7nm, AMD Zen4 5nm).

10nm kohdalla tämä alkaa olla jo myöhäistä. Tuossa nyt maaltaan kuvaa siitä, että myös 7nm on myöhästymässä edellisestä arviosta 2022-2023. Ongelmana tuossa tietysti on se, että AMD on jo siirtynyt/siirtymässä TSMC 3nm jos se valmistuu suunnitellusti 2022.

Mielestäni on selvää, että Intel ei pääse tasoihin ja AMD vain jatkaa tämän kuilun kasvattamista.

Intelin puolella tarvitaan nyt oikeasti peliliikkeitä laivan kääntämiseksi.

Mikään ei estä Inteliä tulevaisuudessa käyttämästä samaa TSMCn prosesia kuin mitä AMD käyttää.

Sen sijaan, mikäli Intel saa joskus taas prosessikehityksensä hyvälle mallille, on sillä joskus mahdollisuus päästä käsiksi parempaan valmistusprosesiin kuin AMDllä. Tämän toteutuminen lähivuosina ainakaan pitkäksi aikaa ei kuitenkaan vaikuta todennäköiseltä, teoriassa Intelillä voisi seuraavan kerran hetken ajan olla paras valmistusprosesi kun sen "7nm" valmistuu jos TSMCn "3nm" ei ole vielä valmis, mutta TSMCn "3nm" tullee hyvin pian sen jälkeen ja mennee edelle.

Realistinen (muttei kuitenkaan todennäköinen?) mahdollisuus pidempiaikaiseen valmistustekniikkaylivoimaan on sitten kun Intel saa oman "5nm" tekniikkansa valmiiksi.

Prosessorien (mikro)arkkitehtuuripuoli on sitten valmistustekniikoista aika erillinen asia. AMD yllätti zen3lla aika hyvin, Intelin Covet ja AMDn zen3 on melko tasoissa, mutta mitä niiden jälkeen, siitä ei ole riiittävästi tietoa.

Mikroarkkitehtuuri on yksi asia, mutta toinen missä AMD yllätti Intelin housut kintuissa oli Chiplet-pohjainen prosessoriarkkitehtuuri. Intelin prosessorit ovat edelleen monoliittisia, mikä tekee hyvin hankalaksi valmistaa niitä samoilla ydinmäärillä mitä AMD tekee - ja vaikka se teknisesti onnistuisi, olisi tuollainen saantojen vuoksi kilpailukyvytön AMD:n kanssa.Prosessorien (mikro)arkkitehtuuripuoli on sitten valmistustekniikoista aika erillinen asia. AMD yllätti zen3lla aika hyvin, Intelin Covet ja AMDn zen3 on melko tasoissa, mutta mitä niiden jälkeen, siitä ei ole riiittävästi tietoa.

Ensimmäisten vuotojen pohjalta Sapphire Rapids on idealtaan pitkälti ensimmäisen sukupolven EPYCin kaltainen: Ei erillistä I/O-sirua vaan kaksi isoa monoliittista sirua pultattu yhteen samoihin prosessorikuoriin. Seuraava sukupolvi Sapphire Rapidsin jälkeen siirtynee täysin AMD:n Rome/Milan-prosessorin malliin - mutta auttamattoman myöhässä.

EPYCin ensimmäisen sukupolven julkaisun jälkeen Intel haukkui AMD:n mallin lyttyyn - ja tuossa vaiheessa osaksi syystäkin - mutta nyt ovat tekemässä AMD:n perässä vaihe vaiheelta aivan samat temput.

Cirrus

Miksei maailma toimi asmilla?

- Liittynyt

- 16.10.2016

- Viestejä

- 3 398

TSMC:n kapasiteetti tuo reaalimaailmassa rajoitteita kaikille.Mikään ei estä Inteliä tulevaisuudessa käyttämästä samaa TSMCn prosesia kuin mitä AMD käyttää.

Ja reaalimaailman rajoitteen tuo myös se, ettei Intel ole ainakaan toistaiseksi ilmoittanut luopuvansa omista tehtaistaan. Miksi TSMC rakentaisi lisää kapasiteettia väliaikaiselle asiakkaalle, kun heillä on pitkäaikaisiakin asiakkaita jonossa?TSMC:n kapasiteetti tuo reaalimaailmassa rajoitteita kaikille.

- Liittynyt

- 28.12.2016

- Viestejä

- 90

Tämä tässä vähän pelottaakin. AMD on täysin riippuvainen TSMC:stä ja nurkkaan ahdistettu Intel, lähes pohjattomalla kassalla voi olla iso riski AMD:lle. Toivon että sopimukset on kunnossa eikä rahalla pääse jonon ohi ostamaan kapasiteettiä.Mikään ei estä Inteliä tulevaisuudessa käyttämästä samaa TSMCn prosesia kuin mitä AMD käyttää.

Arkkitehtuuri puoli on sitten toinen homma. Intelin nykyinen monoliittinen isojen piirien tie on kyllä loppusuoralla. Varsinkin XCC lastut tulevalla 10nm SuperFin jos huhut saannoista pitävät paikkansa. Jo nyt Intel joutuu turvautumaan "liimaaman" ytimiä samalle socketille (muistakaa mistä tämä toteamus tuli, kun Zen 1 julkaistiin). Tähän ongelmaan Intelillä ei ole vielä hyvää ratkaisua.

Edit: @MOS6510 tuossa jo hyvin tiivistikin asian.

Viimeksi muokattu:

Uutiset

-

OnePlus Suomen toiminta supistuu – valmistajan puhelimet käyneet Suomessa kuitenkin kaupaksi

11.5.2026 15:51

-

HyperX esitteli uuden peliohjaimen tehokäyttäjille ja edullisemman pään pelikuulokkeet

11.5.2026 14:12

-

Live: io-techin Tekniikkapodcast (18-19/2026)

8.5.2026 11:16

-

Tietoturvatutkija: Chrome asentaa salaa 4 Gt:n Gemini Nano -tekoälymallin

8.5.2026 00:38

-

Qualcomm julkaisi uudet Snapdragon 6 Gen 5- ja 4 Gen 5 -alustat edullisempiin mobiililaitteisiin

8.5.2026 00:06

Uusimmat viestit

-

-

Hiljainen, energiatehokas ja pieni pelitietokone valmiiksi koottuna?

- Viimeisin: Tigerman82

-

-

-