Siirsin vastauksen tänne, koska meni niin kauas alkup aiheesta.

Eli minun käsittääkseni Zen kolmoselle odotetaan taas sellaista samanlaista IPC parannusta kuin oli zen+ -> zen2 ja mahdollisesti taas hitusen lisää kellotaajuuksia, jolloin zen3 voisi olla ~20 nopeampi kuin vastaavan tuoteryhmän zen2.

Näin suurta IPC-parannusta odotetaan lähinnä

1) AMD-fanien toimesta

2) Sellaisten ihmisten toimesta, jotka eivät perusta arvioitan teknisiin faktoihin vaan "aina ennenkin parantunut" ymmärtämättä syitä milloin ja miksi ennen parantunut, eivätkä tajua sitä että yhden säikeen suorituskyvyn parantaminen on hommaa jossa jokainen parannus käy jatkuvasti entistä vaikeammaksi.

Vertailukohdaksi:

Intel yli puolitoistakertaisti ytimen efektiivisen koon että sai sen luokkaa 15% IPCtä lisää välillä Skylake->Sunny cove (~8.7mm^2 @"14nm" => 6.9mm^2 @ "10nm")

(toki AMD-fanien vastakommentti tähän on tietysti, että syy oli se, että Intel vaan ei osaa, mutta Intelin insinöörit kyllä osaavat ziljoona kertaa enemmän kuin nämä AMD-fanit; AMDn oli helppo parantaa Bulldozer-johdannaisista zeniin koska BUlldozer/Steamroller oli niin kämäinen ja lähtötilanne onneton, ja toisaalta AMDn oli helppo parantaa zenistä zen2een koska zenistä oli jouduttu aikataulusyistä jättämään pois asioita mitä siihen oli alunperinkin kaavailtu. Zen2ssa on nyt "helpot parannukset" otettu pois ja ydin jo jo hyvä ja nyt jokainen parannus on paljon vaikeampi.

Itse odottaisiin siis pienempää keskimääräistä IPC-parannusta, MUTTA selvästi parempaa käyttäytymistä nimenomaan niissä peleissä, joissa zen2 oli hitaampi kuin skylake-johdannaiset, koska AMD tuntuu keskittyvän nimenomaan näiden pullonkualojen korjaamiseen.

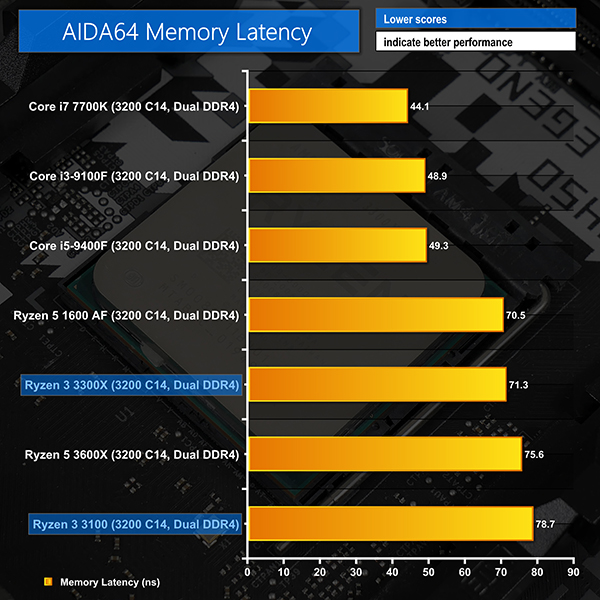

Esim. siirtyminen kahdeksan ytimen CCXään nopeuttaa >4 ytimen välistä kommunikaatiota, ja kasvattaa yhden ytimen käytössä olevan L3-kakun määrää (eli siten osumatarkkuutta), mutta toisaalta tarkoittaa että L3-kakun viive kasvanee hiukan, ja toisaalta jos on ajossa joku kaistarohmu säie, se saa heitettyä useamman muun säikeen datat sieltä pihalle. Näissä ei ole juuri koskaan absoluuttisesti parempia ja huonompia ratkaisuita, vaan ratkaisuita joilla on hyvät ja huonot puolensa.

Tämän pitäisi riittää pelisuorituskyvyssä sitten about tasoihin jo Intelin kanssa.

Tämän pitäisi helposti riittää tasoihin Comet Laken kanssa/ohi Comet Lakesta.

Willow Cove-ytimet vaan on selvästi järeämpiä ja nopeampia kuin Skylake-ytimet, joten odotettavissa on, että Rocket Lake ja Tiger Lake ovat taas kauempana, tosin Rocket Lake on melkoinen arpa sen suhteen, että miten se "14nm" tekniikalla kellottuu ja paljon kuluttaa sähköä.

Näistä Tiger Lake ehtinee ulos ennen zen3sta, ja sillä Intel vienee "peliläppärisegmentin" selvästi.

Tsäkällä joissain peleissä edellekin. Hyötyohjelmissa on AMD jo ollutkin edellä ja tämä ero vain kasvaa.

Juu, siis monisäikeistetyissä hyötyohjelmissa.

Se, että Cove-sarjan ytimet on niin paljon järeämpiä tarkoittaa, että Intel ei voi tunkea niitä kovin montaa yhdelle piilastulle, ja AMD pystyy samoilla valmistuskustannuksilla valmistamaan >1.5-kertaisen määrän tehoytimiä lähitulevaisuudessakin, ja pitämään helposti muutamankymmenen prosentin edun vaikka IPC onkin hiukan huonompi,

Se, minkä intel saa tiheydessä takaisin kun saa "10nm" prosessinsa toimimaan myös työpöydällä se käytännössä melkein menettää siirtymisessä isompiin "Cove"-sarjaan ytimiin (joihin kuitenkin haluaa siirtyä paremman säiekohtaisen suorituskyvyn takia).

Alder Lakessa Inteliltä sitten tulee myös Gracemont-pikkuytimiä, mutta Alder Lakessa AVX-512 on kytketty pois päältä mikäli pikkuytimet on käytössä, mikä on huono maksimaalisen rinnakkaisen suorituskyvyn kannalta.

Toisaalta, AVX-512sta tukevissa hyötysoftissa Intelillä olisi voinut olla etu ainakin Tiger Laken kanssa läppäreissä, jos niitä AVX-512sta tukevia hyötysoftia olisi, mutta kun niitä ei juuri HPC-sektorin ulkopuolella ole (mistä intel saa lähinnä syyttää itseään tavalla miten on markkinasegmentoinut käskykantojaan ja viivyttämyt AVX-512n tuloa työpöydälle).

Sellaista minä odotan. Jos siitä sen sijaan tulisi xt-tyyppinen nolla-parannus niin se olisi kyllä surkuhupaisaa. En jaksa uskoa.

Kyllä sieltä tullee ihan kelpoa parannusta, mutta ei silti kannata odottaa liikoja.

Yhden säikeen suorituskyvyn kasvattaminen vaan on vaikea asia.

Inteliltä toivottavasti tulee järkevä vastaus ensi vuonna.

Tiget lake tosiaan tulee jo etukäteen, Rocket Lake sitten talvella.

Rocket Lake varmaan ottaa taas absoluuttisen yhden säikeen/pelisuorituskyvyn kuninkuuden itselleen, mutta monen säikeen suorituskyvyssä jää vaan kauemmas taakse, kun "14nm" tekniikalla noita Willow Cove-ytimiä saadaan samalle piirille vaan 8 ja AMD pystyy samassa hintaluokassa tuomaan jopa 16 ydintä kahden CCDn konfiguraatiolla.

Tai ylemmässä keskiluokassa AMD pystyy tarjoamaan yhden CCDn mallia 8 ytimellä melko mukavilla valmistuskustannuksilla ja Intelillä on tätä vastaan heittää ehkä n. 6-ytiminen Rocket Lake joka on silti selvästi kalliimpi valmistaa.

Alder Lake tullee sitten joskus reilusti yli vuoden, ehkä n. puolntoista vuoden päästä.

Missäs sukupolvessa se olikaan, olikos ehkä se Zen 4 sitte missä piti AMD:ltä tulla I/O ytimen päälle stacked SRAM muistia? (jossain Moore's Law is Dead kanavan videossa siitä oli juttua, mutta en nyt nopeesti löydä sitä)

Sitä odotan mielenkiinnolla, että miten vaikuttaisi pelisuorituskykyyn.

"Moores Law is Dead"in videoista ei kannata uskoa

yhtään mitään

Tyyppi on täysin pihalla kuin lumiukko ja uskoo ja höpisee eteenpäin ihan mitä tahansa satuja sille syöttää.

SRAMin voi valmistaa (ja se kannattaa valmistaa) ihan samalla (mahdollisimman uudella ja tiheällä) logiiukkaprosessilla kuin itse ytimet valmistaa ja sijoittaa ihan sille samalle piirille kuin millä ytimet on (kuten AMD on zen2ssa tehtyt; yli puolet CCD-piilastujen pintala-alasta on L3-kakkua).

Että ei ole tulossa mitään stacked SRAMia zen4een.

eDRAM taas on menneen talven lumia, ei skaalaudu valmistustekniikan mukana joten sitä ei oikein kannata valmistaa nykyaikaisilla valmistustekniikoilla kun SRAMin saa käytännössä yhtä tiheään mutta SRAM on paljon nopeampaa, vähävirtaisempaa ja helpåompaa käyttää.

Eli jos jotain muistia tulisi pirin päälle, se olisi sitten melko perinteistä DRAMia, esim. HBM2-rajapinnalla. Mutta tämäkin tarkoittaisi sitä, että sitä muistia ei voi laajentaa.

Oma visioni on se, että jossain vaiheessa nykyinen DRAM korvautuu yhdistelmällä

1) prossun kanssa samassa paketissa oleva HBM(2|3),

2) muistikammoilla oleva NVRAM; (Optane tms.).

Kun DRAM on prossun kanssa samassa paketissa, sille saadaan tarpeeksi kaistaa, että voidaan tehdä

oikeasti tehokas integroitu näyttis ja toisaalta tällaisessa systeemissä jossa ei ole erillistä näyttismuistia, rinnakkaislaskennan offloadaaminen näyttisytimille on helpompaa ja nopeampaa.

Ja se, että DRAMin määrää ei voi laajentaa ei haittaa siinä vaiheessa kun muistikammoilla olevalta NVRAMilta (jota voidaan laajentaa, ja jota saa helposti vaikka 128 gigaa melko halvallakin hinnalla) voidaan ajaa kaikki koodi suoraan, sekä niille tunkea myös se vähemmän käytetty käyttömuisti ja sitä voidaan sieltäkin suoraan käyttää(sen sijaan että se swapattaisiin levylle josta sitä ei voi käyttää suoraan), joten sen käyttäminen on silti tuhansia kertoja nopeampaa kuin SSDlle swapatun muistin lataaminen sieltä DRAMille sen käyttämiseksi.

Tuo NVRAMin tehokas käyttäminen tälla tavalla toki vaatii käyttistukea, joka ei vielä ole riittävällä tasolla, käytännössä mm. uutta tiedostojärjestelmää.