- Liittynyt

- 21.02.2017

- Viestejä

- 6 174

Eikö toi vajaa 200 CU:n lippulaivapiiri olisi melko realistinen tai välttämätön siinä skenaariossa, jossa RDNA 5:llä AMD yrittäisi taas kilpailla kovemmin kuten RDNA 2 sukupolvessa?

Follow along with the video below to see how to install our site as a web app on your home screen.

Huomio: This feature may not be available in some browsers.

hmm toisaalta miksi kepler_l2 näitä repostailee X:ssä jos ei ole luotettava? Toki MLIDiin on aina hyvä suhtautua skeptisesti.Kuulostaa yhtä uskottavalta clickbait materialilta kuin navi3x kellotaajuudet, no vähintään respinnin jälkeen kelloa luvassa, eiku viimeistään navi4x:ssa, eikun. En pidättele hengitystä 512bit amd pelipiiriä odotellessa. MLID:n track record niin huono ettei kannata kiinnittää mitään huomiota siihen. Jos paremmat huhupajat alkavat tuollaisista puhumaan niin uskottavuus voisi olla nollaa suurempi.

Kepler tais postata spekulaation 384bit rdna5:sta jonka kertoi olevan täyttä keksintöä omasta päästä. Onko sulla linkata missä kepler väittää amd:lta olevan tulossa 512bit väyläisen ratkaisun? Aika paljon kertoo huhujen tasosta kun wccftech, videocardz tms, huhusaitit ei nosta tätä MLID:n clickbait keksintöä sivuillensa.hmm toisaalta miksi kepler_l2 näitä repostailee X:ssä jos ei ole luotettava? Toki MLIDiin on aina hyvä suhtautua skeptisesti.

Noh kaikki on spekulaatiota, mä itse veikkaan enemmän tuota 96 CU:ta, noi 600w monsterit on vähä meh varsinkin näillä helteillä:

AMD's Upcoming UDNA / RDNA 5 GPU Could Feature 96 CUs and 384-bit Memory Bus

According to one of the most reliable AMD leakers, Kepler_L2, AMD's upcoming UDNA (or RDNA 5) GPU generation will reintroduce higher-end GPU configurations with up to 96 Compute Units (CUs) in the top-end Navi 5X SKU, paired with a 384-bit bus for memory. We still don't know what type of memory...www.techpowerup.com

Kunhan vaan AMD:kin lähtis 5090 tasoisten korttien kilpaan mukaan. AMD sais laitta reilummin muistia mitä Nvidia tulis vähän pöhinää sektoriin. AMD on tehnyt saman ennenkin silloin kun se lisäsäsi prosessoriytimiä vrt Inteliin. Samaten intelin pitäisi nimen omaan yrittää pelata muistin määrällä, että saisivat jotain myytyä. Intelin tuotteiden hitaus takaisi seuraavienkin mallien myyntiperusteen eikä poistaisi niiden tarvetta.

Kilpailu high endissä on ainoa asia joka ajaisi alas hintatasoa kaikilla näytönohjaintasoilla, koska ylemmän keskitason näytönohjainten hinnat määräytyy suhteessa high endiin ja alemman keskitason hinnat suhteessa ylempään keskitasoon, jne. Niin kauan kuin NVIDIAlla on monopoli high endissa, NVIDIA määrää hinnat ja kuluttajahan siitä kärsii. Eli toivomalla, että AMD ei kilpaile high endissä, toivot samalla että kaikki näytönohjaimet pysyvät tarpeettoman kalliina.Mielestäni ei todellakaan tarvitsisi. Toki se saisi näkyvyyttä ja löytyisi ehkä kourallinen ihmisiä maailmasta jotka sitten ostaisivat jonkun 36Gb muistilla olevan 4500€ maksavan vesijäähyä vaativan "tämä on 10% tehokkaampi kuin 5090 ja pystyy luomaan jopa 10 framea lisää jokaisen oikean framen väliin" kortin mikä vaatisi mieluusti sen 1600W virtalähteen ja "vain" 4-6 virtaliitintä vieden sen 4 korttipaikkaa ja 56cm kotelon pituutta...

Jo nytkin nämä "hinnat alkaen" 720€ ylemmän keskiluokan kortit ovat aika paljon rahaa vievä harrastus kun miettii sitä keskiverto pelaajaa joka pohtii sen 1000€ konepaketin kokoamista mihin pitäisi saada mahtumaan vielä näyttö, näppäistö, hiiri ja kuulokkeet vs sitten PS5 konsolia.. voi konsoli vielä monella voiton jos hinnat vielä kasvavat.

Kilpailu high endissä on ainoa asia joka ajaisi alas hintatasoa kaikilla näytönohjaintasoilla, koska ylemmän keskitason näytönohjainten hinnat määräytyy suhteessa high endiin ja alemman keskitason hinnat suhteessa ylempään keskitasoon, jne. Niin kauan kuin NVIDIAlla on monopoli high endissa, NVIDIA määrää hinnat ja kuluttajahan siitä kärsii. Eli toivomalla, että AMD ei kilpaile high endissä, toivot samalla että kaikki näytönohjaimet pysyvät tarpeettoman kalliina.

Tuo mitä sanot ei ole mitenkään ristiriidassa sen kanssa mitä sanoin. Se, että kilpailu high endissä ajaisi hintoja alas kaikilla tasoilla, ei tarkoita etteikö kilpailu low endissä olisi low endille hyvä asia, tai että ei voisi tapahtua muita yksittäisiä hintojen korjauksia.Mutta kun tuo EI ole toiminut noin tähänkään saakka.

Intel on tuonut halpoja hyviä näytönohjaimia eikä todellakaan kilpaile high end (eikä edes hig medium) tasolla. AMD on yleensä myös jos ei heti niin ajan kanssa laskenut mukavasti hintoja. Ainoastaan Nvidia tuntuu loppuun saakka pitävän ne kalliit hinnat...

Katsoo vaikka 7700XT sitä saa noin 400€ 7800XT jopa 500€, kun taas jos katsoo 4070 / 4070Super / 4080 hintoja niin ei löydy tai hinnat edelleen pilvissä..

Mutta kun tuo EI ole toiminut noin tähänkään saakka.

Intel on tuonut halpoja hyviä näytönohjaimia eikä todellakaan kilpaile high end (eikä edes hig medium) tasolla. AMD on yleensä myös jos ei heti niin ajan kanssa laskenut mukavasti hintoja. Ainoastaan Nvidia tuntuu loppuun saakka pitävän ne kalliit hinnat...

Katsoo vaikka 7700XT sitä saa noin 400€ 7800XT jopa 500€, kun taas jos katsoo 4070 / 4070Super / 4080 hintoja niin ei löydy tai hinnat edelleen pilvissä..

Eikö toi vajaa 200 CU:n lippulaivapiiri olisi melko realistinen tai välttämätön siinä skenaariossa, jossa RDNA 5:llä AMD yrittäisi taas kilpailla kovemmin kuten RDNA 2 sukupolvessa?

Eikai peruskuluttajan rtx xx60 mallit nyt niin kalliita ole inflaatio huomioonottaen? maksoin joskus 2012/2013 vuodenvaihteessa 230e gtx 660 2gb näyttiksestä. 2018 tammikuussa maksoin sellaiset 300e gtx 1060 6gb mallista (joku voisi sanoa tämän olleen ti-malli, kun sellaista ei tullut). rtx 3060 oli sellaiset 300-350e niille ketkä kerkesivät sen ostamaan ennen hintojen nousuja ja alle 350 euron saa nyt rtx 5060 mallia. Ongelma koskee noita tehokkaampia näyttiksiä. gtx 1080ti näyttistä sai alle tonnilla. rtx 5090 on jo yli kaksi tonnia (tosin virrankulutus ja jäähdytyksen koko on kasvanut ja piirikin on isompi, gtx 1080ti=471mm vs rtx 5090=750mm).Kilpailu high endissä on ainoa asia joka ajaisi alas hintatasoa kaikilla näytönohjaintasoilla, koska ylemmän keskitason näytönohjainten hinnat määräytyy suhteessa high endiin ja alemman keskitason hinnat suhteessa ylempään keskitasoon, jne. Niin kauan kuin NVIDIAlla on monopoli high endissa, NVIDIA määrää hinnat ja kuluttajahan siitä kärsii. Eli toivomalla, että AMD ei kilpaile high endissä, toivot samalla että kaikki näytönohjaimet pysyvät tarpeettoman kalliina.

Juu tuosta vinkkelistä lähinnä kattelin, eli että RDNA 3:ssa saatu tungettua 96CU 305mm2:iin, joten tuon tuplaaminen pienemmällä prosessilla ei tuntuisi mahdottomalta. Turhan yksinkertaistavaa tuijotella CU määriä toki.Ja ei kannata tosiaan vertailla RDNA4sta vanhempien AMDn "huippu"piirien CU-lukuihin suoraan CU per CU

Juu tuosta vinkkelistä lähinnä kattelin, eli että RDNA 3:ssa saatu tungettua 96CU 305mm2:iin, joten tuon tuplaaminen pienemmällä prosessilla ei tuntuisi mahdottomalta. Turhan yksinkertaistavaa tuijotella CU määriä toki.

Onko RDNA 5:n kohdalla RDNA 3:a muistuttava chiplet ratkaisu, mutta isompana, poissuljettu? Esim joku 500-600mm2 GCD + MCD:t päälle?RDNA3n CU on ihan eri asia kuin RDNA5n CU, ja siinä 305mm2ssa ei ole mukana muistiohjaimia eikä L3-välimuistia. Kokonaisuudessaan piipinta-alaa navi31ssä on n. 500 mm2

Johan AMD yritti chiplettiä ja julkaisuun ei edes päässyt, kun vituiksi meni..Ihme jos ei siirry chiplettiin ainakin lippulaivamallien osalta. Massiivipiirien teko on liian kallista ja hankalaa

RTX 5060 8GB on ihan OK hintainen. Voisi se olla halvempikin, ei voida ajatella että se olisi jotenkin aggressiivisesti hinnoiteltu. Mutta kilpailu high endissä vaikuttaisi todennäköisesti vähiten juurikin noihin ihan lähtötason kortteihin. Eniten RTX 5090:aan ja 5080:aan, nämä kun ovat ne hinta-suorituskykysuhteeltaan selvästi huonoimmat kortit joille AMD:llä ei ole vastinetta, ja siitä sitten portaittain alaspäin vähenevissä määrin.Eikai peruskuluttajan rtx xx60 mallit nyt niin kalliita ole inflaatio huomioonottaen? maksoin joskus 2012/2013 vuodenvaihteessa 230e gtx 660 2gb näyttiksestä. 2018 tammikuussa maksoin sellaiset 300e gtx 1060 6gb mallista (joku voisi sanoa tämän olleen ti-malli, kun sellaista ei tullut). rtx 3060 oli sellaiset 300-350e niille ketkä kerkesivät sen ostamaan ennen hintojen nousuja ja alle 350 euron saa nyt rtx 5060 mallia. Ongelma koskee noita tehokkaampia näyttiksiä. gtx 1080ti näyttistä sai alle tonnilla. rtx 5090 on jo yli kaksi tonnia (tosin virrankulutus ja jäähdytyksen koko on kasvanut ja piirikin on isompi, gtx 1080ti=471mm vs rtx 5090=750mm).

olisihan se mukavaa jos näyttikset ei maksaisi niin paljoa, muttei tuolle oikein mitään voi, valmistuskustannuksetkin uusilla prosesseilla vain nousevat

Onko RDNA 5:n kohdalla RDNA 3:a muistuttava chiplet ratkaisu, mutta isompana, poissuljettu? Esim joku 500-600mm2 GCD + MCD:t päälle?

Lähinnä tässä yritän siis miettiä skenaariota, jossa AMD skabaa kärjen tuntumassa (voi hyvin olla että ei yritä tätä). Tuote kallis valmistaa juu, mutta Nvidian tapaan siitä sitten pyydettäisiinkin riistohintaa ja mahdollisesti samaa tuotetta myös myytäisiin datakeskus-/ammattilaissektoreilla.

Mun mielestä kyllä selkeästi parempi, että pidetään kuluttaja- ja Pro-/AI-rauta tyystin erillään. Kryptomania on koko ATK-historian mustinta aikaa miesmuistiin. Varmaan kaikista, normaalisti suurinpiirtein rehellisistä kauppiaista tuli lähes kertaheitolla rikollisia (pyyhkivät kuluttajansuojalailla perseitään) eikä ns. normaalit ihmiset yksinkertaisesti pystyneet ostamaan näytönohjaimia lainkaan, mutta kryptoroistoille niitä riitti kyllä tiskien alta kymmenittäin. Tai jos jotain romurautaa sai ostettua, niin moninkertaiseen hintaan. Tämän hulluuden seurauksia maksamme vieläkin erityisesti NVidian tuotteiden pöhöttyneissä hinnoissa.AI-laskenta on se mihin itse kaipaan halvempaa ja parempaa rautaa. Sen verta köyhä olen, että ei ole varaa 96GB 9000 euroa maksavaan RTX PRO 6000 korttiin. Nythän Ai laskennasta on kehittymässä vähän samaan tapaan kotihässläämisen boomi mitkä cryptotkin olivat.. tai no ainakin siinä on samoja piirteitä. Jengi kasaa 8 x 4090 / 8x3090 komboja koti LLM käyttöön. Köyhänä saattaisin hyvinkin harkita 3500 euron 5090 nopeuksista AMD korttia jossa 64GB muistia (siis siitä RDNA5 sukupolvesta). 5070ti nopeuksinen kortti 96GB:lla muistia edulliseen hintaan myisi kuin häkä. Maailmalla on huutava pula sellaisista tuotteista. Porukka joutuu pohtimaan AMD 395+ Ai super duper hyper max läppäri-piireistä tehtyjä pöytäkoneita, koska siinä on 128GB muisti, josta 96GB voi käyttää integroidun näyttiksen kanssa mihin vaan.

Ei. Mutta nopeampi piiri vaatii myös enemmän muistikaistaa. Enemmän/kalliimpia MCD-piirejä.

Ja joku 500-600 mm2 N3sta (+ ne MCDt päälle) tulisi järkyttävän kalliiksi ja olisi täysin normaalien kuluttajien hintaluokan ulkopuolella, aivan kuten 5090, koska tuo olisi käytännössä 5090stäkin selvästi kalliimpi valmistaa.

Ei välttämättä tarvita sen enempää MCD piirejä koska 20gbps GDDR6 -> 30gbps GDDR7 tuo jo 50% lisää kaistaa.

Tosin jos 5090 (6090) kanssa haluaa kilpailla niin miksi AMD:n 2x ~300mm2 GCD + 8x ~30mm2 MCD olisi selvästi kalliimpi valmistaa kuin Nvidian ~750mm2 monoliittipiiri?

Nuo MCD piirithän voisi olla huomattavasti edullisemmalla valmistusprosessilla kuin GCD:t.

Huhujen mukaanhan RDNA4(5) lippulaivan piti olla kahdella GCD:llä.

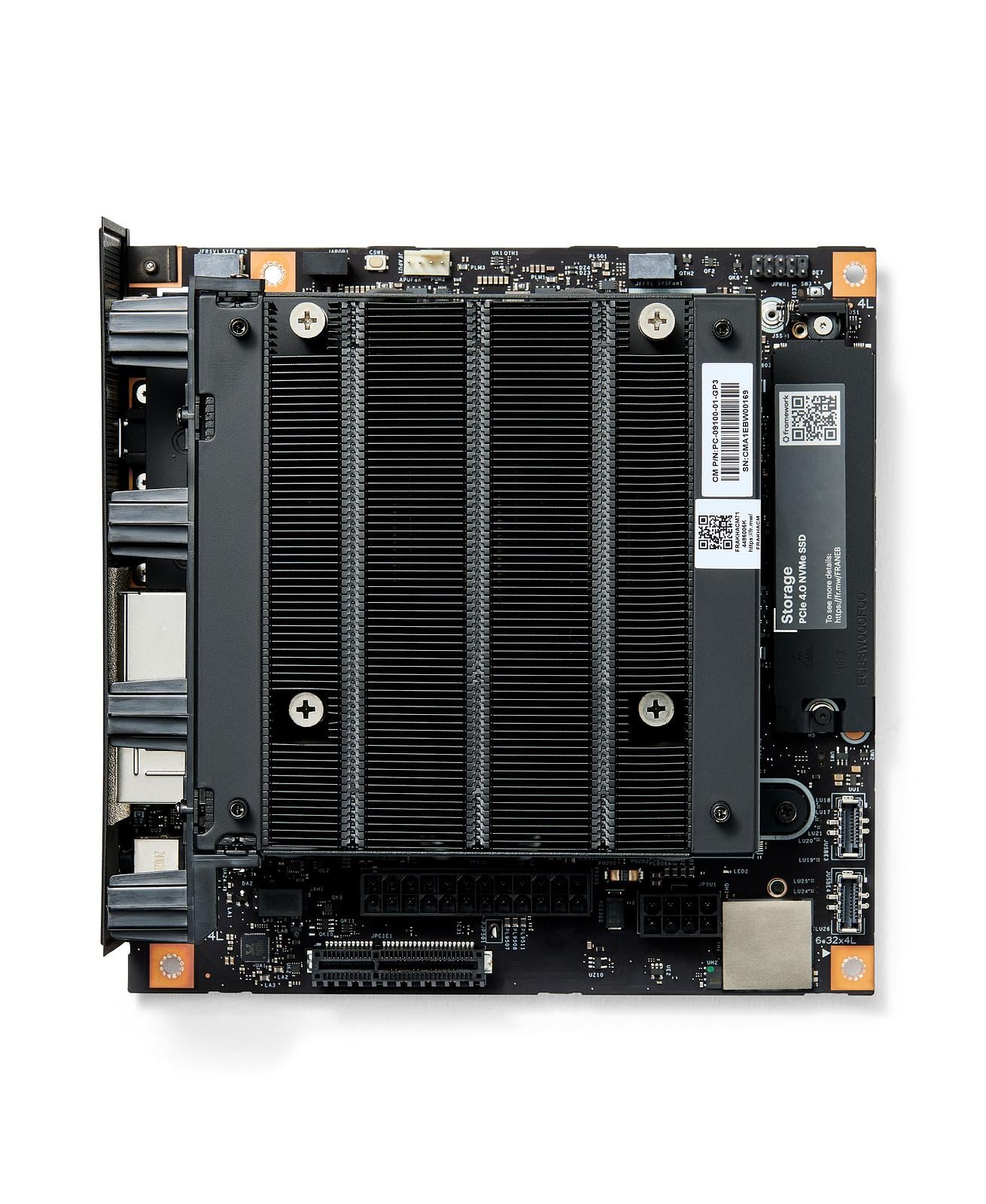

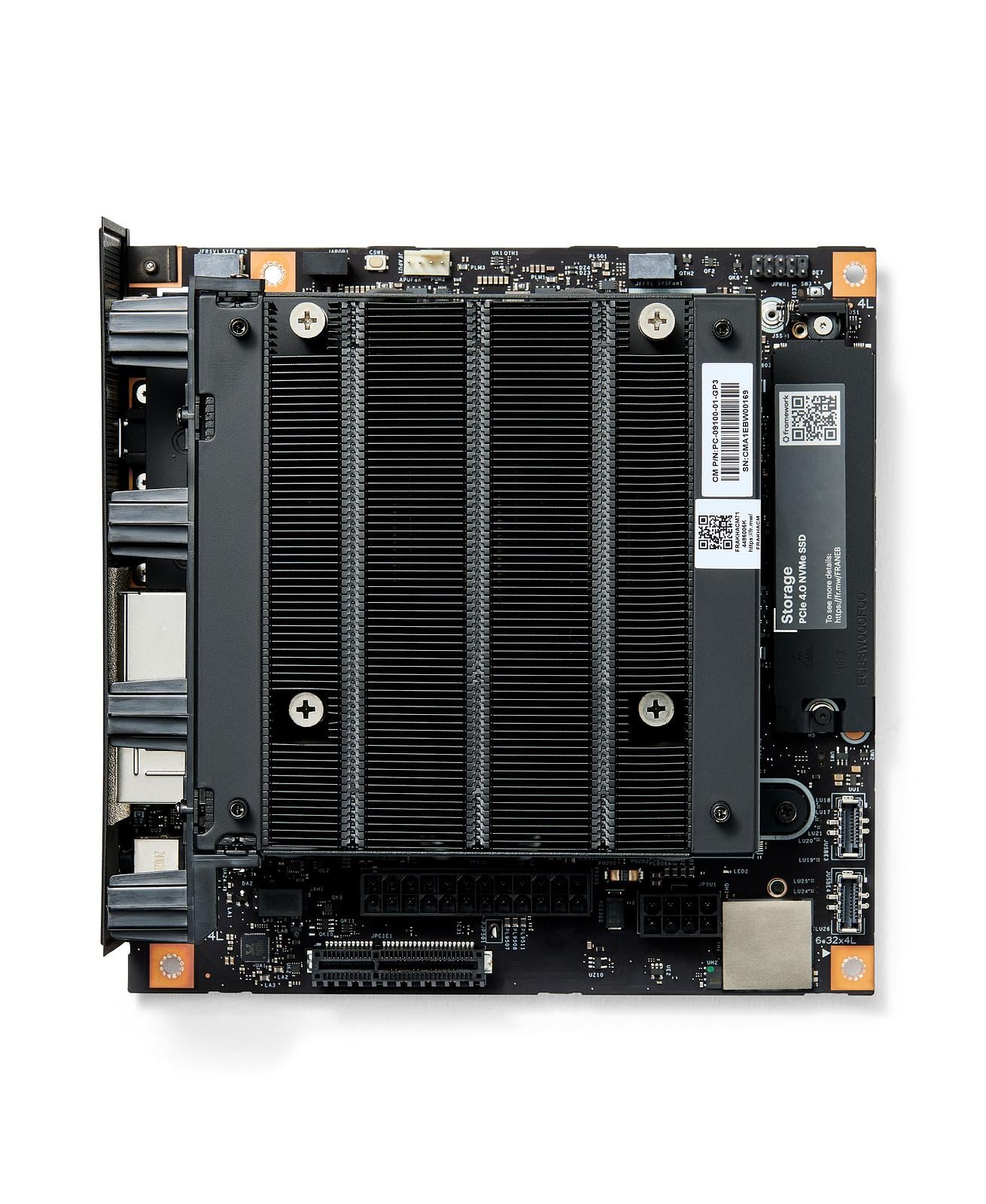

Tuosta kirjoitinkin, että moni joutuu katselemaan AMD Halo SER:riä. Noin kalliiksi tuotteksi aivan liian hidas ~2000 euron hintaiseksi todella liitin köyhiä nuo. Jos esim katsot frameworkin erillisemona myytävää.Jos kaipaa vaan paljon muistia, niin Strix Halo prosu hankintaan. Olisikohan jossain minisforumin koneessa paras hinta/laatusuhde, todennäköisesti edullisempi kuin läppäri vastaavilla osilla ja taatusti halvempi kuin kolme 5090 korttia.

Tuosta kirjoitinkin, että moni joutuu katselemaan AMD Halo SER:riä. Noin kalliiksi tuotteksi aivan liian hidas ~2000 euron hintaiseksi todella liitin köyhiä nuo. Jos esim katsot frameworkin erillisemona myytävää.

Max+ 395 - 128GB

Framework Desktop Mainboard (AMD Ryzen™ AI Max 300 Series)

Available with AMD Ryzen™ AI Max 385 and Ryzen™ AI Max+ 395 processors, the Framework Desktop’s mainboard is designed for performance and upgradeability.frame.work

~2000 eur

3x Standard 4-pin fan header (Standard PWM)

1x Standard 9-pin header (Front Panel Header)

2x 20-pin USB Type-E header (Front panel USB header)

1x Standard 9-pin header (Front panel audio header)

1x Standard 4-pin header with 3 signals (ARGB header)

1x RTC Battery connector (Molex 51021-8602, RTC Battery is preinstalled)

1 x PCIe x4 slot (not exposed on default case)

HUOM!. Joissain minisforumin emoissa on sentään 16x PCIE liitin, vaikka kyseessä on läppäpuolen piirisarjasta kyhätty ITX emo. Halot on aina integroituja.

Ehkä seuraava iteraation tuosta Halosta tarjoaa enemmän vastinetta rahalle jos olis tyylin 3x NPU + 50% lisää muistia.

Todella typerää valitusta jälleen.

Mikään muu kuluttaja-PC-rauta ei tietääkseni tarjoa tuollaista muistimäärää ja kaistaa nimenomaan neuroverkkojen ajamiseen, niin ihan turha valittaa jostain "hitaudesta" jos kyseessä on ainoa kuluttajarauta millä malli toimii ja vertailukohteena on lähinnä unelmat tai paljon kalliimmat erikoiskiihdyttimet.

Ja se, että joku tekee prossulle emolevyn jossa on vähän liittimiä ei tee prossusta huonoa.

Tuon prossun IO-piiriltä löytyy kyllä 16x pcie-väylä.

Mihin ihmeen "hitaaseen ensimmäiseen iteraatioon"? Siellä on se PC-maailmassa ennennäkemättömän tehokas integroitu GPU hoitamassa niitä tekoälylaskuja.Ehkä se on sinusta typerää. Kerroin vain, että en todellakaan tyydy tuohon hitaaseen ensimmäiseen iteraatioon. Pihien valmistajien kohdalla pitää aina äänestää lompakolla. Nuo firmat eivät välitä sinusta / kuluttajista ja enemmänkin aina miettivät miten voisivat antaa vähemmän kovemmalla hinnalla. Ei noita yrityksia kannata ruveta fanittamaan ellei ne maksa siitä hyvää hintaa. "shilling for money"

Sanottakoon tähän väliin, että on tuossa Halossa jonkin verran hyvääkin. Se on melko hyvän hyötysuhteen lopputuote ja siinä mielessä uniikki markkinoilla. Täysi kuorma kuluttaa noin 115W ja se on kohtuu kova lukema.

Ehkä se on sinusta typerää. Kerroin vain, että en todellakaan tyydy tuohon hitaaseen ensimmäiseen iteraatioon.

Pihien valmistajien kohdalla pitää aina äänestää lompakolla.

Mihin ihmeen "hitaaseen ensimmäiseen iteraatioon"? Siellä on se PC-maailmassa ennennäkemättömän tehokas integroitu GPU hoitamassa niitä tekoälylaskuja

Ja niitä firmoja kiinnostaa aika paljon enemmän sinua rikkaampien ja asioista paljon sinua paremmin perillä olevien asiakkaiden lompakot kuin juuri sinun lompakkosi.

PC maailmassa onkin ollut hirveä vaje noissa integroiduissa. Eivät ole viitsiineet tarjota niitä kun se söisi liikaa erillisnäyttisten kakkua tai ainakin niin pelkäävät

. Enennäkemättömän tehokas juu mutta silti hidas.

Tällaisen salaliittohörhöilyn sijaan kannattaisi yrittää opetella ymmärtämän vähän sitä tekniikkaa, mistä höpisee

Tällaisen salaliittohörhöilyn sijaan kannattaisi yrittää opetella ymmärtämän vähän sitä tekniikkaa, mistä höpisee.

Tässä ei ole kyse pelkästään mistään "viitsimisestä" vaan myös oleellisista teknisistä rajoitteista.

Tehokas näyttis tarvii paljon muistikaistaa, ja:

1) normaaleilla laajennettavilla DRAM-keskusmuistityypeillä (DDR4, DDR5) se tehokkaan näyttiksen tarvitsema kaista tulee hyvin kalliiksi ja lisää virrankulutusta selvästi. Se, että siinä Strix Halossa on 256-bittinen muistiväylä (siinä missä muissa kuluttaja-PC-CPU-piireissä on vain 128-bittinen muistiväylä) on yksi oleellinen syy sen korkeaan hintaan.

2) grafiikkaoptimoiduilla DRAM-muisteilla (GDDR, HBM) joilla kaistaa on enemmän se muisti pitää kolvata emolevylle tai laittaa näyttiksen kanssa samaan pakettiin mikä tekee mahdottomaksi sen muistin laajentamisen tai vaihtamisen jälkikäteen. Lisäksi voi tulla ongelmaksi, että jos esim paketointivaiheessa menee jotain pieleen, on sekä muistit että itse prossupiilastu kaikki käyttökelvottomia.

Lisäksi ne graffaoptimoidut muistit on usein viiveiltään huonompia kuin "normaalit" CPU-optimoidut DRAM-muistit tai niiden (liian pitkät) purskekoot sopivat huonosti CPU:iden välimuisteille, voi esim. olla että CPUn ladatessa dataa muistista joudutaan käytännössä lataamaan tuplasti enemmän, tuhlaten kaistaa ja virtaa, mikäli pienin puskekoko on tuplasti isompi kuin CPUn välimuistilinjan koko. Ja se välimuistilinjan koko on käytännössä modernissa x86-64ssa lukittu 64 tavuun, sen vaihtaminen olisi hyvin ongelmallista.

Verrattuna mihin?

Tämän valittamisen sijaan, suunnittele itse nopeampi. Palaa takaisin haukkumaan tätä hitaaksi vasta kun olet onnistunut.

Ite näkisin että muistia tuossa on jo nyt runsaasti mutta kaistaa ja laskentatehoa suhteessa turhan vähän, mitä AI puuhasteluun tulee. Tasapaino siis päinvastaisella tavalla heikko kuin 4090:ssä.Tuosta

AMD Ryzen™ Al Max+ 395

tuotteesta tulee jossain kohtaa seuraava malli ja jos pyhä Liisa suo, niin isommalla maksimi muistilla.

Aika villiä huhua taas MLID tarinoi tänään tulevista AMD RDNA5 low end ja mid range korteista. Eli tuon "vuodon" mukaan myös erillisnäyttiksiin olisi tulossa LPDDR6 / LPDDR5X muistiohjaimet ja 128bit / 256bit / 384bit muistiväylät.

Eikö tuollaisen valmistaminen olisi kohtuu kallista jos on noin leveät muistiväylät, vaikka kuinka käyttäisi läppärimuistia?

Toki tuollaisessa etuna varmaan olisi se että voisi tehdä AI variantteja korteista todella suurilla muistimäärillä.

1755844638987.png

OpenAI diilissä sanottiin selkeästi, että mi450 ensimmäisen GW toimitukset alkavat 2026 toisella vuosipuoliskolla. Iso muutos amd:lle kun samalla tulee uusi räkki missä 72gpu:ta yhteenkytketty nopealla linkillä. Ensimmäinen oikea rackscale ratkaisu, edellinen ratkaisu ei oikein skaalannut suorituskykyisesti yli 8gpu:lle jaettuun kuormaan.Lisa Sun mukaan MI450 valmistetaan (ainakin osittain) 2nm prosessilla. Vuoden 2026 jälkimmäisellä puoliskolla ilmeisesti ovat toimittamassa tuota.

- Neural Arrays: A collection of compute units configured to share and process data to work together like a single AI engine.

- Radiance Cores: New dedicated ray traversal hardware to deliver high-performance real-time ray tracing and path tracing.

- Universal Compression: A new system that evaluates and compresses all available data within the GPU to dramatically reduce memory bandwidth usage.

Amd ja sony kertoivat amd:n gpu-raudan tulevista ominaisuuksista.

AMD Unveils Radiance Cores, Neural Arrays & Universal Compression For Next-Gen RDNA GPU Architecture: Faster RT, Better Upscaling, & Lower Bandwidth Needs

AMD has just announced three key features of its next-gen RDNA architecture: Neural Arrays, Radiance Cores & Universal Compression.wccftech.com

Linkki: https://youtu.be/ItXPvGrI6gY?si=aNQor_KeD5hgDP9S

Säteenseurannan osalta ratkaisu on hyvin samankaltainen kuin nvidialla. Videolla cerny selitti miten säteenseuranta menee uudella yksiköllä shadereiden rinnalla versus ennen säteenseuranta laskettiin shadereilla. Samalla gpu voi käyttää enemmän muistikaistaa kun säteenseuranta ja shaderit laskevat samaan aikaan jos ei ota kiinni muistista tai lämmöistä.Nämä ovat varmaan Nvidian leirissäkin korkealla olevia tavoitteita - RT ei ole varmaan koskaan liian hyvä (AMD:llähän tuo on ollut aina ongelmana ja on edelleenkin), ja GPU:n laskentatehoa käyttävien erilaisten AI-sovellusten myötä halutaan myös erinäisiä parannuksia liittyen toisaalta tarvittavan fyysisen muistin kokoon (eli otetaan kompressio käyttöön) ja toisaalta halutaan myös saada eri GPU prosessit jakamaan dataa paremmin ja kommunikoimaan keskenään tehokkaammin. AMD käsittääkseni häviää Nvidialle eri benchmarkeissa ja käytännön suorituskyvyssä eniten juuri esim. N-body simulaatiossa (joka ehkä toisaalta myös benchmarkeissa paremmin CUDA:lle optiomoitu) ja säteenseurannassa (RT= ray tracing).

We are excited to host our Financial Analyst Day on Tuesday, November 11, 2025. Join Chair and Chief Executive Officer Dr. Lisa Su and members of the AMD leadership team who will present the company’s strategy and growth opportunities, innovative product and technology roadmaps, and long-term financial plan.

Ei tuota jaksa kyllä kattoa kun "ai per second" on niin helvetin korkee.

Jos tuli kirjoittelen siitä huomenna uutistaNiinpä. Itsekin aloin katsoa mutta aloin sitten kuitenkin tekemään koneella muuta ja jossain vaiheessa vaihtui tuon sivukorvalla kuunteleminen telkkarin katsomiseen kun oli niin pelkkää AI-hypeä.

Tuliko tuolla josssain välissä jotain oikeaa asiaakin?

Käytämme välttämättömiä evästeitä, jotta tämä sivusto toimisi, ja valinnaisia evästeitä käyttökokemuksesi parantamiseksi.