- Liittynyt

- 17.10.2016

- Viestejä

- 10 882

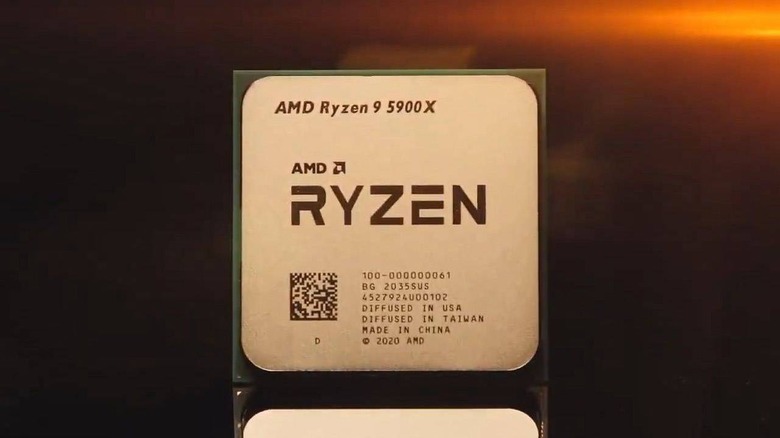

AMD:n julkkaritilaisuudessa 5950X esiteltiin "best for gamers meets best for creators". 5900X ei taida olla millään osa-alueella parempi lukuunottamatta hintaa.

En sano oletko oikeassa tai väärässä mutta tämän mukaan: "AMD Ryzen 5900X claimed "world's best gaming CPU" <= mistä omalla, kieltämättä ehkä hieman puutteellisellakin englannin kielelläni kääntäisin kyllä tuon "maailman paras peli prosessori". Tuo siis otettu ihan AMD:n esittelystä.

AMD Ryzen 5900X Claimed

Today AMD revealed ZEN 3 CPU Ryzen 5000 processors for desktop computers. These processors feature ZEN 3 architecture, rolling with 7nm process tech and a…

Edit: ja tässä vielä: AMD "Ryzen 9 5900X is the best gaming processor in the world".

kannattaa miettiä niitä tulevia konsoleita tässä vaiheessa kun ne on tossa viikkojen päästä eikä junnata vanhassa vain oman pointtinsa osoittamiseksi...

kannattaa miettiä niitä tulevia konsoleita tässä vaiheessa kun ne on tossa viikkojen päästä eikä junnata vanhassa vain oman pointtinsa osoittamiseksi...