- Liittynyt

- 05.12.2018

- Viestejä

- 2 378

AMD:llä on ollut jotain monimutkaisia lainapapereita, joita voi konvertoida osakkeiksi. Ts. AMD on efektiivisesti tehnyt osakeannin, jolla se on maksanut lainojaan pois. Osakeannista tienattu raha ei ole liiketoiminnan voittoa, vaan omaa pääomaa ja kirjautuu suoraan taseeseen. Samalla tietty osakemäärä on lisääntynyt ja earnings per share on laskenut, koska voitto jakautuu useammalle osakkeelle.

Syy noiden käyttöön oli se, että joskus 2015-2017 välillä firma oli oikeasti paskassa jamassa ja sen oli vaikea saada lainarahaa markkinoilta siedettävillä ehdoilla. Se sai laskettua myymiensä velkakirjojen korkoja sillä, että siellä oli tuo konversioehto, jolla velan ostaja sai muutettua lainasaatavat osakkeiksi niin halutessaan, joka tietty nyt on tehty kun osakkeet ovat raketoineet verrattuna lainojen antohetkeen.

Ks. Convertible debt annual reportista ja kaiva jostain tarkemmat ehdot.

Ilman niitä kirottuja pavunlaskijapukupellejä jotka tekevät noita finanssikikkailuja AMD olisi ollut oikeasti kusessa. Heille on ihan käyttönsä.

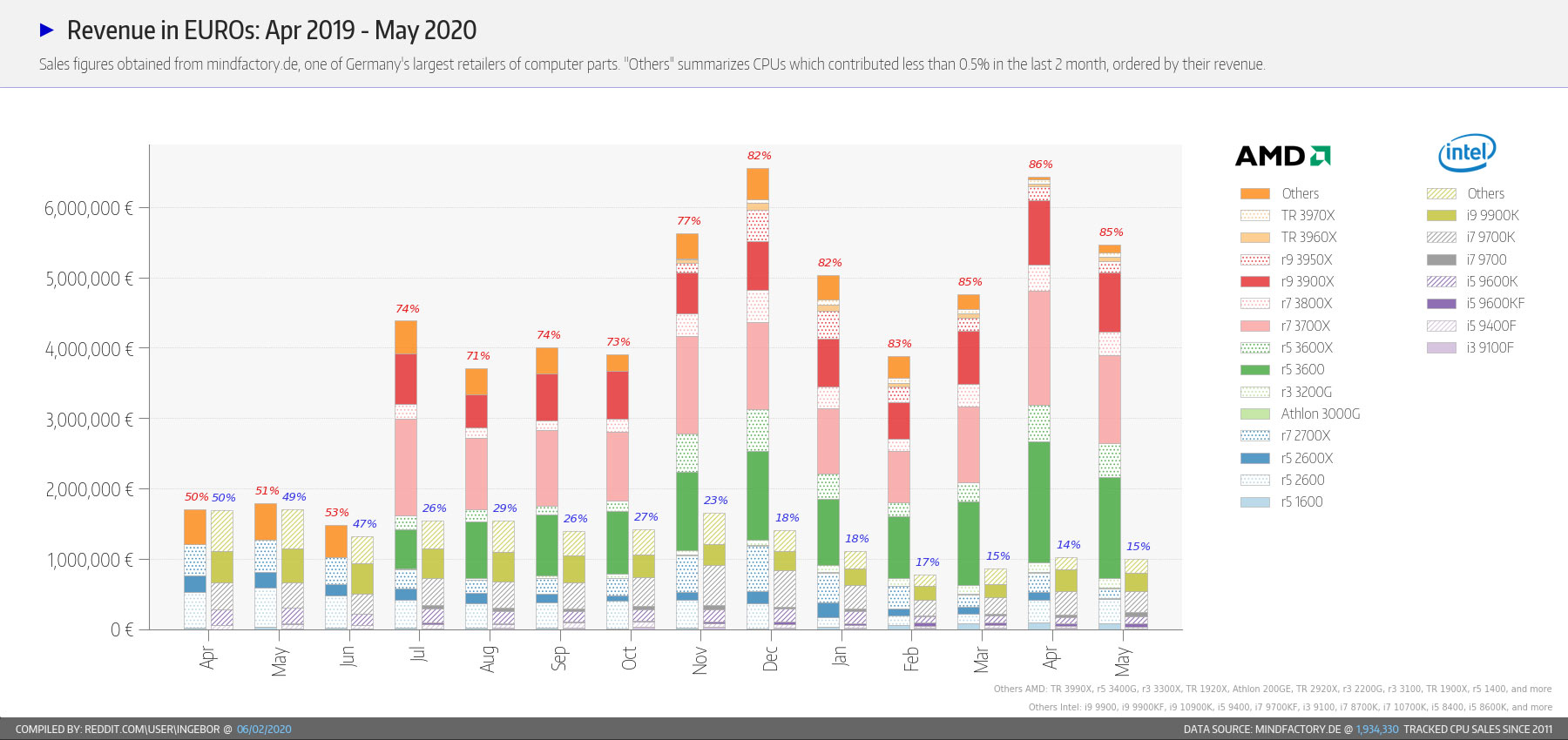

Niin no AMD rahan lainaaminen osakkeita vastaan on nykyisellä AMD kurssikehityksellä yksi paras investointi päätös mitä kukaan on pitkään aikaan tehnyt. AMD on palannut ihan huippuvuosien tuloskehitykseen. Tosin kurssi romahtaa aika nopeasti, jos AMD ei kykene pysymään nykyisessä voitollisuus ja kasvu uralla. Jos AMD nokittaa vielä jatkossakin Inteliä kaappaamalla vielä suuremman markkinaosuuden tulee jatkossakin rakettimaista kurssinousua AMD osakkeelle.

AMD taas sanoo, että samalla hinnalla saatte ylikellottaa kuinkapaljon haluatte takuu voi mennä mut me ei oteta siitä ylimääräistä satasta.

AMD taas sanoo, että samalla hinnalla saatte ylikellottaa kuinkapaljon haluatte takuu voi mennä mut me ei oteta siitä ylimääräistä satasta.