-

PikanavigaatioAjankohtaista io-tech.fi uutiset Uutisia lyhyesti Muu uutiskeskustelu io-tech.fi artikkelit io-techin Youtube-videot Palaute, tiedotukset ja arvonnat

Tietotekniikka Prosessorit, ylikellotus, emolevyt ja muistit Näytönohjaimet Tallennus Kotelot ja virtalähteet Jäähdytys Konepaketit Kannettavat tietokoneet Buildit, setupit, kotelomodifikaatiot & DIY Oheislaitteet ja muut PC-komponentit

Tekniikkakeskustelut Ongelmat Yleinen rautakeskustelu Älypuhelimet, tabletit, älykellot ja muu mobiili Viihde-elektroniikka, audio ja kamerat Elektroniikka, rakentelu ja muut DIY-projektit Internet, tietoliikenne ja tietoturva Käyttäjien omat tuotetestit

Softakeskustelut Pelit, PC-pelaaminen ja pelikonsolit Ohjelmointi, pelikehitys ja muu sovelluskehitys Yleinen ohjelmistokeskustelu Testiohjelmat ja -tulokset

Muut keskustelut Autot ja liikenne Urheilu TV- & nettisarjat, elokuvat ja musiikki Ruoka & juoma Koti ja asuminen Yleistä keskustelua Politiikka ja yhteiskunta Hyvät tarjoukset Tekniikkatarjoukset Pelitarjoukset Ruoka- ja taloustarviketarjoukset Muut tarjoukset

Kauppa-alue

Navigation

Install the app

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Huomio: This feature may not be available in some browsers.

Lisää vaihtoehtoja

Tyylin valinta

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

NVIDIA-spekulaatioketju (Blackwell ja tulevat sukupolvet)

- Liittynyt

- 20.10.2016

- Viestejä

- 4 430

Onko tuolla muistien nopeudella edes kuinka suurta merkitystä pelikäytössä?

Se riippuu ytimien määrästä ja kellotaajuudesta meneekö pullonkaula muisteihin, vai gpu coreen. Nopeammat muistit vain mahdollistaa kapeamman väylän samalla kaistalla. Leveämpi väylä nostaa valmistuskuluja kun tarvitaan enemmän muistipiirejä ja singalointikin pitää hoitaa niille.

Jos on aito kuva niin tuossa on lähdetty hakemaan hiljaista ja tehokasta jäähdytystä jolla saadaan 1440p ja 4k raytracemaan vähintään 60fps nopeudella. Tuohon vielä dlss 3.0 niin kyllä kelpaa.Eli siis tämänhetkisten huhujen mukaan tuossa 3080 kortissa olisi sama määrä Cuda coreja kuin 2080 ti:ssä ja 10-20% IPC parannus. Jos kellot on samalla myös hieman korkeammat niin ei ole mitenkään mahdotonta että olisi sen 20-30% nopeampi.

Ja toinen huhu kertoo että Ray tracing suorituskyky olisi jopa 4x parempi jokaisessa luokassa. (eli siis esim. 2080 vs 3080). Silloin sekin voisi olla sen 2-3x parempi kuin 2080 ti...

Siis jos huhut pitävät lähellekkään paikaansa niin hyvä kortti sieltä on tulossa.

- Liittynyt

- 21.08.2018

- Viestejä

- 5 521

Vai että ainoa syy..tuskimpa.Muista miksi valmistajat tekevät "marginaalituotteita". Koska kilpailutilanne. Voin uskoa NVIDIAn pistävän lisää watteja pesään jos se on tarpeen että Big Navi voitetaan. Samasta syystä AMD aikoinaan puski noita 2 GPU "halokortteja" kun ei muuten pärjännyt, tai yleensäkin noita refekortti-vesijäähyllä -virityksiä. Tässä 3080 sentään ei ole AIO vesijäähyä vakiona, mutta tuommoinen extreme propelliratkaisu tuskin olisi tehty jos siihen ei ole mitään syytä ja vanhan liiton 2080-cooleri riittäisi. Ainoa syy viritellä jäähdytystä paremmaksi on että vanhan vääntö ei riitä.

Miten sä sitten selität ne tulevat Blowerjäähyt tms.vähän pulimmat mallit kun niissä sitten taas yhtäkkiä riittääkin?

Kyse ei ole siis riittämisestä vaan optimaalisesta jäähystä joka olisi myös mahdollisimman hiljainen.

Blower jäähyllisten refu ohjainten aika Nvidialla ohitse ja se on hyvä se. (Vaikka sellainen riittäisikin on hyvä ettei sellaisia enään käytetä)

Pistikö Nvidia lisää watteja pesään ja julkaisi 2080Ti että voitetaan Amd?

- Liittynyt

- 21.02.2017

- Viestejä

- 6 172

Korkea tehonkulutus kuulostaa siinä mielessä ihan mahdolliselta että A100:kin hörppää 400W ja silti kellot on melko alhaiset verrattuna edeltäjiin.

Korkea tehonkulutus tarkoittaisi myös kalliita ja mahdollisesti silti äänekkäitä jäähdytysratkaisuja.

Korkea tehonkulutus tarkoittaisi myös kalliita ja mahdollisesti silti äänekkäitä jäähdytysratkaisuja.

Tuo moorelawis dead oli kuukausi sitten huhuvideo jossa 3080 on 18gbs gddr6 muisti 320bit väylällä--tarvitsee kunnon tuuletusta.Yksi huhuartikkeli, tuo kopemite ja moores law is deadin uusin video, joka oli tuon tweaktownin linkatun artikkelin lähteenä.

Cudacoreja tässä huhussa oli 3840, mutta uusin tilanne on 4352 cores 320bit väylä 18gbs gddr6 rt 2.5-4 x performance vs 2000 sarja. Eli ga103 --ga102

Viimeksi muokattu:

- Liittynyt

- 20.10.2016

- Viestejä

- 4 430

Korkea tehonkulutus kuulostaa siinä mielessä ihan mahdolliselta että A100:kin hörppää 400W ja silti kellot on melko alhaiset verrattuna edeltäjiin.

Korkea tehonkulutus tarkoittaisi myös kalliita ja mahdollisesti silti äänekkäitä jäähdytysratkaisuja.

Alkuperäinen lähde päivitti tuon kulutuksen 300-375W tasolle. Jos tuossa on jotain perää, niin voihan se tehopiikki tulla rajusta RT ytimien suhteelisen määrän kasvattamisestakin.

- Liittynyt

- 21.08.2018

- Viestejä

- 5 521

On hieman eri luokassa painiva tämä A100Korkea tehonkulutus kuulostaa siinä mielessä ihan mahdolliselta että A100:kin hörppää 400W ja silti kellot on melko alhaiset verrattuna edeltäjiin.

Korkea tehonkulutus tarkoittaisi myös kalliita ja mahdollisesti silti äänekkäitä jäähdytysratkaisuja.

Huippu Ampere voi toki yltää 385w arvoihin ja varmasti siis kunnon kelloilla yltääkin mutta on siinä sitten suorituskykyäkin luvassa.

2080Ti salama menee kellotettuna myös 385w arvoihin, mutta menee yli sweet spottien noi kellot ja kulutus lähtee vähä lapasesta

- Liittynyt

- 21.02.2017

- Viestejä

- 6 172

Kyllä se samassa luokassa esim. V100:n kanssa painii, johon edeltäjillä viittasin.On hieman eri luokassa painiva tämä A100

V100 300W, boost clock 1530 MHz

A100 400W, boost clock 1410 MHz

Tähän vielä jäisipä alle 240w niin kiitän ja kumarran.On hieman eri luokassa painiva tämä A100

Huippu Ampere voi toki yltää 385w arvoihin ja varmasti siis kunnon kelloilla yltääkin mutta on siinä sitten suorituskykyäkin luvassa.

2080Ti salama menee kellotettuna myös 385w arvoihin, mutta menee yli sweet spottien noi kellot ja kulutus lähtee vähä lapasesta

- Liittynyt

- 21.08.2018

- Viestejä

- 5 521

Sinä viittasit Ampereen ja tuohon 385w kulutukseen tällä.Kyllä se samassa luokassa esim. V100:n kanssa painii, johon edeltäjillä viittasin.

V100 300W, boost clock 1530 MHz

A100 400W, boost clock 1410 MHz

"Korkea tehonkulutus kuulostaa siinä mielessä ihan mahdolliselta"

eli tarkoitit tulevaa "385w Amperea"

Toit esille A100 400w TDP

ja minä sanoin että A100 painii ihan eriluokassa(siinä on 6192 ydintä ja kaistaa 1.6TB/s jne...)

Ja nyt sotket soppaan Voltan V100? vaikka ensin viittasit selvästi 385w tulevaan Ampereen???

- Liittynyt

- 19.10.2016

- Viestejä

- 351

Ja minua hulluksi sanottiin kun ostin 850w powerin vuonna -paavo. silloin oli fx-8320 ja rx390x haukkaamassa virtaa. Oli kuulemma overkill koska tuleva vihreä maailma ei voi mitenkään viedä yli 500w koko koneelta

T: Kellot tappiin vaikka vanhasta Seikosta

T: Kellot tappiin vaikka vanhasta Seikosta

minusta tuntuu että 7nm tsmc nvidialla on saatu aika hyväksi tehon kulutuksen suhteen jos pumppaavat korttiin lisääpotkua varmistaakseen kilpailukyvyn.Ja minua hulluksi sanottiin kun ostin 850w powerin vuonna -paavo. silloin oli fx-8320 ja rx390x haukkaamassa virtaa. Oli kuulemma overkill koska tuleva vihreä maailma ei voi mitenkään viedä yli 500w koko koneelta

T: Kellot tappiin vaikka vanhasta Seikosta

- Liittynyt

- 21.02.2017

- Viestejä

- 6 172

Yritin alunperin sanoa, että Ampere Geforcejen korkea tehonkulutus kuulostaisi hyvinkin mahdolliselta, kun ottaa huomioon kuinka tehosyöppö tuo A100 on edeltäjiinsä (V100 lukeutuu näihin!) verrattuna.Ja nyt sotket soppaan Voltan V100? vaikka ensin viittasit selvästi 385w tulevaan Ampereen???

Se V100 oli alunperinkin jo sopassa, ehkäpä olisi pitänyt mainita nimeltä niin olisi ollut helpompi ymmärtää.

- Liittynyt

- 20.10.2016

- Viestejä

- 5 236

Jos jotakin voidaan päätellä RTX 3080:n vuotaneista kuvista - erityisesti tuuletinratkaisusta - merkitsee sitä, että jäähdytysratkaisu on mietitty kokonaan uudella tavalla.

Miksi se oltaisiin mietitty kokonaan uusiksi, jos sille ei olisi tarvetta?

Hiljaisuuden vuoksi? - Mahdollisesti

Kovan virrankulutuksen / lämpöjen vuoksi? - Mielestäni vielä todennäköisempää

Itse arvioisin, että nuo 3080 -piirit on tehty Samsungin 7nm prosesilla, jolla ei ole päästy aivan riittävän hyvään teho/suorituskykysuhteeseen. Tämän vuoksi jäähdytyratkaisu on jouduttu miettimään uusiksi ja toteuttamaan aikaisemmista poikkeavalla (ja kalliimmalla) tavalla.

Tuosta tullee varmaan hyvä ja hiljainen ilmajäähy, eikä silloin mahdolliset ylimääräiset virrankulutukset haittaisi. Voi olla suunannäyttäjänä tulevaisuuden ilmahäähyille muutenkin.

3080Ti / 3090 tulee omien arvausten perusteella TSMC:n 7nm UEV -prosessilla valmistettuna (5nm ratkaisuun en aivan jaksa uskoa).

Miksi se oltaisiin mietitty kokonaan uusiksi, jos sille ei olisi tarvetta?

Hiljaisuuden vuoksi? - Mahdollisesti

Kovan virrankulutuksen / lämpöjen vuoksi? - Mielestäni vielä todennäköisempää

Itse arvioisin, että nuo 3080 -piirit on tehty Samsungin 7nm prosesilla, jolla ei ole päästy aivan riittävän hyvään teho/suorituskykysuhteeseen. Tämän vuoksi jäähdytyratkaisu on jouduttu miettimään uusiksi ja toteuttamaan aikaisemmista poikkeavalla (ja kalliimmalla) tavalla.

Tuosta tullee varmaan hyvä ja hiljainen ilmajäähy, eikä silloin mahdolliset ylimääräiset virrankulutukset haittaisi. Voi olla suunannäyttäjänä tulevaisuuden ilmahäähyille muutenkin.

3080Ti / 3090 tulee omien arvausten perusteella TSMC:n 7nm UEV -prosessilla valmistettuna (5nm ratkaisuun en aivan jaksa uskoa).

- Liittynyt

- 17.10.2016

- Viestejä

- 2 010

Mitä näitä keskusteluja seurannut, niin nimenomaan nvidian käyttäjät on isosti juuri pienemmän tehonkulutuksen vuoksi näitä valinnut. Vähemmän lämpöä, vähemmän ääntä jne. Toki sitten erikseen ne jotka tarvitsee huippumallin, siinähän ei ole enää tehonkulutuksen kannalta mitään tekemistä kun ne on monesti kellotettukin tappiin eikä ole valinnan varaakaan kun kilpailua ei ole.Eipä sillä tehonkulutuksella ole ainakaan minulle juurikaan merkitystä, paitsi jos kilpailijalla on saman tehoinen kortti huomattavasti pienemmällä tehonkulutuksella... Silloinkin hinta on isompi tekijä...

- Liittynyt

- 21.08.2018

- Viestejä

- 5 521

Onhan se 385w kulutus mahdollista jo 2080Ti ohjaimillakin.Yritin alunperin sanoa, että Ampere Geforcejen korkea tehonkulutus kuulostaisi hyvinkin mahdolliselta, kun ottaa huomioon kuinka tehosyöppö tuo A100 on edeltäjiinsä (V100 lukeutuu näihin!) verrattuna.

Se V100 oli alunperinkin jo sopassa, ehkäpä olisi pitänyt mainita nimeltä niin olisi ollut helpompi ymmärtää.

Kysymys kuuluukin montako ydintä nopeimmassa amperessa on ja millaiset kellot. (V100 ja A100 vertailu tuskin avaa asiaa?)

3080 ei ole kuitenkaan nopein Ampere eikä siinä todellakaan tule olemaan 385w kulutusta, kyse on nyt sitten 3080Ti/3090 kulutuksista.

Ei se energiatehokkuus huonommaksi ole menossa.

- Liittynyt

- 21.08.2018

- Viestejä

- 5 521

Pienempi kulutus ja energiatehokkuus on 2 eriasiaa.Mitä näitä keskusteluja seurannut, niin nimenomaan nvidian käyttäjät on isosti juuri pienemmän tehonkulutuksen vuoksi näitä valinnut. Vähemmän lämpöä, vähemmän ääntä jne. Toki sitten erikseen ne jotka tarvitsee huippumallin, siinähän ei ole enää tehonkulutuksen kannalta mitään tekemistä kun ne on monesti kellotettukin tappiin eikä ole valinnan varaakaan kun kilpailua ei ole.

Energiatehokkuus mahdollistaa kovemmat HighEnd kortit samalla kulutuksella esim Rtx2080Ti

Jos haluaa vähän kuluttavan ohjaimen niin sitten kannattaa ostaa Gtx1650 tms.

Ei ole 2080Ti energiatehokkuus mikään huono, nopea ohjain hyvällä energiatehokkuudella.

Edelleen energiatehokkuus merkitsee, muuten sen hyvän energiatehokkuuden omaavan 250w ohjaimen suorituskykyyn tarvittaisiin jopa yli 300w

385w 7nm Ampere ohjain voi ihan hyvin mennä ohitse energiatehokkuudessa jopa Gtx1660Ti

Ja täytyykin mennä!!

- Liittynyt

- 21.02.2017

- Viestejä

- 6 172

Tämä nyt on ihan eri kysymys. Minä puhuin tehonkulutuksesta jolloin V100 ja A100 vertailu ehkä hieman valottaa mihin suuntaan ollaan menossa, tai sitten ei.Kysymys kuuluukin montako ydintä nopeimmassa amperessa on ja millaiset kellot. (V100 ja A100 vertailu tuskin avaa asiaa?)

- Liittynyt

- 14.10.2016

- Viestejä

- 25 069

5nm se ei taatusti ole, kysymys on lähinnä onko se TSMC:n N7, N7P vai N7+ EUV, vai jopa Samsung (7nm EUV tai 8nm DUV)3080Ti / 3090 tulee omien arvausten perusteella TSMC:n 7nm UEV -prosessilla valmistettuna (5nm ratkaisuun en aivan jaksa uskoa).

- Liittynyt

- 22.10.2016

- Viestejä

- 12 910

Eli siis tämänhetkisten huhujen mukaan tuossa 3080 kortissa olisi sama määrä Cuda coreja kuin 2080 ti:ssä ja 10-20% IPC parannus. Jos kellot on samalla myös hieman korkeammat niin ei ole mitenkään mahdotonta että olisi sen 20-30% nopeampi.

Onko jotain lähdettä näille huhuille? Vaikuttaa nimittäin jossain määrin epäuskottavalta tämä ensimmäinen:

GPUssa ei ole mitään järkeä uhraamaan hirveää määrää transistoreita paremman IPCn tavoitteluun, kun rinnakkaista laskettavaa on kuitenkin paljon.

Erityisesti kun vielä säteenjäljitys- ja tensoriyksiköiden määrä on sidottu niihin shader-prosessoreihin.

Tuollainen "10-20% lisää IPCtä ja vain pieni ydinmääränlisäys" olisi vaan helposti huonompi piiri kuin Turingin suora die-shring ja lisäpinta-alan käyttö suurempaan määrään ytimiä. Ja nVidia ei ole tyhmä, eikä tuppaa tehdä huonoja ratkaisuita.

Ellei sitten kyse ole siitä, että piiristä haluttiin tehdä selvästi pienempi jolloin niitä ytimiä ei kuitenkaan mahdukaan kovin paljoa, ja se IPC saatiin kuitenkin melko halvalla

Ja toinen huhu kertoo että Ray tracing suorituskyky olisi jopa 4x parempi jokaisessa luokassa. (eli siis esim. 2080 vs 3080). Silloin sekin voisi olla sen 2-3x parempi kuin 2080 ti...

Siis jos huhut pitävät lähellekkään paikaansa niin hyvä kortti sieltä on tulossa.

Se on suomeksi "säteenjäljitys".

Mutta tämä on ihan mahdollista, käytännössä siten että säteenjäljitysyksiköiden määrä/ydin, tai yksittäisen säteenjäljitysyksikön throughput-nopeus tuplataan, ja sitten suurempi määrä ytimiä + kellojen lisäys antaa toisen tuplauksen.

Ensimmäiseen kysymykseen vastaus on --katso vaikka not apple fan youtube video eiliseltä ampere video jossa näkyy kopite@kimi postaus kesäkuun alusta--siinä viitataan 3080 specsit.Onko jotain lähdettä näille huhuille? Vaikuttaa nimittäin jossain määrin epäuskottavalta tämä ensimmäinen:

GPUssa ei ole mitään järkeä uhraamaan hirveää määrää transistoreita paremman IPCn tavoitteluun, kun rinnakkaista laskettavaa on kuitenkin paljon.

Erityisesti kun vielä säteenjäljitys- ja tensoriyksiköiden määrä on sidottu niihin shader-prosessoreihin.

Tuollainen "10-20% lisää IPCtä ja vain pieni ydinmääränlisäys" olisi vaan helposti huonompi piiri kuin Turingin suora die-shring ja lisäpinta-alan käyttö suurempaan määrään ytimiä. Ja nVidia ei ole tyhmä, eikä tuppaa tehdä huonoja ratkaisuita.

Ellei sitten kyse ole siitä, että piiristä haluttiin tehdä selvästi pienempi jolloin niitä ytimiä ei kuitenkaan mahdukaan kovin paljoa, ja se IPC saatiin kuitenkin melko halvalla

Se on suomeksi "säteenjäljitys".

Mutta tämä on ihan mahdollista, käytännössä siten että säteenjäljitysyksiköiden määrä/ydin, tai yksittäisen säteenjäljitysyksikön throughput-nopeus tuplataan, ja sitten suurempi määrä ytimiä + kellojen lisäys antaa toisen tuplauksen.

- Liittynyt

- 21.06.2017

- Viestejä

- 7 588

8192 ytimellä TDP 400w

vai oliko se 6912 ydintä ja 400w siis.

6912 cudaa ja varsin maltillisilla kelloilla (piiriltä kyllä löytyy 8192 cudaa mutta niitä on poistettu käytöstä ja osa ihan vaan rikki. Saantojen parantamiseksi näin tehty).

Kellot, cuda määrä ja toi kulutus on se mikä itteäni hiukan kummastuttaa, toki tuossa A100:ssa on paljon sellaista roskaa syömässä virtaa jota ei kuluttaja kortteihin tule, mutta kuluttaja kortteihin taas tulee jotain mitä A100:ssa ei ole. Eli jotenkin toi kulutus kyllä tuntuu aika kovalta.

ja minä sanoin että A100 painii ihan eriluokassa(siinä on 6192 ydintä ja kaistaa 1.6TB/s jne...)

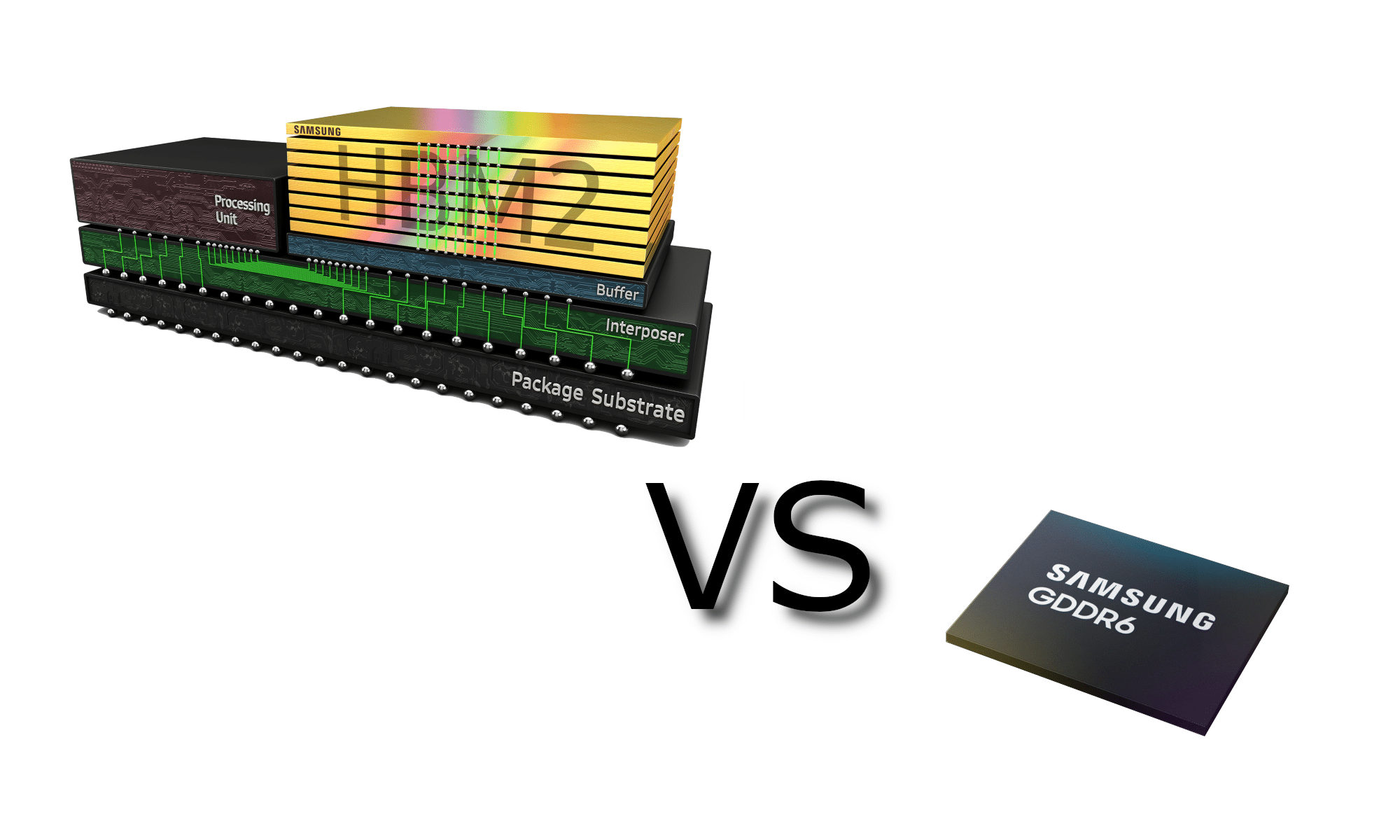

Ja se kaista saavutetaan HBM2 muisteilla jotka kuluttaa selvästi vähemmän virtaa kuin GDDR6. TOi A100 DDR6 muisteilla ja tuolla kaistalla hörppäisi selvästi enemmän hattiwatteja mitä se nyt tekee.

- Liittynyt

- 22.10.2016

- Viestejä

- 12 910

Ensimmäiseen kysymykseen vastaus on --katso vaikka not apple fan youtube video eiliseltä ampere video jossa näkyy kopite@kimi postaus kesäkuun alusta--siinä viitataan 3080 specsit.

Jos "lähde" on satunnainen youtube-video johon ei edes anneta linkkiä, jossa vaan väitetään sellaisen toisen tyypin twiitanneen jotain, joka postailee juttuja täysin olemattomasta muistityypistä niin tarkoittaa että ne on aivan yhtä tyhjän kanssa.

Kopite7kimi tuntuu keksivän juttujaan ihan omasta päästään eikä erottele, mikä on 1) omaa spekulaatiota 2) muualla spekulaationa väitettyä 3) muualla vuotona väitettyä. Ja postaa eteenpäin kaiken piittaamatta yhtään siitä, onko siinä mitään järkeä.

Toki sen jutuissa on selvästi paikkaansapitäviäkin, mutta kun niiden seassa on niin paljon sontaa että mihinkään mitä se postaa ei todellakaan voi luottaa.

Toinen sonta tuon GDDX6Xn lisäksi on esim. tämä:

Tosiasiassa tapeoutista piirin markkinoilletuloon menee n. vuosi. Jos tuo piiri olisi juuri tapeoutattu tuolloin toukokuussa, se tarkoittaisi markkinoilletuloa aikaisinaan kevälllä 2021.

Taitaa kuitenkin pikkusen aikaisemmin olla nämä tulossa...

Viimeksi muokattu:

- Liittynyt

- 14.10.2016

- Viestejä

- 25 069

Saman kaverin speksit joka puhuu ties mistä olemattomista GDDR6X-muisteistaEnsimmäiseen kysymykseen vastaus on --katso vaikka not apple fan youtube video eiliseltä ampere video jossa näkyy kopite@kimi postaus kesäkuun alusta--siinä viitataan 3080 specsit.

- Liittynyt

- 21.08.2018

- Viestejä

- 5 521

Tarkoitin tuossa että painii ihan eri sarjassa ja asioissa suorituskyvyn suhteen kuin peli ampere,virrankulutuksesta en sitten tiedä kun hieman eroaa kuitenkin "peli" Amperesta6912 cudaa ja varsin maltillisilla kelloilla (piiriltä kyllä löytyy 8192 cudaa mutta niitä on poistettu käytöstä ja osa ihan vaan rikki. Saantojen parantamiseksi näin tehty).

Kellot, cuda määrä ja toi kulutus on se mikä itteäni hiukan kummastuttaa, toki tuossa A100:ssa on paljon sellaista roskaa syömässä virtaa jota ei kuluttaja kortteihin tule, mutta kuluttaja kortteihin taas tulee jotain mitä A100:ssa ei ole. Eli jotenkin toi kulutus kyllä tuntuu aika kovalta.

Ja se kaista saavutetaan HBM2 muisteilla jotka kuluttaa selvästi vähemmän virtaa kuin GDDR6. TOi A100 DDR6 muisteilla ja tuolla kaistalla hörppäisi selvästi enemmän hattiwatteja mitä se nyt tekee.

Peli amperessa vähemmän ytimiä ja muuta "turhaa" mutta kovemmat kellot.

Luonnollisesti sieltä varmaan tulee ohjaimia tuttuun 200-300w TDP haarukkaan. 385w TDP sitten täytyisi olla jo mukavasti ytimiä kohtuu kelloilla.

Olisi mielenkiintoista tietää paljonko

40GB HBM2 2.4Gbps, 5120bit 1.6TB/s kuluttaa.

Vaikea uskoa että kulutus olisi ainakaan perus GDDR6 muisteja matalempi tuossa kokoluokassa.

- Liittynyt

- 21.06.2017

- Viestejä

- 7 588

Triviaalisti nähdään että muistin määrä ja muistiväylän leveys ei matchää. Silti pitänyt retweetata.

Öh, miten niin ei mätsää? 32-bit per kika niin hyvinhän toi näyttäisi osuvan kohdilleen.

- Liittynyt

- 21.08.2018

- Viestejä

- 5 521

Oliskohan kaveri selannu Cdon.com sivustoa ja tehnyt vähän johtopäätöksiäSaman kaverin speksit joka puhuu ties mistä olemattomista GDDR6X-muisteista

Moni paikka näemmä ilmoittaa että muistit olisi GDDR6X

- Liittynyt

- 22.10.2016

- Viestejä

- 12 910

Öh, miten niin ei mätsää? 32-bit per kika niin hyvinhän toi näyttäisi osuvan kohdilleen.

Joo, tuossa tuli moka minulta, en huomannut että siinä puhuttiin kahdesta eri piiristä. Poistin tuon heti n. minuutissa kun huomasin mokani (eli n. puoli tuntia sitten)

- Liittynyt

- 20.10.2016

- Viestejä

- 4 430

Oliskohan kaveri selannu Cdon.com sivustoa ja tehnyt vähän johtopäätöksiä

Moni paikka näemmä ilmoittaa että muistit olisi GDDR6X

On noita muutaman muunkin 2080 kortin tiedoissa, joku on typottanut tukkurilla.

Ja tietty colorfullin pressitiedotteessa:

"

The RTX 2080 Advance OC features the Turing architecture and TU102 GPU with 8GB of GDDR6X memory running at 448 GB/S bandwidth. The RTX 2080 Ti has the same memory bandwidth with 11GB of GDDR6X RAM."

Mutta tuo gddr6x huhun todenperäisyys on on kyllä aika heikko. Jos tuo olisi käynnykän autocorrectin tekosia, niin luulisi korjauksen jo tulleen.

bahis

Tukijäsen

- Liittynyt

- 06.03.2019

- Viestejä

- 4 129

Onko jotain lähdettä näille huhuille? Vaikuttaa nimittäin jossain määrin epäuskottavalta tämä ensimmäinen:

GPUssa ei ole mitään järkeä uhraamaan hirveää määrää transistoreita paremman IPCn tavoitteluun, kun rinnakkaista laskettavaa on kuitenkin paljon.

Erityisesti kun vielä säteenjäljitys- ja tensoriyksiköiden määrä on sidottu niihin shader-prosessoreihin.

Tuollainen "10-20% lisää IPCtä ja vain pieni ydinmääränlisäys" olisi vaan helposti huonompi piiri kuin Turingin suora die-shring ja lisäpinta-alan käyttö suurempaan määrään ytimiä. Ja nVidia ei ole tyhmä, eikä tuppaa tehdä huonoja ratkaisuita.

Ellei sitten kyse ole siitä, että piiristä haluttiin tehdä selvästi pienempi jolloin niitä ytimiä ei kuitenkaan mahdukaan kovin paljoa, ja se IPC saatiin kuitenkin melko halvalla

Huomasit varmaan että 3080 kortissa olisi sama määrä Cuda ytimiä kuin 2080 TI kortissa (4352). Eli 1408 kappaletta enemmän mitä 2080 kortissa (2944), joka on saman luokan Turing kortti. TI kortissa varmasti sitten on reilusti enemmän...

Lähteenä taisi olla alunperin tuo Moore's Law Is Dead jonka monikin sivusto sitten julkaisi...

Se on suomeksi "säteenjäljitys".

Olen syvästi pahoillani. Suomeksi kirjoittaminen ei ole oikein minulle luontevaa, yritän jatkossa parantaa ulosantiani.

- Liittynyt

- 14.10.2016

- Viestejä

- 25 069

...ja jonka "ennustuksista" meni puolet juuri mönkään kun NVIDIA julkaisi Amperen eikä täsmännytkään sen "tietojen" kanssa?Huomasit varmaan että 3080 kortissa olisi sama määrä Cuda ytimiä kuin 2080 TI kortissa (4352). Eli 1408 kappaletta enemmän mitä 2080 kortissa (2944), joka on saman luokan Turing kortti. TI kortissa varmasti sitten on reilusti enemmän...

Lähteenä taisi olla alunperin tuo Moore's Law Is Dead jonka monikin sivusto sitten julkaisi...

- Liittynyt

- 21.06.2017

- Viestejä

- 7 588

Peli amperessa vähemmän ytimiä ja muuta "turhaa" mutta kovemmat kellot.

Luonnollisesti sieltä varmaan tulee ohjaimia tuttuun 200-300w TDP haarukkaan. 385w TDP sitten täytyisi olla jo mukavasti ytimiä kohtuu kelloilla.

Niin toki tulee mutta itteäni vain kummastuttaa tuon A100 hyvin maltilliset kellot. Volta on varmaan lähin mihin voi verrata niin tuntuisi että ei ole oikein mitään hyötyä saatu 7nm nodesta energian kulutuksen suhteen.

Olisi mielenkiintoista tietää paljonko

40GB HBM2 2.4Gbps, 5120bit 1.6TB/s kuluttaa.

Vaikea uskoa että kulutus olisi ainakaan perus GDDR6 muisteja matalempi tuossa kokoluokassa.

GDDR6 VS HBM2 Memory - TechSiting

Both GDDR6 and HBM2 are types of memory that enable processors to perform better in a wide variety of applications due to their high memory bandwidth. In this

Tuolla puhutaan 3,5-4,5 kertaisesta erosta HBM2 hyväksi. Eli jos laitetaan riita puoliksi eli 4x niin kortille voi laittaa 32G HBM2 muistia taikka 8G GDDR6 muistia jolloin muistin kuluttama virta on about sama.

Tuo virran kulutus ja HBM2 toteutuksen pienempi pintaalan tarve itse GPU:lta on ne suurimmat syyt miksi noissa isoissa piireissä tuota suositaan. GDDR6:lla kun aletaan toteuttaa leveää muistikaistaa niin siihen kuluu piiriltä pintaalaa ja onhan se nähty että 512-bit GDDR toteutuksia ei ole montaa ollut kun ilmeisesti alkaa jo ihan piirilevyn suunnitteluunkin tuomaan haasteita.

- Liittynyt

- 14.10.2016

- Viestejä

- 25 069

Öö, täh? Ei ne matalat kellot liity mitenkään siihen paljonko 7nm nodesta saatiin hyötyä energiankulutukseen (vinkki: se auttoi paljon)Niin toki tulee mutta itteäni vain kummastuttaa tuon A100 hyvin maltilliset kellot. Volta on varmaan lähin mihin voi verrata niin tuntuisi että ei ole oikein mitään hyötyä saatu 7nm nodesta energian kulutuksen suhteen.

- Liittynyt

- 21.06.2017

- Viestejä

- 7 588

Öö, täh? Ei ne matalat kellot liity mitenkään siihen paljonko 7nm nodesta saatiin hyötyä energiankulutukseen (vinkki: se auttoi paljon)

Asia selvä. Muuten vain ihan huvikseen on TDP:tä pumpattu reippaasti ylös. Eihän se nyt eka kerta olisi että piiri ei käyttäydykkään kuten on oletettu ja kuluttaa enemmän.

- Liittynyt

- 14.10.2016

- Viestejä

- 25 069

Sitä on pumpattu ylös 50 wattia. Siinä sirussa on yli 2,5 kertaa enemmän transistoreja.Asia selvä. Muuten vain ihan huvikseen on TDP:tä pumpattu reippaasti ylös. Eihän se nyt eka kerta olisi että piiri ei käyttäydykkään kuten on oletettu ja kuluttaa enemmän.

- Liittynyt

- 21.08.2018

- Viestejä

- 5 521

Melkoisen järjetön määrä eroa transistoreissa, johtuuko sitten mistä? oma tietämys A100/V100 heikon puoleinen kun ei ole joutunut niihin sen paremmin perehtymään.Sitä on pumpattu ylös 50 wattia. Siinä sirussa on yli 2,5 kertaa enemmän transistoreja.

- Liittynyt

- 14.10.2016

- Viestejä

- 25 069

Siinä on 50% leveämpi muistiohjain, 60% enemmän CUDA-ytimiä, uusia temppuja osaavia järeämpiä tensoriyksiköitä, enemmän ja järeämpiä NVLinkkejä jne jne jneMelkoisen järjetön määrä eroa transistoreissa, johtuuko sitten mistä? oma tietämys A100/V100 heikon puoleinen kun ei ole joutunut niihin sen paremmin perehtymään.

- Liittynyt

- 21.06.2017

- Viestejä

- 7 588

Sitä on pumpattu ylös 50 wattia. Siinä sirussa on yli 2,5 kertaa enemmän transistoreja.

NVIDIA Data Centers for the Era of AI Reasoning

Accelerate and deploy full-stack infrastructure purpose-built for high-performance data centers.

www.nvidia.com

250/300W (mallista riippuen) vs. 400W

Vaikuttaisi että suurin osa niistä transuista on mennyt uusiin ominaisuuksiin joita Voltassa ei ole. Sitähän en toki tiedä että saako tuon A100 hörppäämään tuon 400W pelkästään cudaa hyrskyttämällä.

- Liittynyt

- 21.06.2017

- Viestejä

- 7 588

Siinä on 50% leveämpi muistiohjain, 60% enemmän CUDA-ytimiä, uusia temppuja osaavia järeämpiä tensoriyksiköitä, enemmän ja järeämpiä NVLinkkejä jne jne jne

Millä matematiikalla sie oikein saat 60% enemmän cuda ytimiä A100 vs V100? 6912 vs 5120 on miun laskejen mukaan 35% enemmän.

- Liittynyt

- 14.10.2016

- Viestejä

- 25 069

Syystä X NVIDIA ei ole päivittänyt sivuilleen, mutta tuosta V100:sta on myös 350W versio

NVIDIA Data Centers for the Era of AI Reasoning

Accelerate and deploy full-stack infrastructure purpose-built for high-performance data centers.www.nvidia.com

250/300W (mallista riippuen) vs. 400W

Vaikuttaisi että suurin osa niistä transuista on mennyt uusiin ominaisuuksiin joita Voltassa ei ole. Sitähän en toki tiedä että saako tuon A100 hörppäämään tuon 400W pelkästään cudaa hyrskyttämällä.

Building Bigger, Faster GPU Clusters Using NVSwitches

Nvidia launched its second-generation DGX system in March. In order to build the 2 petaflops half-precision DGX-2, Nvidia had to first design and build a

It is worth noting that Nvidia increased the power consumption rating for the new Tesla V100 32 GB SXM3 module to 350 watts from the 16 GB version’s 300 watt rating. Nvidia also upgraded the 32 GB version’s air-cooled heat sink.

Koko sirusta. Koita pistää mieluummin yhteen viestiin kaksi asiaa kuin kaksi peräkkäistä lyhyttä viestiäMillä matematiikalla sie oikein saat 60% enemmän cuda ytimiä A100 vs V100? 6912 vs 5120 on miun laskejen mukaan 35% enemmän.

- Liittynyt

- 21.06.2017

- Viestejä

- 7 588

Koko sirusta. Koita pistää mieluummin yhteen viestiin kaksi asiaa kuin kaksi peräkkäistä lyhyttä viestiä

Ja ne disabloidut coret vie kuinka paljon sähköä?

- Liittynyt

- 21.08.2018

- Viestejä

- 5 521

Ei ole niin yksinkertaista kuin esim näissä Turing pascal tms peli näytönohjain vertailuissa.Ja ne disabloidut coret vie kuinka paljon sähköä?

Painoarvo muutenkin ihan eri lukemissa/laskennassa.

Tuki on nyt FP16, BF16, TF32, FP64, INT8, INT4

A100 on featuret joita V100 ei ole.

A100 on 1.2-10x nopeampi ja sparsityllä jopa tuplaantuu jne..

Näiden A100/V100 vertaaminen ja näistä päätteleminen on turhaa.

Joku katsoo A100/v100 pelkkää cuda ytimiä ja coren kelloja ja kulutuksia jotka ei anna lopulta mitään vertailuarvoa siihen millainen se 3080 tms. tulee olemaan.

Mun puolesta V100 ja A100 voi jättää ja keskittyä vaikka ennemmin huhuihin, niistäkin saa enemmän tuntumaa,kuin A100 vertailusta v100 tai mihinkään muuhunkaan.

Mutta sivu mainintana niin hyvin mahtuu transistoria lähes samaankokoon kuin V100.

- Liittynyt

- 21.02.2017

- Viestejä

- 6 172

Igorin mukaan Nvidia on käynnistänyt tutkinnan vuodosta. Pitää myös ilmeisesti varmana, että GDDR6X käytössä:

"All three expected launch cards will definitely be equipped with GDDR6X..."

www.igorslab.de

www.igorslab.de

"All three expected launch cards will definitely be equipped with GDDR6X..."

Exclusive info about NVIDIA’s Ampere: 3 models, memory size, PCBs, an extremely expensive cooler for the FE and the search for the leak | igor´sLAB

Recently I had already posted some information about the new graphics card generation from NVIDIA and also processed it in the video, but I was still a little bit reserved concerning the currently…

- Liittynyt

- 20.10.2016

- Viestejä

- 4 430

Igorin mukaan Nvidia on käynnistänyt tutkinnan vuodosta. Pitää myös ilmeisesti varmana, että GDDR6X käytössä:

"All three expected launch cards will definitely be equipped with GDDR6X..."

Exclusive info about NVIDIA’s Ampere: 3 models, memory size, PCBs, an extremely expensive cooler for the FE and the search for the leak | igor´sLAB

Recently I had already posted some information about the new graphics card generation from NVIDIA and also processed it in the video, but I was still a little bit reserved concerning the currently…www.igorslab.de

Siinä oli myös 320-350W TDP 3080/3080TI/3090 korteille ja sama siru eri leikkausasteella. Tuo 10Gb muistimäärä on myös vähän outo tuon gddr6x:n lisäksi. Lähteet oli "omat", joten joku trollaa useampaa vuotajaa tuolla muistityypillä, tai se tulee ihan puskasta.

- Liittynyt

- 20.10.2016

- Viestejä

- 4 430

Ettei tuo 3090 olisi kuitenkin sitten uusi Titan? Muistimäärä siihen viittaisi...

Sitä videocardz ainakin veikkaisi. Siellä myös arveltiin jäähyn hinnaksi 150usd.

"Another thing that caught my attention is the fact that both Igor and Kopite refer to the next-gen TITAN as RTX 3090. This is obviously not confirmed and personally I doubt NVIDIA would drop this brand all of sudden, but it appears that the RTX 3090 could take the place in the RTX lineup. The current-gen TITAN already carries RTX branding, and to be honest, I’m not sure how NVIDIA was planning to introduce a successor: TITAN RTX II? On the other hand, we have not seen an x90 SKU in years and they have always been dual-GPU models. It is simply too soon to tell."

- Liittynyt

- 15.04.2018

- Viestejä

- 2 342

Saiskohan ilman jäähyä?Sitä videocardz ainakin veikkaisi. Siellä myös arveltiin jäähyn hinnaksi 150usd.

Toisaalta jos on noin kallis, niin vesijäähdytetyt mallit eivät pitäisi olla paljoa kalliimpia. Ikävä kyllä näin se ei taida toimia, vaan valmistaja vetää rahat taskuun :/

- Liittynyt

- 14.10.2016

- Viestejä

- 25 069

Vaikka Igorilla on hyvä maine, niin vähän kyllä haisee siltä että nyt haukkaa kakkaa. Mahdollisuudet sille, että taustalla olisi kehitetty uusi muistityyppi ennen kuin GDDR6-muistit ovat saavuttaneet edes lopullisia nopeuksiaan, ja ilman että asiasta on valunut mitään tietoa muualle vain pari kuukautta ennen julkaisua, on erittäin pienet.Igorin mukaan Nvidia on käynnistänyt tutkinnan vuodosta. Pitää myös ilmeisesti varmana, että GDDR6X käytössä:

"All three expected launch cards will definitely be equipped with GDDR6X..."

Exclusive info about NVIDIA’s Ampere: 3 models, memory size, PCBs, an extremely expensive cooler for the FE and the search for the leak | igor´sLAB

Recently I had already posted some information about the new graphics card generation from NVIDIA and also processed it in the video, but I was still a little bit reserved concerning the currently…www.igorslab.de

Uutiset

-

Renderöintivuodoissa Samsungin tulevat Galaxy Glasses -älylasit

30.4.2026 22:16

-

Motorola julkaisi lisää moto g -puhelimia – moto g87:ssä 200 megapikselin pääkamera

30.4.2026 19:07

-

Windows Central sai tietoja Microsoftin Windows K2 -projektista

30.4.2026 11:13

-

Motorola julkaisi uuden edge 70 pron neljänä PANTONE-versiona eri materiaalein

30.4.2026 01:34

-

Motorola julkaisi razr 70 -malliston – ultra-mallissa LOFIC-pääkamera

30.4.2026 00:42