Eli maskin tekeminen valmistaa 7nm yksipiiristä desktop-prossua maksaa ~300M.

Ei maksa.

Yritin joskus etsiä lähdettä tuolle luvulle, eikä löytynyt. Löytyi vain joku n. 271 miljoonan suuruusluokkaa oleva luku, jossa se luku käsitti paljon muutakuin kuin pelkän maskin.

10nm Versus 7nm

Sen sijaan täältä löytyi käppyrä, jossa mainitaan maskin hinta:

http://www.swtest.org/swtw_library/2015proc/PDF/SWTW2015_Keynote_McCann_GlobalFoundries.pdf

Tuolla sivu 5

Piiristä, jonka kehityskustannukset on n. 600 miljoonaa, maskin osuus on luokkaa 10 mljoonaa 7nm:llä

Tuo kustannus pitää saada desktop-prossujen myynnistä takaisin jotta hommassa olisi mitään järkeä. Muutaman miljoonan prossun myynnille AMD:llä ei ole ylipäätään varaa muuhun kuin soveltaa valmista chiplet-versiota

.. paitsi että jos ei tulisi yksipiilastuista ryzeniä, tarvittaisiin toinen, pienempi IO-piiri. EPYCin IO-piiri on aivan liian iso kallis käytettäväksi ryzenissä.

Eli sitten tarvittaisiin kuitenkin uusi IO-piiri. Ei yhtään sen vähempää piirejä. Toki se "lisäpiiri" olisi vanhemmalla valmistustekniikalla.

Ja koko chiplet-idean juurisyy on että ei tarvitse suunnitella kuin yksi 7nm piiri, halvempia 14nm IO-piirejä voi suunnitella sitten useampiakin, ellei jopa Epyciin suunniteltu IO-piiri ole suunniteltu niin että se voidaan jakaa useammaksi kappaleeksi käytettävissä desktop-ryzeneissä jolloin lisämaskikustannuksia desktop-Ryzenin valmistukseen ei tulisi ollenkaan.

En oikein näe mitään "jakamista" mitenkään käytännössä mahdollisena.

Niiden järeiden väylien pitää mennä piirin kaikkiin osiin, eikä niitä johtoja voi vaan katkaista. Ja jos piirin yrittäisi jotenkin tehdä "monesta palasta" siten että väliin laitetaan johdot jotka VOI katkaista, nämä kohdat olisivat todella pahoja kommunikaatiopullonkauloja.

Jo 14nm maskit on niin kalliita että AMD ei ole tehnyt esimerkiksi suunniteltua 2C 3CU-versiota Ryzenistä vaikka se halventaisi halpaprossujen tuotantokustannuksia alle puoleen nykyisestä - myynnin pitäisi olla todella suurta jota halpojen piirien suunnittelu kannattaisi. Paljon kustannustehokkaampaa leikata suuria piirejä pienemmiksi, Intelillä asia on eri kun myyntimäärät ovat paljon suurempia.

Zenissä yhdessä CCXssä on 4 ydintä. 2-ytiminen piiri ei olisi vain uusi piiri, vaan se vaatisi uuden CCX-designin.

ja siitä säästöstä:

Se yksi CCX on pinta-alaltaan n. 40mm^2 (8 megan kakulla muistaakseni n. 44mm^2). Ytimien pudottaminen kahteen säästäisi vain n. 20mm^2, 10%.

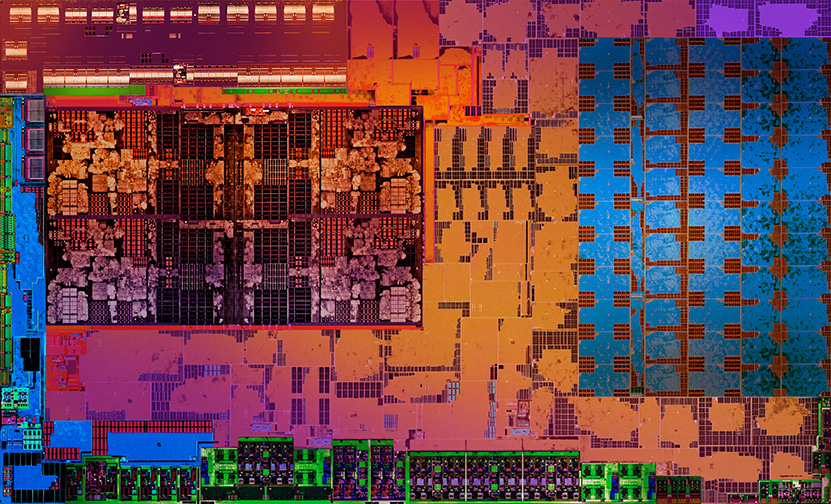

Oikealla näkyy sitten Vegan NCUt. Niitä on 11 kpl. Niiden pudottaminen kolmeen säästäisi ehkä n. 25 mm^2.

Jos ROPit puolittaisi, saisi ehkä luokkaa maksimissaan 5 mm^2 lisää.(niitä ei tästä kuvasta erota)

Eli, säästettäisiin vain n. 50mm^2 eli piirin koko putoisi n. 75%iin nykyisestä. Ei todellakaan putoisi valmistuskustannukset alle puoleen.

Toisen muistikanavan pudottamalla pois tosin voisi saada vielä ehkä n. 8mm^2 lisää pois. Pääsisi n. 70%iin nykyisestä. Edelleenkään ei lähelläkään "alle puolta".

Kyse ei ole mistään maskin hinnasta, vaan siitä, että AMDllä on rajallinen määrää insinöörejä tekemässä tuota layout-hommaa ja heidän työnsä pitää prioritisoida. Tärkeimmät ensin. Ja halpistuotteina voidaan aina myydä isoja piirejä, joista on joitain (pikkutuotteissa tarpeettomia) kohtia rikki.