- Liittynyt

- 14.10.2016

- Viestejä

- 22 495

Kaotik kirjoitti uutisen/artikkelin:

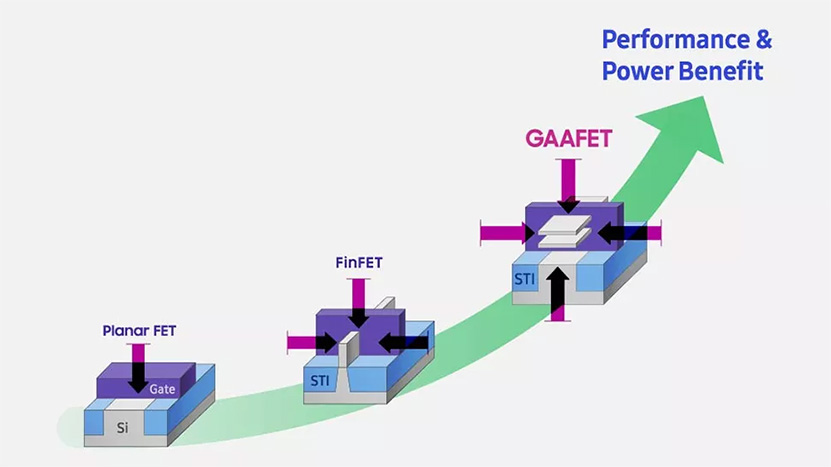

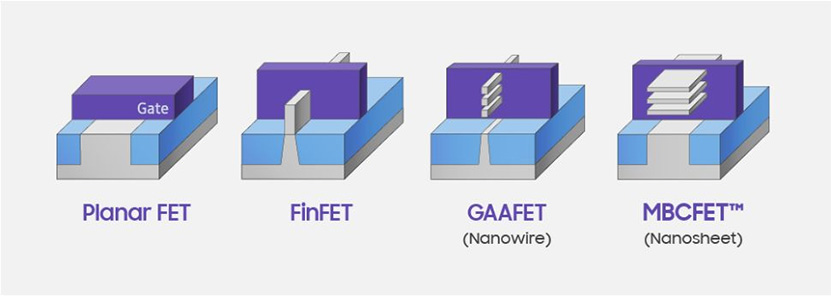

Huippusuorituskyvyn piireissä siirryttiin perinteisistä 2D-transistoreista kolmiulotteisiin FinFET-transistoreihin vuonna 2012, kun Intel aloitti Ivy Bridge -prosessoreiden myynnin. Pian on edessä seuraava askel, kun valmistajat aloittavat siirtymisen kohti GAAFET-transistoreja (Gate All Around Field Effect Transistor), joissa hila ympäröi kanavat täysin.

Samsung on esitellyt IEEE International Solid-State Circuits Conference -tapahtumassa eli ISSCC:ssä ensimmäisiä yksityiskohtia yhtiön tulevasta 3 nanometrin prosessista, joka hyödyntää GAAFET-transistoreja. Tarkemmin käytössä tulee olemaan kahdenlaisia transistoreja. Samsung kutsuu sen omia nanolevyihin perustuvia transistoreja tuotemerkin suojaamalla MBCFET-nimellä (Multi-Bridge Channel FET) ja nanolankoihin perustuvia tavallisksi GAAFETeiksi.

GAAFET-transistoreissa nimestä riippumatta voidaan hallita transistorien suorituskykyä ja samalla tehonkulutusta kanavien leveyttä muuttamalla. Leveämmät kanavat ovat nopeampia mutta samalla ne kuluttavat enemmän tehoa. Tällä on vaikutusta myös piirien transistoritiheyteen, kun saman piirin sisällä voidaan eri osissa hyödyntää aina sopivan levyisin kanavin varustettuja transistoreja.

Samsungin 3GAE-prosessin, joka hyödyntää ensimmäisen sukupolven MBCFET-teknologiaa, on tarkoitus päästä tuotantoon vuonna 2022. Yhtiö on kuitenkin ehtinyt jo toteuttamaan ensimmäisen MBCFET SRAM -sirun ja ISSCC:ssä kerrottujen tietojen mukaan 256 megabitin SRAM olisi pinta-alaltaan 56mm2. Samsungin omien vertailujen mukaan 3GAE tarjoaa 30 % parempaa suorituskykyä samalla tehonkulutuksella, 50 % pienempää tehonkulutusta samalla suorituskyvyllä ja jopa 80 % korkeampaa transistoritiheyttä, kuin yhtiön 7 nanometrin 7LPP-prosessi. Transistoritiheyden kasvu on luonnollisesti riippuvaista entistä useammasta seikasta GAAFET-transistoreiden kohdalla, eikä Samsungin luvusta tiedetä muuta, kuin että se perustuu sekoitukseen logiikka- ja SRAM-transistoreja.

Lähde: Tom's Hardware

Linkki alkuperäiseen juttuun