- Liittynyt

- 14.10.2016

- Viestejä

- 22 630

NVIDIA ilmoitti aiemmin tänä vuonna tulevansa käyttämään Samsungin 7 nanometrin valmistusprosessia tulevissa piireissään. Moni media veti tästä hätäisiä johtopäätöksiä, joiden mukaan tämä tarkoittaisi samalla TSMC:n hylkäämistä. NVIDIA tarkensi myöhemmin, että myös TSMC tulee pysymään yhtiölle tärkeänä kumppanina.

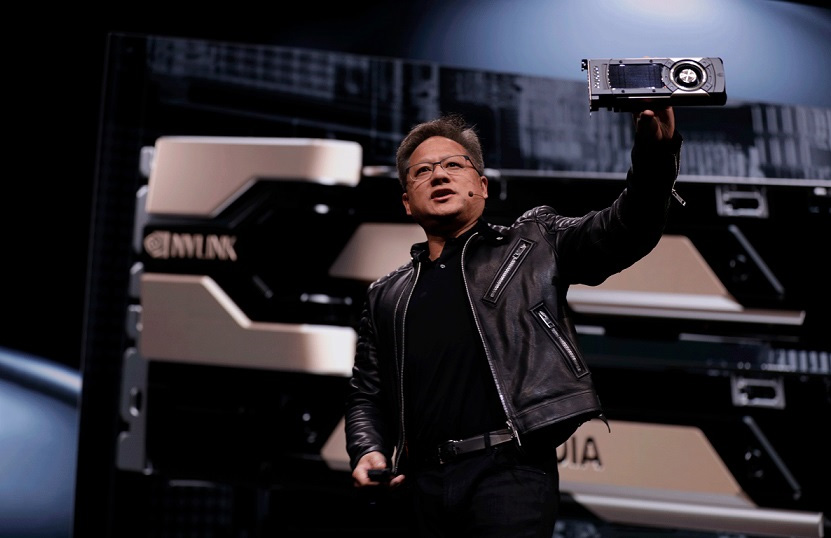

Nyt NVIDIAn toimitusjohtaja Jensen Huang on tarkentanut yhtiön suunnitelmia puolijohdevalmistajien käytöstä piirien valmistuksessa. Kiinassa pidetyssä GTC-konferenssissa Huangin kerrotaan varmistaneen, että TSMC tulee jatkossakin valmistamaan valtaosan yhtiön piireistä, myös 7 nanometrin prosessilla ja että Samsungille on myönnetty vain pieni määrä tilauksia täytettäväksi. Tilanne saattaa olla vastaava, kuin esimerkiksi Pascal-sukupolven kohdalla. Pascal-sukupolvessa NVIDIA tuotatti suurimman osan piireistään TSMC:n 16 nanometrin prosessilla, mutta kaikkein pienimmät GP107- ja GP108-piirit valmistettiin Samsungin 14 nanometrin prosessilla.

Tällä hetkellä kenties mielenkiintoisin kysymys NVIDIAn tulevien piirien valmistusprosessin osalta koskee TSMC:n linjoilla valmistettavia piirejä: Käyttääkö yhtiö N7-prosessia DUV-litografialla (Deep UltraViolet) vai hyppääkö se suoraan N7+-prosessiin EUV-litografialla (Extreme UltraViolet). Samsungilla tuotettavat piirit tulevat käyttämään varmuudella EUV-prosessia, sillä yhtiöllä ei ole lainkaan 7 nanometrin DUV-prosessia. Tämä ei kuitenkaan kerro mitään TSMC:llä tuotettavista piireistä, sillä prosessien suunnittelusäännöt eivät ole yhteensopivia keskenään eri puolijohdevalmistajien välillä. NVIDIA käyttää Samsungin ainakin toistaiseksi pienintä 8 nanometrin DUV-valmistusprosessia uusien Orin-koodinimmellisten Tegra-piirien tuotantoon.

Lähde: WCCFTech, TechNews

Huom! Foorumiviestistä saattaa puuttua kuvagalleria tai upotettu video.

Linkki alkuperäiseen uutiseen (io-tech.fi)

Palautelomake: Raportoi kirjoitusvirheestä

Viimeksi muokattu: