- Liittynyt

- 14.10.2016

- Viestejä

- 22 495

Kaotik kirjoitti uutisen/artikkelin:

Intel on vasta päässyt aloittamaan Ice Lake-SP -palvelinprosessoreiden tuotannon, mutta sen seuraajaa on huhuttu julkaistavaksi jo kuluvan vuoden aikana. Todennäköisemmin prosessorit kuitenkin saapuvat markkinoille aikaisintaan ensi vuoden puolella. Riippumatta lopulta toteutuvasta aikataulusta Sapphire Rapids -koodinimellä tunnetut seuraavan sukupolven Xeon Scalable -prosessorit ovat merkittävä julkaisu jo niiden tuomien uusien teknologioiden myötä.

[gallery link="file" columns="2" size="medium" ids="57826,57825"]

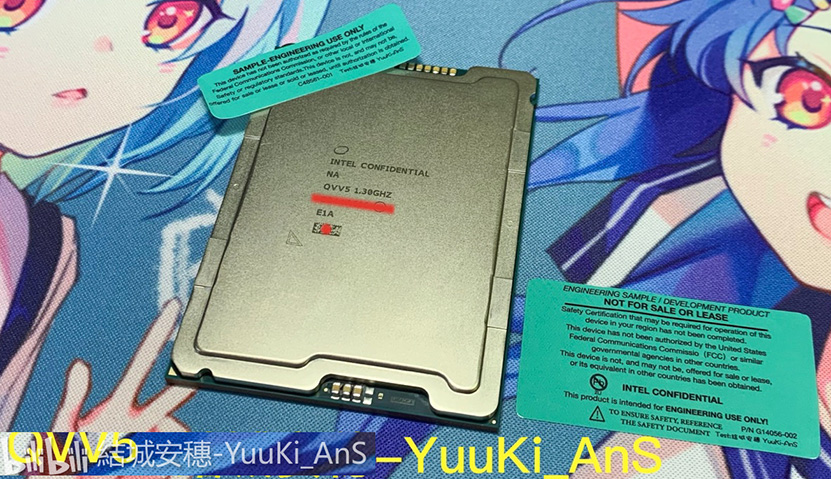

Luotettavista vuodoistaan tuttu HXL on twiitannut kiinalaisesta Bilibili-palvelusta löytämänsä kuvat tulevasta palvelinprosessorista. Alkuperäisen vuotajan mukaan LGA4677-X-kantaan sopiva ja 1,3 GHz:n peruskellotaajuudella toimiva Engineering Sample on joko viimeisiä ES0-tason prosessoreita tai askelta pidemmällä oleva ES1-versio. Se rakentuu ilmeisesti neljästä erillisestä prosessorisirusta, joissa HXL:n mukaan olisi mahdollisesti kussakin enimmillään 14 eli yhteensä 56 ydintä, mutta tästä ei ole vielä varmuutta.

Sapphire Rapids tulee olemaan näillä näkymin yksi ensimmäisistä DDR5-muisteja tukevista alustoista, mutta se tukee sen lisäksi suoraan prosessorin paketointiin integroituja HBM-muisteja. Vuodon mukaan paketin sisällä olisi neljä HBM-pinoa prosessorisirujen rinnalla. Sen lisäksi uusia teknologioita ovat tuki PCI Express 5.0:lle ja siihen perustuvalle avoimelle Compute Express Link -väylälle.

Päivitys:

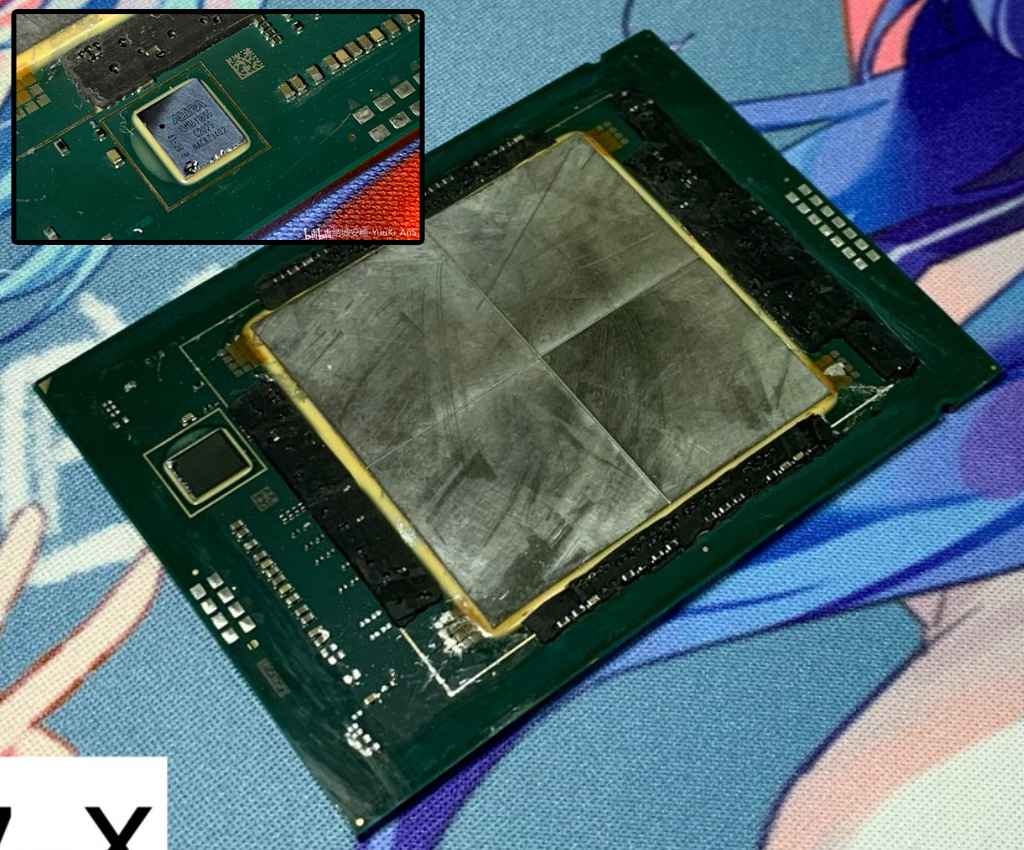

HXL löytänyt samasta lähteestä kuvan prosessorista myös ilman lämmönlevittäjää. Lämmönlevittäjän alta paljastuu alkuperäisen vuotajan mainitsemat neljä sirua, mutta mainostettuja HBM-muisteja kuvan prosessorissa ei ole nähtävillä. Sen sijasta mielenkiintoisena yksityiskohtana sirun reunalta löytyy yksi pienikokoinen Altera-brändätty piiri. Altera oli FPGA-piireihin erikoistunut yritys, jonka Intel kaappasi talliinsa vuonna 2015.

Lähde: HXL @ Twitter, Bilibili

Linkki alkuperäiseen juttuun

Viimeksi muokattu: