- Liittynyt

- 14.10.2016

- Viestejä

- 22 630

Puolijohdevalmistajien markkinoilla on nykyään jäljellä enää neljä jättiä: GlobalFoundries, Intel, Samsung ja TSMC. Kilpailu nelikon välillä on edelleen kovaa, mutta fysiikan lakeja vastaan kamppailu on hidastanut kehitystä viime vuosina selvästi yhtiöiden aiempiin suunnitelmiin nähden. Viime vuosiin on mahtunut niin kokonaan peruttuja prosesseja kuin julkaistujen prosessienkin myöhästymisiä vuodella tai jopa yli.

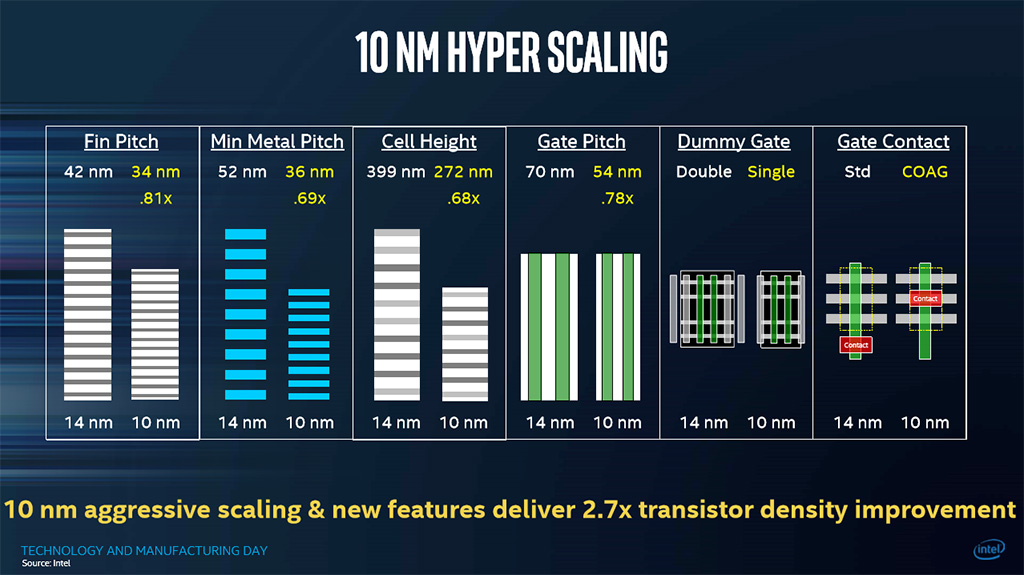

Puolijohdevalmistajien tarjontaa vertaillessa kannattaa aina muistaa, että yhden valmistajan 14 nanometriä ei välttämättä vastaa toisen valmistajan 14 nanometriä. Todellisuudessa nimellisesti saman viivanleveyden prosesseissa on merkittäviäkin eroja ja esimerkiksi Intelin arvioiden mukaan kilpailijoiden 10 nanometrin hilojen jakoväli olisi vain aavistuksen pienempi kuin yhtiön omassa 14 nanometrin prosessissa. Intel uskookin, että sen 10 nanometrin prosessi on kokonaisen sukupolven edellä kilpailijoita ja että sen transistoritiheys olisi niihin nähden kaksinkertainen.

Intel piti viime kuun lopulla Technology and Manufacturing Day -tapahtuman, jossa se valotti lähitulevaisuuden suunnitelmiaan puolijohdealalla. io-techin lukijoita tapahtuman annista kiinnostanee eniten pahasti myöhässä oleva 10 nanometrin valmistusprosessi, jolla Intel tulee valmistamaan seuraavan sukupolven Cannonlake-prosessorit.

Intelin mukaan sen 10 nanometrin prosessi skaalautuu selvästi normaalia paremmin kiitos Hyper Scaling -teknologian. Pienemmän viivanleveyden ja Hyper Scalingin ansiosta prosessin transistoritiheys tulee yli kaksinkertaistumaan 14 nanometriin nähden, sillä siinä missä Intelin 14 nm:n prosessilla yhdelle neliömillille mahtui 37,5 miljoonaa transistoria, tulee 10 nm:n prosessilla samaan tilaan mahtumaan peräti 100,8 miljoonaa transistoria.

Yhtiön mittausten mukaan sen 14 nm:n prosessilla evien jakoväli oli 42 nm, kun 10 nm:llä se on 0,81-kertainen eli 34 nm. Metallikerrosten jakoväli on puolestaan kutistunut 52 nm:stä 0,69-kertaiseksi eli 36 nm:iin, solujen korkeus 399 nm:stä 0,68-kertaiseksi 272 nm:iin ja hilojen jakoväli 70 nm:stä 0,78-kertaiseksi 54 nm:iin.

Prosessia entisestään pienentävän Hyper Scaling -teknologian alle kuuluvat kontaktin siirtäminen aktiivisen hilan päälle (COAG, Contact Over Active Gate) ja siirtyminen kahdesta valehilasta (Dummy Gate) yhteen valehilaan. Valehiloja käytetään solujen ulkoreunoilla. COAG:n kerrotaan parantavan prosessin skaalautumista noin 10 % kun kahdesta yhteen valehilaan siirtymisellä saadaan parannusta peräti 20 %.

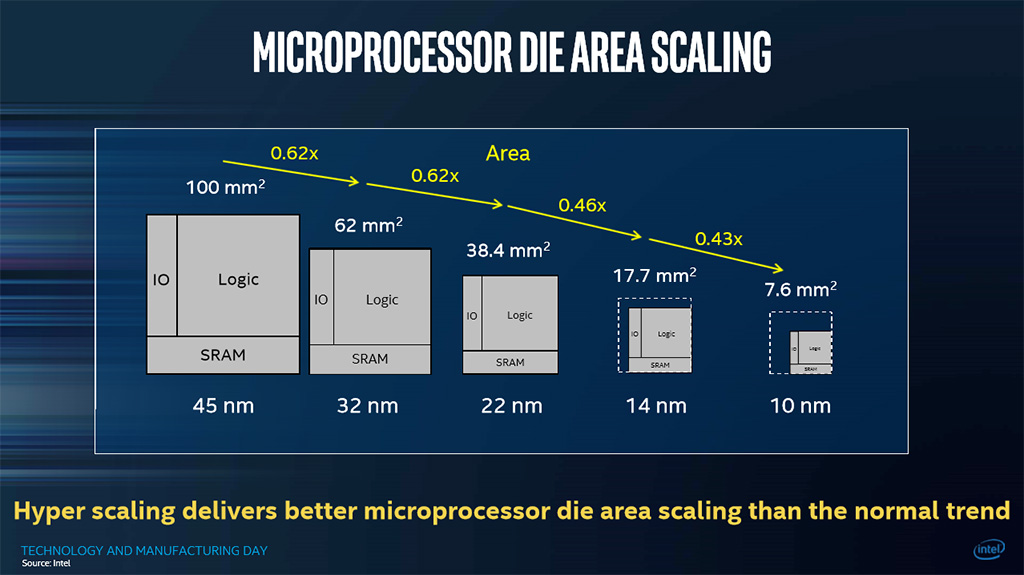

Yhdessä perinteisten ominaisuuksien ja Hyper Scaling -ominaisuuksien kanssa Intel laskee koko prosessin pinta-alatarpeen kutistuneen noin 0.37-kertaiseksi 14 nanometriin nähden. Kokonaisen prosessorin kohdalla skaalautuminen ei ole kuitenkaan aivan yhtä yksinkertaista. Intelin mukaan esimerkiksi hyppy 22 nanometristä 14 nanometriin pienensi saman prosessorin kokoa 0,46-kertaiseksi, vaikka teoreettisesti prosessin vaatima pinta-ala kutistuikin 0,37-kertaiseksi myös silloin. Vastaavasti 14 nm:stä 10 nm:iin siirryttäessä Intel laskee prosessorin koon kutistuvan noin 0,43-kertaiseksi teoreettisen 0,37-kertaisen sijasta.

Intel ei tule jäämään lepäämään laakereilleen 10 nanometrin prosessin valmistuttuakaan. Hamassa tulevaisuudessa odottaa 7 nanometrin prosessi, mutta sitä ennen Intel tulee julkaisemaan kaksi paranneltua painosta 10 nm:n prosessista. Intel julkaisi myös 14 nanometrin valmistusprosessista lopulta kaksi parannettua versiota.

Huom! Foorumiviestistä saattaa puuttua kuvagalleria tai upotettu video.

Linkki alkuperäiseen uutiseen (io-tech.fi)