- Liittynyt

- 14.10.2016

- Viestejä

- 21 607

Kaotik kirjoitti uutisen/artikkelin:

Tekniikan kehityksen kannalta avainasemassa olevien valmistusprosessien kehitys on viime vuosina hidastunut ja näillä näkymin on edelleen hidastumaan päin. Oman mausteensa soppaan tuovat myös eri tasoiset epäonnistumiset ja myöhästelyt, kuten Intelin surullisenkuuluisan 10 nanometrin prosessin tapauksessa.

WikiChip on ollut mukana IEEE:n jokavuotisessa International Electron Devices Meeting -tapahtumassa (IEDM), jossa on kuultu jälleen uutta eri puolijohdevalmistajilta. Mielenkiintoisinta ja toisaalta ikävintä antia tarjoili TSMC tulevilla 3 nanometrin luokan N3-perheen prosesseillaan: SRAMin skaalautuminen on pysähtymässä ainakin toistaiseksi.

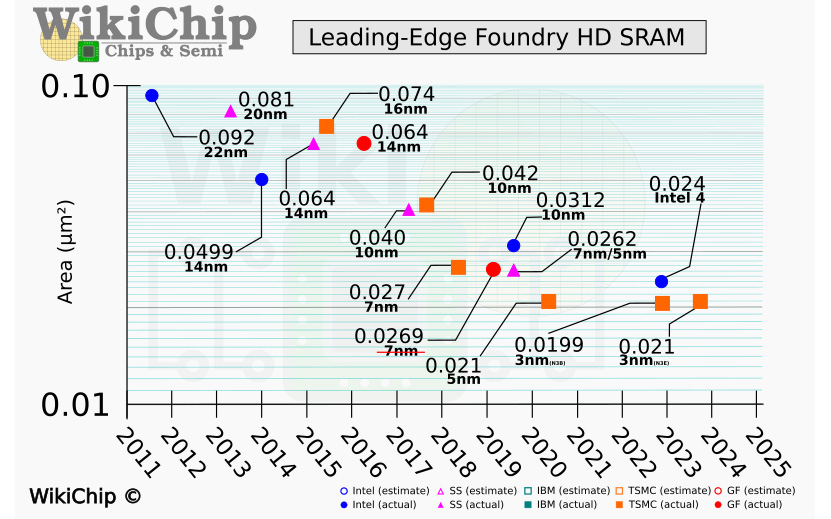

AMD toi esille RDNA3:n julkaisussa jälleen syitä, miksi se on siirtynyt useampaa sirua käyttävien piirien strategiaan. Yksi merkittävä tekijä näissä oli analogisten elementtien nollaa lähentelevä skaalaus, jonka lisäksi muistin skaalautuminen on yhtiön mukaan hidastunut selvästi, mikä on puolestaan ongelma koska juuri SRAMiin perustuvien välimuistien kasvatus on ollut viime sukupolvissa yksi merkittävistä tekijöistä lisäsuorituskyvyn takana. AMD:n ilmoittamaa muistin skaalautumisen hidastumista tukevat myös TSMC:n IEDM:ssä kertomat luvut.

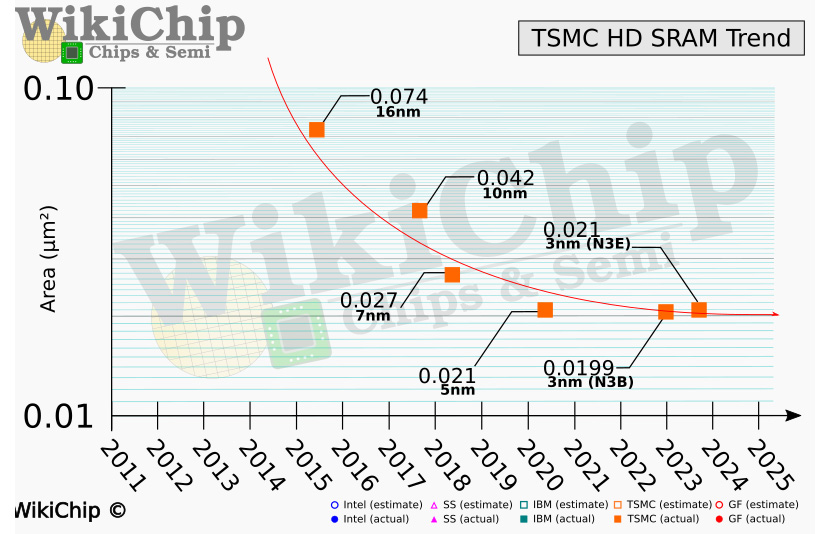

Nykyisen N5-prosessilla SRAM-solujen koko on 0,021 µm2. Tuleva N3-prosessi tulee edelleen kutistamaan sitä, mutta vain aavistuksen; SRAM-solujen kooksi kerrotaan olevan N3-prosessilla 0,0199 µm2. Vielä ikävämmäksi asia muuttuu siksi, että vain harvojen odotetaan käyttävän perusmuotoista N3-prosessia ja ottavan sen sijasta käyttöön N3E-prosessin, jota ei ole viritetty niin äärimmilleen. N3E:llä SRAM-solujen koko on samat 0,021 µm2 kuin N5:lläkin. N5:ttä edeltäneellä N7-prosessilla SRAM-solut olivat kooltaan 0,027 µm2, mutta jo silloin oli nähtävissä merkkejä skaalautumisen hidastumisesta. WikiChipin mukaan tilanne on vastaava myös muilla valmistajilla.

Tällä hetkellä todennäköisimmältä tieltä eteenpäin lähitulevaisuudessa näyttää AMD:n jo valitsema tie, jossa välimuistia sijoitetaan mahdollisesti vanhemmilla prosesseilla valmistettuina erillisille siruille itse pääsirulta. Tämä mahdollistaa välimuistien kasvamisen tiettyjen rajojen sisällä vielä tulevaisuudessakin, ilman että hinta räjähtäisi käsiin uunituoreen prosessin huonosti tai ei lainkaan skaalautuvien SRAM-solujen kanssa. Pidemmällä tähtäimellä esimerkiksi eurooppalainen puolijohdetutkimuslaitos IMEC on kuvaillut nykyiseen verrattuna noin kaksinkertaisen tiheyden SRAM-muisteja, mutta niiden kohdalla puhe on ollut kahden nanometrin luokan prosesseja kehittyneemmistä prosesseista. Myös tutkimusta muiden muistityyppien hyödyntämisen osalta tehdään luonnollisesti jatkuvasti, mutta niiden kanssa joudutaan ainakin tällä hetkellä tekemään jo kompromisseja muissa ominaisuuksissa tiheyden kasvattamiseksi.

Lähde: WikiChip

Linkki alkuperäiseen juttuun