- Liittynyt

- 14.10.2016

- Viestejä

- 25 085

Kaotik kirjoitti uutisen/artikkelin:

AMD:n ensimmäiseksi hybridiprosessoriksi huhuttu Phoenix2 on myllännyt vuotomaailman normaalin järjestyksen ympäri. Prosessori ilmestyi yleiseen tietouteen suoraan valokuvalla itse prosessorista ja pian AMD varmisti sillä olevan erillinen 6-ytiminen versio Phoenixista.

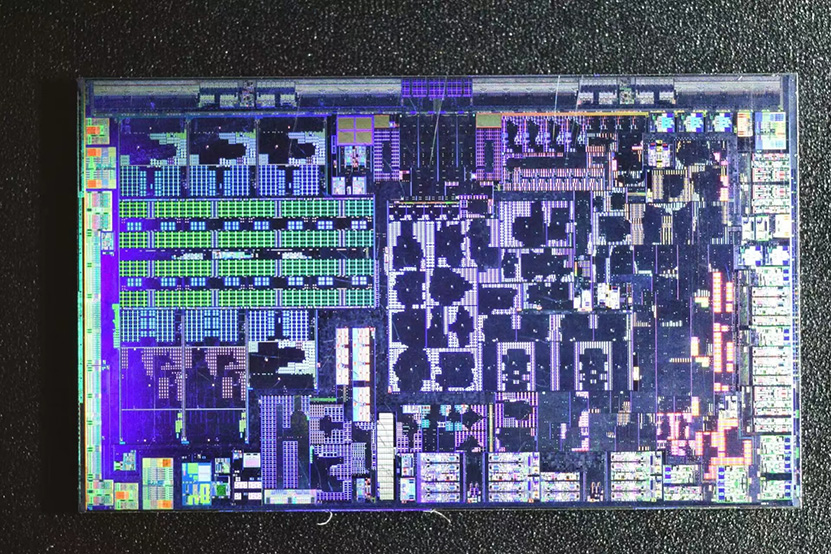

Vaikka AMD ei suoraan sanonut 6-ytimisen Phoenixin perustuvan hybridiarkkitehtuuriin, ensimmäinen vuotokuva vihjasi jo hyvin vahvasti sen suuntaan kokoeron vuoksi. Nyt X:n luottovuotajiin lukeutuva HXL on julkaissut viestintäpalvelussa valokuvan, jossa itse sirun rakenne on hiottu näkyviin. Kuva samalla käytännössä varmistaa Phoenix2:n todella olevan hybridiarkkitehtuurilla, sillä kaksi erillistä 6-ytimistä monoliittista APU-piiriä olisi äärimmäisen epätodennäköistä.

Sirun rakenteen kuvassa on helposti nähtävissä prosessorin eri elementtejä. Vasemmasta reunasta löytyy prosessoriytimet, jotka on sijoitettu kolmen ytimen riveihin L3-välimuistin kummallekin puolen. Hieman erikoisesti asetelma on kuitenkin epäsymmetrinen, sillä toisella puolella kaksi ytimistä on täyskokoisia Zen 4 -ytimiä ja yksi Zen 4c, kun yläpuolella kaikki kolme ovat pienempiä Zen 4c -ytimiä.

X-ketjun vastauksista löytyy myös käyttäjän ”three twenty six” julkaisema kuva, jossa on eroteltu prosessorin eri osia toisistaan. Vastaavista kaavioistaan tuttu Locuza on vahvistanut merkintöjen olevan oikein, mutta merkittäviä osia prosessorista ei ole osattu erotella tietyiksi yksiköiksi. Grafiikkaohjain on sijoitettu keskelle sirua kaksine WGP-yksiköineen (4 Compute Unit -yksikköä) ja sen yläpuolelta löytyy mediayksikkö, joskin sen tarkempi asettelu ei ole varmaa. Sirun alalaidan oikean puoliskon täyttävät PCIe-väylien PHY:t ja oikealta laidalta USB- ja näyttöyhteyksiä tukevat PHY:t. Ylälaita on muistiohjainten PHY:t ja niiden ohjain löytyy keskeltä sirun ylälaitaa.

Lähde: HXL @ X

Linkki alkuperäiseen juttuun

Viimeksi muokattu: