- Liittynyt

- 14.10.2016

- Viestejä

- 23 722

Kaotik kirjoitti uutisen/artikkelin:

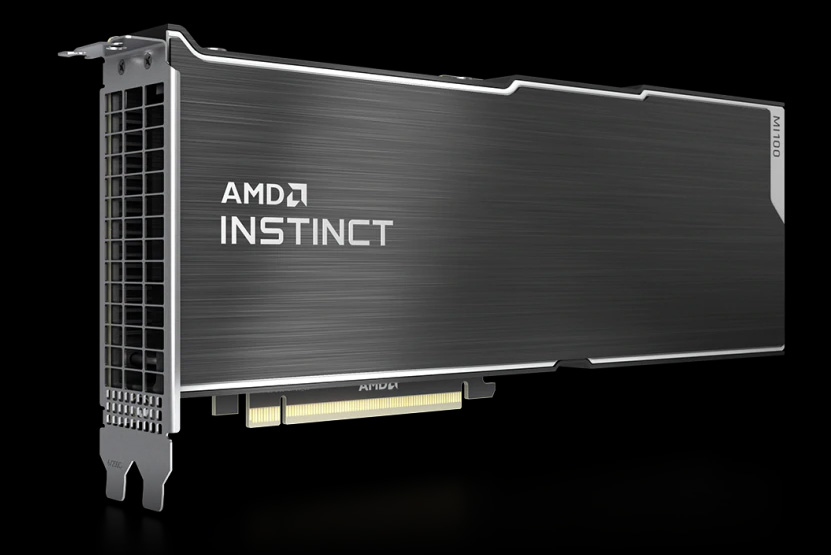

AMD on julkaissut tänään jo pitkään odotetun, Arcturus-koodinimellä tunnetun ensimmäisen erillisen laskentapiirinsä. AMD Instinct MI100 -nimellä julkaistu laskentakortti on yhtiön mukaan maailman nopein ja samalla ensimmäinen yli 10 teraFLOPSin FP64-suorituskykyyn yltävä HPC-luokan GPU.

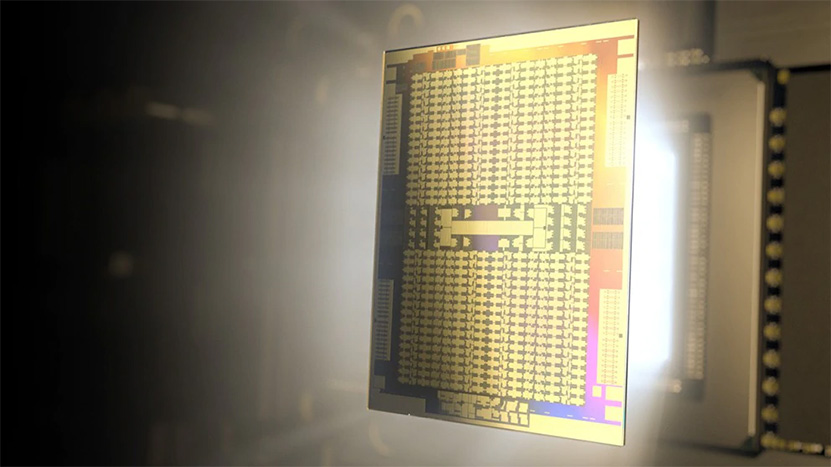

AMD:n CDNA-arkkitehtuuriin perustuva Instinct MI100 valmistetaan TSMC:n 7 nanometrin prosessilla, mutta yhtiö ei paljastanut esimerkiksi monestako transistorista se rakentuu. CDNA-arkkitehtuuri itsessään perustuu edelleen kehitettyyn GCN-arkkitehtuurin pohjaan, mutta paljon on myös muuttunut.

MI100:ssa on käytössä 120 Compute Unit -yksikköä, jotka on jaettu neljään Compute Engine -osioon. Jokaisessa CU-yksikössä on perinteisten skalaari- ja vektoriyksiköiden rinnalla Matrix Core Engine, joka on suunniteltu kiihdyttämään matriisilaskuja. MCE-yksiköt laskevat Matrix Fused Multiply-Add- eli MFMA-tehtäviä KxN-matriiseilla INT8-, FP16-, BF16- ja FP32-tarkkuuden luvuilla. MFMA-laskujen tulos lasketaan tarpeen mukaan joko INT32- tai FP32-tarkkuudella.

MI100:n teoreettinen FP32-suorituskyky on 23,1 ja FP64-suorituskyky 11,5 TFLOPSia. FP32-matriisilaskujen teoreettinen maksiminopeus on 46,1 TFLOPSia, FP16-matriisilaskujen 184,6 TFLOPSia ja INT4- ja INT8-laskujen niin ikään 184,6 TFLOPSia. Bfloat16-tarkkuudella teoreettinen maksimisuorituskyky on 92,3 TFLOPSia.

Laskentayksiköiden tukena on 8 megatavua L2-välimuistia jaettuna 32 siivuun. L2-välimuistiin kerrotaan olevaan yhteenlaskettua kaistaa jopa 6 Tt sekunnissa. Yhteensä 4096-bittinen muistiohjain tukee sekä 4- että 8-kerroksisia HBM2-muisteja 2,4 Gt/s:n nopeudella, mikä tarkoittaa yhteensä 1,23 Tt/s:n muistikaistaa ja 32 gigatavua muistia. Laskentakortin TDP-arvo on 300 wattia.

[embed]

Instinct MI100 tukee myös toisen sukupolven Infinity Fabric -linkkiä laskentakorttien välillä ja maksimissaan neljän GPU:n naittamista samaan ryhmään sillan avulla. Kussakin GPU:ssa on kolme IF-linkkiä, joiden myötä neljän MI100-kiihdyttimen välillä on yhteensä 552 Gt/s teoreettista P2P-kaistaa. Prosessoriin kiihdyttimet ovat yhteydessä PCI Express 4.0 -väylän yli.

Yhdessä uusien laskentakorttien mukana julkaistiin uusi avoimen lähdekoodin ROCm 4.0. ROCm-pakettiin kuuluu erilaisia työkaluja kehittäjien tarpeisiin kääntäjistä rajapintoihin ja valmiisiin kirjastoihin. ROCm 4.0:n uusi avoimen lähdekoodin kääntäjä tukee sekä OpenMP 5.0- että HIP-rajapintoja.

AMD:n mukaan valmiita palvelinkonfiguraatioita Instinct MI100 -kiihdyttimillä on luvassa ainakin Delliltä, Gigabyteltä, Hewlett Packard Enterpriseltä ja Supermicrolta.

Lähde: AMD

Linkki alkuperäiseen juttuun

[/embed]