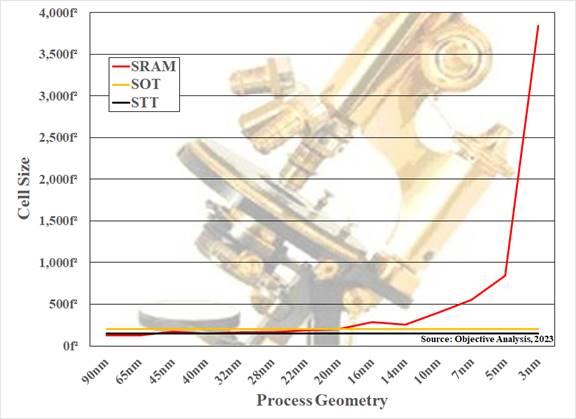

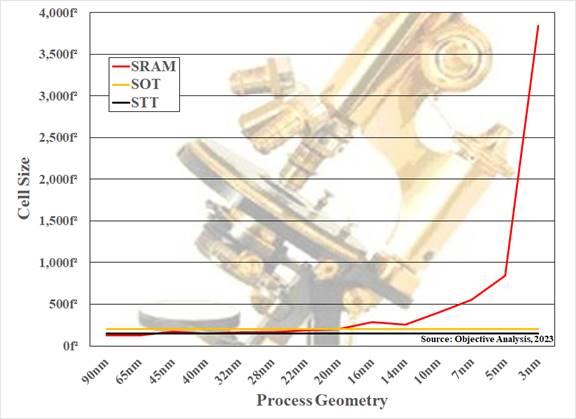

SRAM:in skaalautumisen hidastuminen oli jo huomattu aiempien valmistusprosessisukupolvien kohdalla ja 3 nm prosessisukupolven kohdalla se oli pysähtynyt täysin nähden edelliseen 5 nm prosessisukupolveen, mikä tarkoitti lisääntyneitä kustannuksia muistille.

TSMC on ilmoittanut, että sen N2-prosessitekniikka (2nm-luokka) tulee tarjoamaan merkittäviä parannuksia suorituskykyyn, energiaehokkuuteen ja pinta-alaan, verrattuna edellisen sukupolven prosesseihin. Myös SRAMin kohdalla tulee merkittäviä parannuksia solujen kokoon ja saavutetaan suurempi SRAM-tiheys, mikä on merkittävä läpimurto, koska HD (high density) SRAM oli loppettanut skaalautumisen kokonaan edellisessä 3 nm prosessisukupolvessa.

TSMC:n tulevassa N2-prosessissa nähdään ensimmäistä kertaa gate-all-around (GAA) nanosheet (nanolevy) -transistorit, joilla saavutetaan merkittävä virrankulutuksen pieneneminen sekä suorituskyvyn ja transistorin tiheyden lisäys.

Verrattuna N3-prosessisukupolveen, N2:lle rakennettujen sirujen odotetaan vähentävän virrankulutusta 25 - 30 prosenttia (vastaavalla transistorien määrällä ja taajuudella), lisäävän suorituskykyä 10–15 prosenttia (samalla transistorien määrällä ja virrankulutuksella) tai saavuttaa 15 %:n lisäys transistorin tiheyteen (samalla nopeudella ja virrankulutunsella).

Mutta erityisen merkittävä piirre TSMC:n N2 valmistusprosessissa on HD SRAM -bittisolun koon kutistuminen 16,67 % N5 ja N3 prosessien 21000 nm^2:stä noin 17 500 nm^2:iin mahdollistaen 38 Mb/mm^2 SRAM-tiheyden.

Tämä on suuri läpimurto, sillä SRAM:in skaalautuminen oli käytännössä pysähtynyt seinään, kuten alla olevasta kuvasta ilmenee.

Asia kävi ilmi tutkimuksesta, jonka TSMC esittelee joulukuun alussa olevassa IEDM-konferenssissa, joka keskittyy elektronisten laitteiden ja puolijohteiden tutkimukseen, kehitykseen ja sovelluksiin.

TSMC:n GAA-nanolevytransistorit näyttävät olevan pääasiallinen syy, joka mahdollistaa pienempien HD SRAM -bittisolukokojen käyttön.

GAA-transistorit mahdollistaa transistorien koon pienenemisen suorituskyvyn säilyttäen, mikä on ratkaisevan tärkeää yksittäisten komponenttien, kuten SRAM-kennojen, koon pienentämisessä.

GAA-rakenteet mahdollistavat myös tarkemman kynnysjännitteen, mikä on välttämätöntä transistorien ja erityisesti SRAM-kennojen luotettavalle toiminnalle mahdollistaen niiden koon pienentämisen edelleen.

Modernit prosessorit, näytönohjaimet ja järjestelmäpiirit vaativat paljon SRAMia, sillä nämä käyttävät runsaasti SRAMia eri välimuistien hallintaan, mikä mahdollistaa suuren datamäärän tehokkaan käsittelyn.

Muistista tietojen hakeminen on sekä suorituskykyä heikentävää että energiaa kuluttavaa, joten riittävä SRAM on ratkaisevan tärkeää optimaalisen suorituskyvyn saavuttamiseksi, jonka takia tulevaisuudessa välimuistien ja SRAMin kysynnän odotetaan kasvavan, minkä takia TSMC:n saavutukset SRAM-solujen koon pienentämisessä ovat erittäin merkittäviä.

www.tomshardware.com

www.tomshardware.com

semiengineering.com

semiengineering.com

TSMC on ilmoittanut, että sen N2-prosessitekniikka (2nm-luokka) tulee tarjoamaan merkittäviä parannuksia suorituskykyyn, energiaehokkuuteen ja pinta-alaan, verrattuna edellisen sukupolven prosesseihin. Myös SRAMin kohdalla tulee merkittäviä parannuksia solujen kokoon ja saavutetaan suurempi SRAM-tiheys, mikä on merkittävä läpimurto, koska HD (high density) SRAM oli loppettanut skaalautumisen kokonaan edellisessä 3 nm prosessisukupolvessa.

TSMC:n tulevassa N2-prosessissa nähdään ensimmäistä kertaa gate-all-around (GAA) nanosheet (nanolevy) -transistorit, joilla saavutetaan merkittävä virrankulutuksen pieneneminen sekä suorituskyvyn ja transistorin tiheyden lisäys.

Verrattuna N3-prosessisukupolveen, N2:lle rakennettujen sirujen odotetaan vähentävän virrankulutusta 25 - 30 prosenttia (vastaavalla transistorien määrällä ja taajuudella), lisäävän suorituskykyä 10–15 prosenttia (samalla transistorien määrällä ja virrankulutuksella) tai saavuttaa 15 %:n lisäys transistorin tiheyteen (samalla nopeudella ja virrankulutunsella).

Mutta erityisen merkittävä piirre TSMC:n N2 valmistusprosessissa on HD SRAM -bittisolun koon kutistuminen 16,67 % N5 ja N3 prosessien 21000 nm^2:stä noin 17 500 nm^2:iin mahdollistaen 38 Mb/mm^2 SRAM-tiheyden.

Tämä on suuri läpimurto, sillä SRAM:in skaalautuminen oli käytännössä pysähtynyt seinään, kuten alla olevasta kuvasta ilmenee.

Asia kävi ilmi tutkimuksesta, jonka TSMC esittelee joulukuun alussa olevassa IEDM-konferenssissa, joka keskittyy elektronisten laitteiden ja puolijohteiden tutkimukseen, kehitykseen ja sovelluksiin.

TSMC:n GAA-nanolevytransistorit näyttävät olevan pääasiallinen syy, joka mahdollistaa pienempien HD SRAM -bittisolukokojen käyttön.

GAA-transistorit mahdollistaa transistorien koon pienenemisen suorituskyvyn säilyttäen, mikä on ratkaisevan tärkeää yksittäisten komponenttien, kuten SRAM-kennojen, koon pienentämisessä.

GAA-rakenteet mahdollistavat myös tarkemman kynnysjännitteen, mikä on välttämätöntä transistorien ja erityisesti SRAM-kennojen luotettavalle toiminnalle mahdollistaen niiden koon pienentämisen edelleen.

Modernit prosessorit, näytönohjaimet ja järjestelmäpiirit vaativat paljon SRAMia, sillä nämä käyttävät runsaasti SRAMia eri välimuistien hallintaan, mikä mahdollistaa suuren datamäärän tehokkaan käsittelyn.

Muistista tietojen hakeminen on sekä suorituskykyä heikentävää että energiaa kuluttavaa, joten riittävä SRAM on ratkaisevan tärkeää optimaalisen suorituskyvyn saavuttamiseksi, jonka takia tulevaisuudessa välimuistien ja SRAMin kysynnän odotetaan kasvavan, minkä takia TSMC:n saavutukset SRAM-solujen koon pienentämisessä ovat erittäin merkittäviä.

SRAM scaling isn't dead after all — TSMC's 2nm process tech claims major improvements

SRAM scales again with GAA transistors.

SRAM Scaling Issues, And What Comes Next

While it will remain a workhorse memory, using SRAM at advanced nodes requires new approaches.

Viimeksi muokattu: