- Liittynyt

- 14.10.2016

- Viestejä

- 22 377

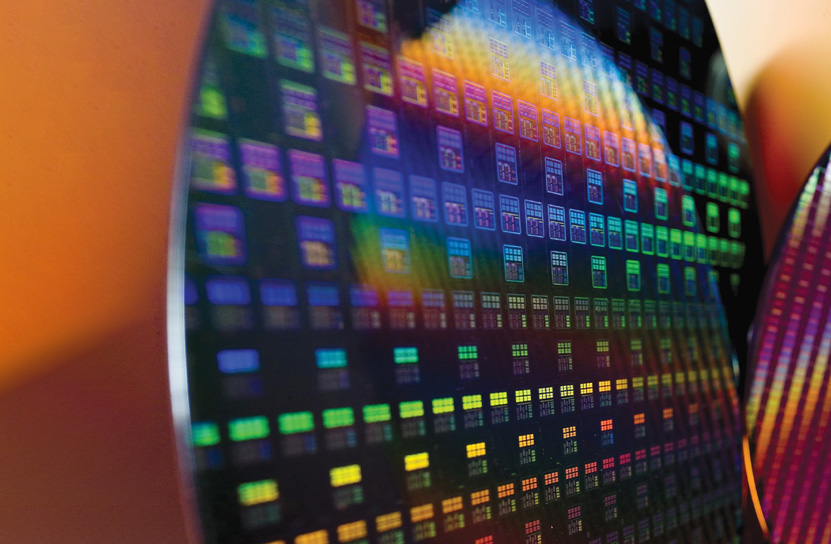

Puolijohdevalmistajia on jäljellä enää muutama, mutta se ei ole hidastanut yhtiöiden halua kehittää uusia, aiempaa pienempiä prosesseja. Tällä kertaa uusista prosesseistaan ovat ilmoittaneet Samsung ja TSMC.

Samsungin mukaan se on saanut valmiiksi kehitystyön 5 nanometrin FinFET-prosessin tiimoilta ja on valmis aloittamaan asiakaspiirien samplauksen prosessilla. Uusi prosessi hyödyntää EUV-litografiaa (Extreme UltraViolet), mikä mahdollistaa aiempaa pienempien yksityiskohtien valottamisen vähemmillä maskeilla, kuin perinteiset prosessit.

Yhtiön mukaan sen 5 nanometrin prosessi parantaa suorituskykyä 10 % samalla tehonkulutuksella tai tarjoaa saman suorituskyvyn 25 % pienemmällä tehonkulutuksella 7 nanometriin nähden pakaten samalla transistorit 25 % aiempaa pienempään tilaan. 5 nanometrin prosessi käyttää ilmeisesti samoja suunnittelusääntöjä kuin 7 nanometrin prosessi, mikä tekee uusien piirien kehitystyöstä nopeampaa.

Lisäksi Samsung kertoi kehittäneensä kustomoidun 6 nanometrin EUV-prosessin, jolla on onnistuneesti tuotettu jo ensimmäiset sirut.

TSMC on puolestaan esitellyt uuden 6 nanometrin valmistusprosessin. Samsungin 5 nm:n tapaan TSMC:n uusi FinFET-prosessi hyödyntää EUV-litografiaa.

Yhtiön mukaan sen 6N:ksi nimetty uusi prosessi parantaa transistorien tiheyttä 18 %, mutta se ei ole paljastanut mitä prosessilta voidaan odottaa suorituskyvyn ja tehonkulutuksen osalta. 6N-prosessi käyttää samoja suunnittelusääntöjä kuin aiempi 7N+-EUV-prosessi, mikä helpottaa asiakkailta vaadittavaa kehitystyötä uuteen prosessiin siirryttäessä.

TSMC:n 6N-prosessi siirtyy riskituotantoon ensi vuoden ensimmäisellä neljänneksellä.

Lähteet: Samsung, TSMC

Huom! Foorumiviestistä saattaa puuttua kuvagalleria tai upotettu video.

Linkki alkuperäiseen uutiseen (io-tech.fi)

Palautelomake: Raportoi kirjoitusvirheestä

Viimeksi muokattu: