- Liittynyt

- 14.10.2016

- Viestejä

- 22 377

Kaotik kirjoitti uutisen/artikkelin:

Avoimen RISC-V-arkkitehtuurin johtaviin kehittäjiin lukeutuva SiFive on ilmoittanut tänään merkittävistä uutisista. Yhtiö on aloittanut yhteistyön Intelin kanssa sekä kehitysalustojen että tuotannon puolella.

Intel tulee tarjoamaan SiFiven IP-portfoliota (Intellectual Property, immateriaalioikeudet) jatkossa Intel Foundry Services -tuotantolaitosten asiakkaille 7 nanometrin prosessilla toteutettuna. Intel pyrkii IFS:n kautta kilpailemaan vakavasti TSMC:n, Samsungin ja muiden puolijohdevalmistajien kanssa asiakaspiirien tuotannosta ja on ilmoittanut aiemmin tulevansa lisensoimaan jopa x86-ytimiään asiakaspiireihin.

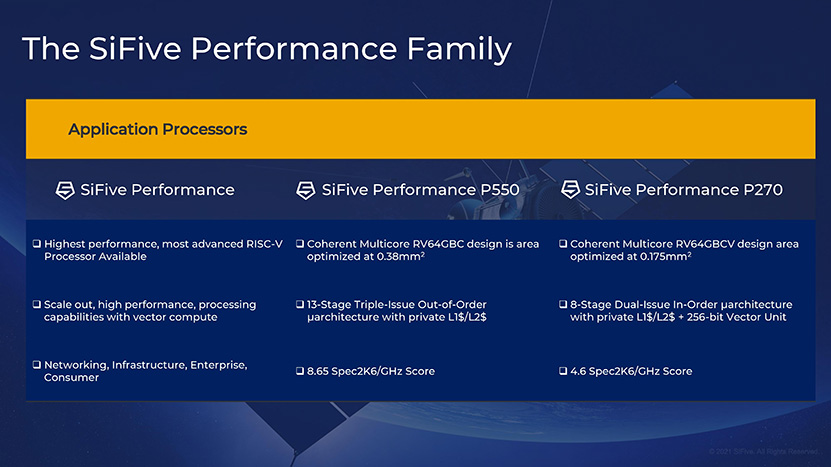

SiFiven RISC-V IP on ensimmäinen kolmannen osapuolen IP, jota tullaan tarjoamaan IFS:n asiakkaille. Pakettiin kuuluvat tässä vaiheessa ainakin SiFive Performance P550- ja P270-ytimet. P550 eli RV64GBC on pinta-alaoptimoitu arkkitehtuuri, jonka ytimet vievät 7 nanometrin prosessilla tilaa vain 0,38 mm2. Ytimet ovat 13-vaiheisia kolme käskyä kerralla liikuttaviaa Out-of-Order-tyyppisiä RISC-V-ytimiä, joilla on oma L1- ja L2-tason välimuistinsa. P550 on suunniteltu maksimissaan neliytimiseksi ja ytimet jakavat L3-välimuistin keskenään. Kevyempi P270 eli RV64GBCV vie tilaa vaivaiset 0,175 mm2 ja ne ovat 8-vaiheisia kahta käskyä kerralla liikuttavia In-Order-tyyppisiä RISC-V-ytimiä.

Toinen aiheeseen liittyvä merkittävä uutinen on puolestaan Intelin päätös julkaista SiFiven Performance P550 -kehitysalusta. Horse Creek -koodinimellä ja 7 nanometrin prosessilla valmistettava kehitysalusta tulee hyödyntämään P550-ytimiä, mutta esimerkiksi PCIe-ohjaimet ja DDR-muistiohjaimet tulevat olemaan Intelin käsialaa. Kehitysalusta tuodaan markkinoilla ensi vuoden aikana.

Lähteet: AnandTech (1), (2)

Linkki alkuperäiseen juttuun