finWeazel

Chief Karpfen - ruoKalan C&R

- Liittynyt

- 15.12.2019

- Viestejä

- 8 998

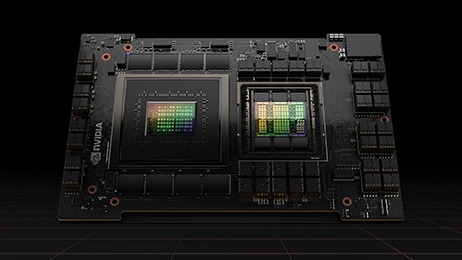

Nvidia on julkaisemassa ARM-pohjaista Grace-suoritinta alkuvuodesta 2023 suorituskykyiseen(HPC) ja tieteelliseen laskentaan. Nvidia on hiljattain julkaissut aloitusoppaan ARM HPC käyttöä varten. Opas on yleinen ja toimii muidenkin valmistajien ARM-suorittimien kanssa. Referenssinä, jolla opasta voi testata on Ampere Altra Q80-30 suoritin. Opas ei vaadi GPU:ta. Oppaan mukaan GPU:n käyttö X86 ja ARM-alustoilla ei eroa toisistansa. Iso osa X86 vs. ARM eroista vaikuttaisi olevan ohjelmistojen kääntämistä lähdekoodista ARM-alustalle ja muuta suoritinriippuvaista asiaa.

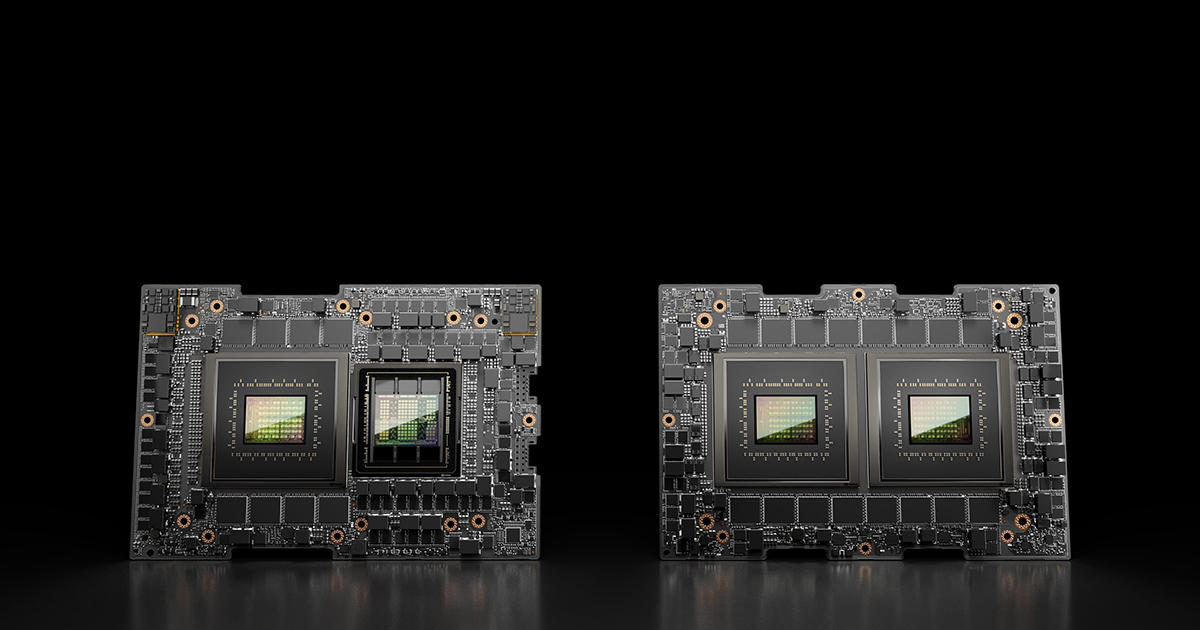

ARM-suorittimet ovat mielenkiintoinen lisä pilviympäristöön, jossa X86-suorittimet AMD:lta ja Inteliltä ovat merkittäviä tekijöitä. Spekuloida voi esimerkisi ARM suorituskyvystä ja virrankulutuksesta versus X86-suorittimet. Spekuloida voi myös Nvidian referenssiratkaisuista, joissa käytettiin yksinoikeudella X86 piirejä aikaisemmin. Ampere aikakaudella Nvidian referenssialusta käytti AMD:n suoritinta. Hopper referenssit käyttävät Intelin X86-suoritinta ja Nvidian omaa Grace-ARM-suoritinta.

Oppaan on ilmeisesti kirjoittanut/julkaissut John Linford

Linkki oppaaseen:

github.com

github.com

Kooste Nvidian Grace-suorittimen pääominaisuusista.

ARM-suorittimet ovat mielenkiintoinen lisä pilviympäristöön, jossa X86-suorittimet AMD:lta ja Inteliltä ovat merkittäviä tekijöitä. Spekuloida voi esimerkisi ARM suorituskyvystä ja virrankulutuksesta versus X86-suorittimet. Spekuloida voi myös Nvidian referenssiratkaisuista, joissa käytettiin yksinoikeudella X86 piirejä aikaisemmin. Ampere aikakaudella Nvidian referenssialusta käytti AMD:n suoritinta. Hopper referenssit käyttävät Intelin X86-suoritinta ja Nvidian omaa Grace-ARM-suoritinta.

Oppaan on ilmeisesti kirjoittanut/julkaissut John Linford

Linkki oppaaseen:

The NVIDIA Arm HPC Developer Kit (simply "DevKit" in this guide) is an integrated hardware and software platform for creating, evaluating, and benchmarking HPC, AI, and scientific computing applications on a heterogeneous GPU- and CPU-accelerated computing system. The kit includes an Arm CPU, dual NVIDIA A100 Tensor Core GPUs, and the NVIDIA HPC SDK suite of tools. See the product page for more information.

GitHub - arm-hpc-devkit/nvidia-arm-hpc-devkit-users-guide: Get started with your NVIDIA Arm HPC Developers Kit!

Get started with your NVIDIA Arm HPC Developers Kit! - arm-hpc-devkit/nvidia-arm-hpc-devkit-users-guide

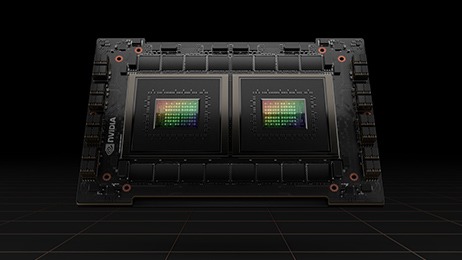

Kooste Nvidian Grace-suorittimen pääominaisuusista.

NVIDIA Grace CPU Superchip uses the NVLink-C2C technology to deliver 144 Arm® v9 cores and 1 TB/s of memory bandwidth.

- High performance CPU for HPC and cloud computing

- Super chip design with up to 144 Arm v9 CPU cores

- World’s first LPDDR5x with ECC Memory, 1TB/s total bandwidth

- SPECrate®2017_int_base over 740 (estimated)

- 900 GB/s coherent interface, 7X faster than PCIe Gen 5

- 2X the packaging density of DIMM-based solutions

- 2X the performance per watt of today’s leading CPU

- Runs all NVIDIA software stacks and platforms, including NVIDIA RTX, HPC, NVIDIA AI, and NVIDIA Omniverse

Introducing Grace

Viimeksi muokattu: