- Liittynyt

- 14.10.2016

- Viestejä

- 22 435

Kaotik kirjoitti uutisen/artikkelin:

Intelin seuraavan sukupolven Core-prosessorit tottelevat tällä hetkellä koodinimeä Meteor Lake. WCCFTech on saanut nyt haltuunsa joitain Intelin Hot Chips -dioista, jotka kertovat paitsi Meteor Lakesta, myös sen seuraajista.

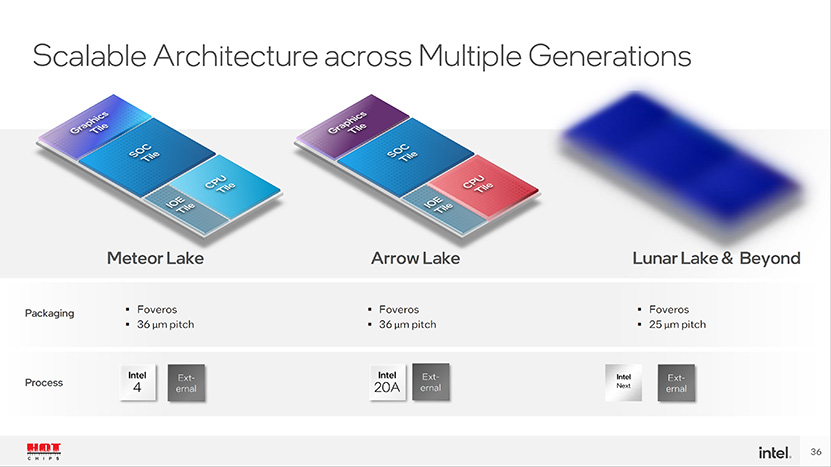

Diojen mukaan Intel aikoo käyttää samaa ”perusarkkitehtuuria” useamman sukupolven yli. Pakettiin kuuluvat Graphics-, SOC-, IO- ja Compute Tilet (kuvassa CPU), eli sirut, jotka Foveros-paketoidaan yhteen pakettiin. Jokainen osa on vaihdettavissa toisistaan riippumatta ja suunniteltu skaalautuviksi tarpeen mukaan. Sama asettelu tulee pysymään ainakin Arrow Lakessa ja todennäköisesti Lunar Lakessa, joskin sen sumennus voisi vihjata myös sirujen määrän muuttumiseen. Meteor Lake ja Arrow Lake hyödyntävät Intelin 36 µm Foveros-paketointia, kun Lunar Lakessa tullaan siirtymään 25 µm:n kontaktipintoja käyttävään Foveros-paketointiin.

Ainakin kolme seuraavaa sukupolvea tulevat hyödyntämään Intelin omien lisäksi myös ulkopuolisia prosesseja. Meteor Lakessa tiedettiin jo entuudestaan olevan käytössä Intel 4:n lisäksi yksi TSMC:n N5- ja kaksi N6-prosessilla varustettua sirua. Arrow Lakessa Intelin oma prosessi päivittyy 20A:ksi, mutta Lunar Laken prosessia ei vielä paljastettu.

WCCFTech on vetänyt artikkelissaan mutkia suoriksi dioissa esimerkkeinä käytetyistä ydinkonfiguraatioista suoraan seuraavan sukupolven ydinkonfiguraatioita arpomalla, mikä kannattaa jättää ainakin tässä vaiheessa omaan arvoonsa. Sivuston mukaan Meteor Lake- ja Arrow Lake -prosessoreissa tulee olemaan käytössä LGA1851-kanta, mutta tämän tiedon lähde ei ainakaan allekirjoittaneella osunut silmiin.

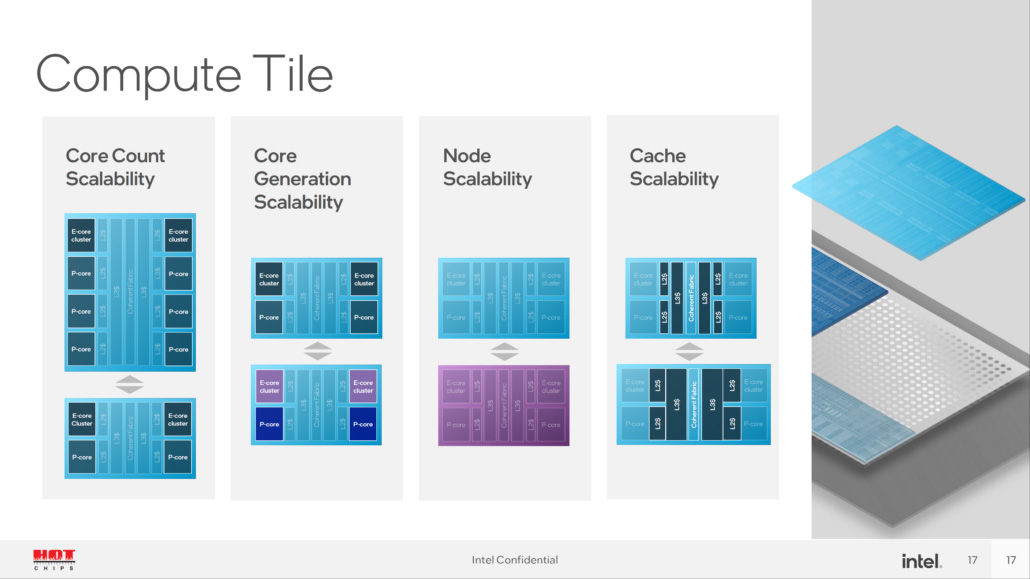

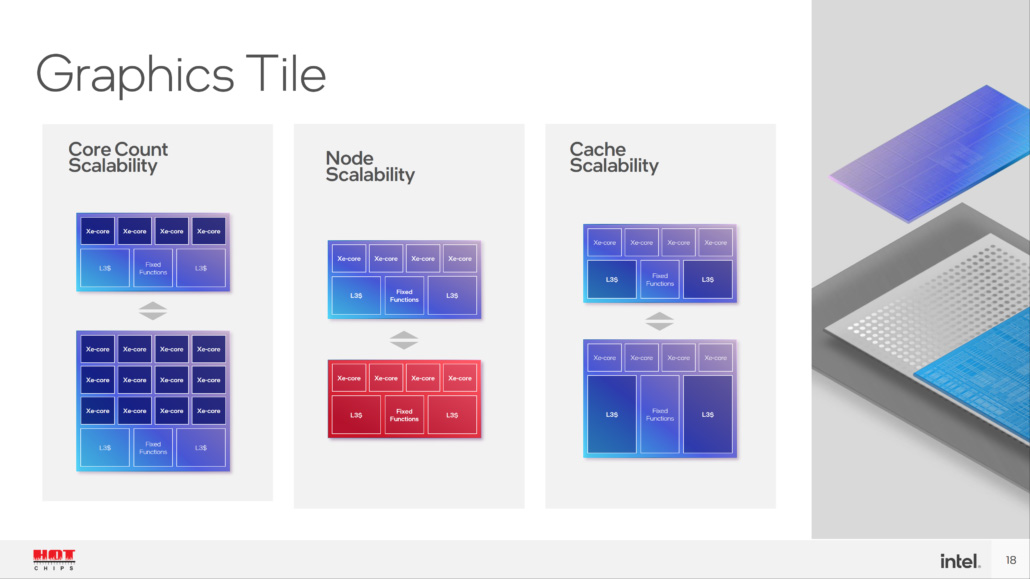

Intelin Compute Tile -diassa esitetään, kuinka ydinmäärät voivat skaalautua kahdesta P-ytimestä ja kahdesta E-ydinryppäästä kuuteen P-ytimeen ja kahteen E-ydinryppääseen. Ytimet asetellaan siis sirulla fyysisesti siten, että ensin on vastapäiset E-ydinryppäät ja sen jälkeen vastaavasti vastapäisiä P-ytimiä. Ytimiä voidaan myös päivittää eri mikroarkkitehtuureihin ja valmistusprosesseihin arkkitehtuurin perusasettelua muokkaamatta. Myös välimuistien määrät ovat skaalattavissa riippumatta muista osista. Graphics Tile -diassa esitetään puolestaan skaalautuvuutta neljästä Xe-ytimestä 12 Xe-ytimeen ja vastaavasti valmistusnoodin päivitettävyys sekä välimuistin koon skaalautuvuus.

Lähde: WCCFTech

Linkki alkuperäiseen juttuun