- Liittynyt

- 14.10.2016

- Viestejä

- 21 919

Intel julkisti hiljattain uuden Compute Express Link- eli CXL-väylän, mutta moni yksityiskohta sen toteutuksesta jäi hämärän peittoon. Nyt Intel on kertonunt lisää uudesta väylästä ja sen toteutuksesta Interconnect Day -tapahtumassaan.

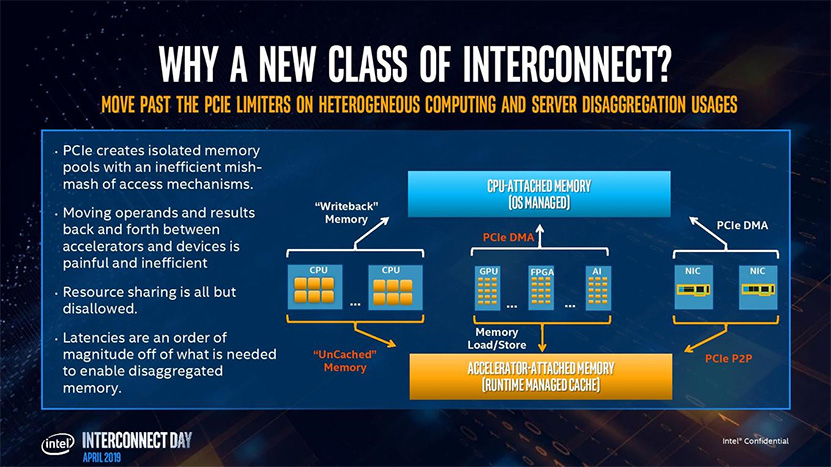

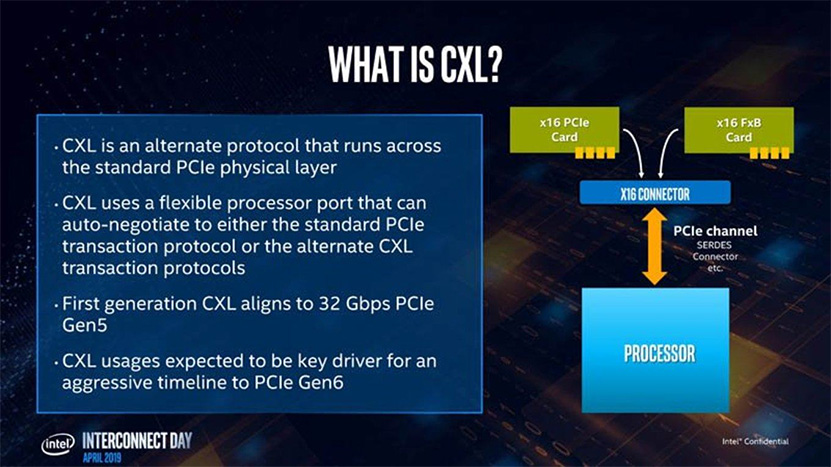

Intelin Compute Express Link pohjautuu PCI Express 5.0 -väylään fyysisesti, mutta yhtiön omilla protokollilla. Eri protokollien käyttö mahdollistaa esimerkiksi matalammat latenssit sekä koherentit yhteiset välimuistikoherentit muistialueet eri laitteiden välille, toisin kuin PCI Express. Lisäksi PCIe:n latenssit ovat selvästi korkeammat, kuin mitä CXL:n protokollien käyttö mahdollistaa.

Intelin mukaan CXL-väylää tukeva prosessori tunnistaa automaattisesti PCIe-väylän toisessa päässä olevan laitteen kyvyt ja valitsee sen mukaan joko PCI Express- tai CXL-standardin mukaisen protokollan liikenteelle. CXL-protokolla koostuu puolestaan kolmesta aliprotokollasta, CXL.io:sta, CXL.cachesta ja CXL.memorystä.

CXL.io on vastuussa nimensä mukaisesti erilaisista I/O-mekanismeista sekä laitteiden tunnistamisesta, konfiguroinnista ja vastaavista. CXL.cache-protokollaa käytetään kun väylään liitettty laite käyttää prosessorin päässä olevaa muistialuetta ja CXL.memoryä kun prosessori käyttää väylän toisessa päässä olevan laitteen muistialuetta.

Asiasta kiinnostuneille suosittelemme esimerkiksi Serve The Home -sivuston artikkelia aiheesta.

Huom! Foorumiviestistä saattaa puuttua kuvagalleria tai upotettu video.

Linkki alkuperäiseen uutiseen (io-tech.fi)

Palautelomake: Raportoi kirjoitusvirheestä

Viimeksi muokattu: