- Liittynyt

- 14.10.2016

- Viestejä

- 23 428

Intel tulee esittelemään VLSI Symposium 2025 -tapahtumassa jopa yhtiön kohtalon kysymykseksi kuvailtua Intel 18A -prosessia. Esityksestä on kuitenkin saatavilla jo nyt mehukkaita yksityiskohtia sisältävä PDF-dokumentti.

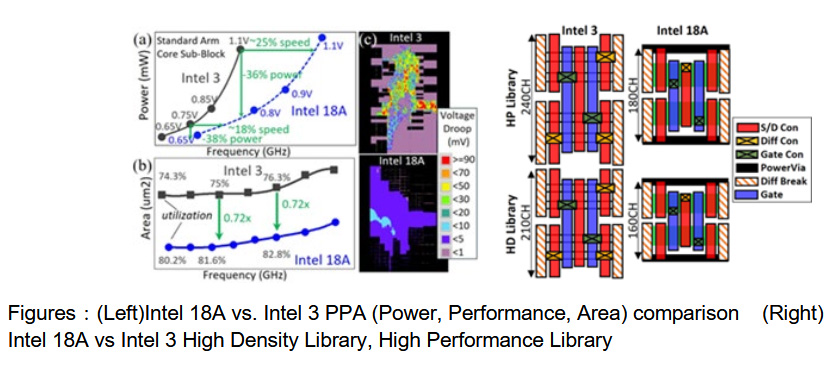

Intel 18A -prosessin merkittävimmät edistysaskeleet ovat RibbonFETeiksi kutsutut Gate-All-Around- eli GAA-transistorit sekä PowerVia-ominaisuus, joka siirtää transistorien virransyötön sirun selkäpuolelle (Backside Power Delivety Network, BSPDN). Kumpikin ominaisuuksista parantaa prosessin PPA:ta (Power, Performance and Area) eli energiatehokkuuden, suorituskyvyn ja pinta-alan suhdetta.

Intelin mukaan sen Intel 18A -valmistusprosessi tulee tarjoamaan 25 % parempaa suorituskykyä samalla 1,1 voltin jännitteellä, kuin Intel 3 -prosessi. Vaihtoehtoisesti tarjolla on myös identtiset kellotaajuudet 36 % matalammalla kulutuksella käyttäen edelleen samaa 1,1 voltin jännitettä. Vertailut on tehty standardilla Arm-ytimen lohkolla. Jos jännitettä lasketaan 0,75 volttiin, on Intel 18A yhtiön lukujen mukaan 18 % nopeampi tai kuluttaa 38 % vähemmän tehoa samalla suorituskyvyllä.

Myös transistorien koko kutistuu luonnollisesti entisestään. Siinä missä Intel 3 -prosessilla korkean suorituskyvyn HP-kirjaston solut olivat 240CH ja korkean tiheyden HD-kirjaston solut 210CH korkeita, ovat vastaavat korkeudet 180CH ja 160CH. Valitettavasti dokumentti ei tarkenna minkä mittayksikkö CH on.

Intel 18A -prosessin kerrotaan lisäksi herättäneen aidosti kiinnostusta myös asiakasyrityksissä. Samssa VLSI Symposiumissa yhtiö tulee esittelemään paperin PAM-4-lähettimen toteutuksesta Intel 18A -prosessilla BSPDN:n kera. Paperista ovat vastuussa paitsi Intelin omat insinöörit, myös piirien sopimussuunnittelijana ja IP-blokkien lisensoijana toimiva Alphawave Semi, Apple ja NVIDIA. Sekä Applen että NVIDIAn on aiemminkin huhuiltu tähyilevän myös Intelin tuotantolaitosten tarjontaa tuleville piireilleen.

Lähde: Tom’s Hardware