- Liittynyt

- 14.10.2016

- Viestejä

- 22 435

Kaotik kirjoitti uutisen/artikkelin:

Intelin ongelmat valmistusprosesseissa viime vuosina lienevät tavoittaneen jo tynnyreissäkin asuvat. Yhtiö on kuitenkin panostanut voimakkaasti aiempien ongelmien korjaamiseen ja tulevien estämiseen. Intel on asettanut tavoitteekseen saada käyttöön jopa viisi uutta prosessia neljässä vuodessa ja ainakin tähän asti suunnitelma on ilmeisesti pysynyt aikataulussaan.

Intelin nykyaikataululla vuonna 2024 tuotantoon otettava Intel 20A -prosessi tulee tuomaan mukanaan sekä RibbonFET-transistorit nykyisten FinFETtien tilalle ja samalla uuden PowerVia-teknologian. PowerVia on Intelin nimi yhtiön näkemykselle Backside Power Delivery -virtajohdotuksille (BS-PDN, Backside Power Delivery Network). Se mullistaa piisirun nykyrakenteen ja teknologiaa ollaan testattu jo nyt Intel 4 -prosessilla.

[gallery link="file" columns="2" size="medium" ids="88221,88222"]

BS-PDN on useiden muiden alan teknologioiden tapaan eurooppalaisen voittoa tavoittelemattoman IMEC:n (Interuniversity Microelectronics Centre) kehittämä teknologia. IMEC tutkii ja kehittää teknologioita puolijohdealan käyttöön vuosia ennen, kuin niitä nähdään varsinaisessa käytössä puolijohdeteollisuudessa. Intelin PowerVian merkittävin ero IMECin alkuperäiseen teknologiaan ovat NanoTSV:t (Through Silicon Via), jotka vievät virtasignaalit transistoreille läpivientien läpi suoraan transistorikerroksessa, kun IMEC reititti sen signaalipuolen alimmaisen kerroksen kautta.

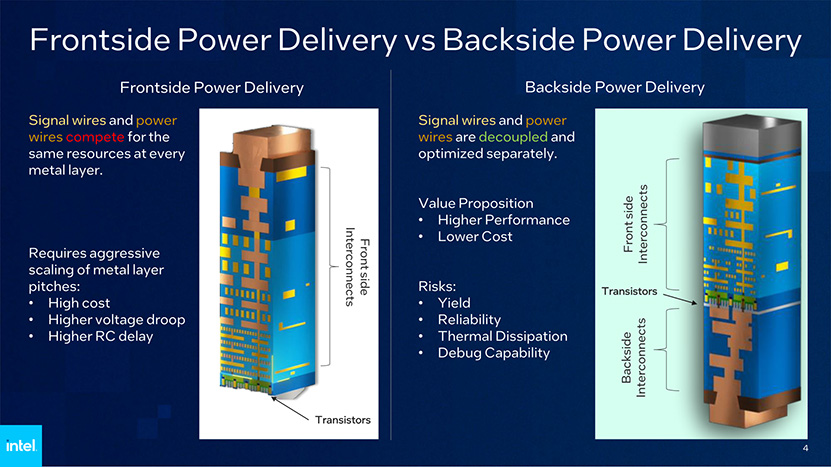

Siinä missä nykyisin transistorit ovat aivan sirun pohjalla ja sekä signaali- että virtajohdot kulkevat siihen ylhäältä, siirtää BS-PDN virranjakelun transistorin alapuolelle, jolloin signaali- ja virtajohdotukset häiritsevät toisiaan vähemmän ja niille on enemmän tilaa. Ratkaisu parantaa sekä suorituskykyä että laskee hintaa, mutta riskipuolelta löytyvät saannot, luotettavuus, lämmön poistaminen transistoreilta sekä erilaisten debug-toimintojen vaikeutuminen, kun transistoreihin ei päästä enää suoraan käsiksi.

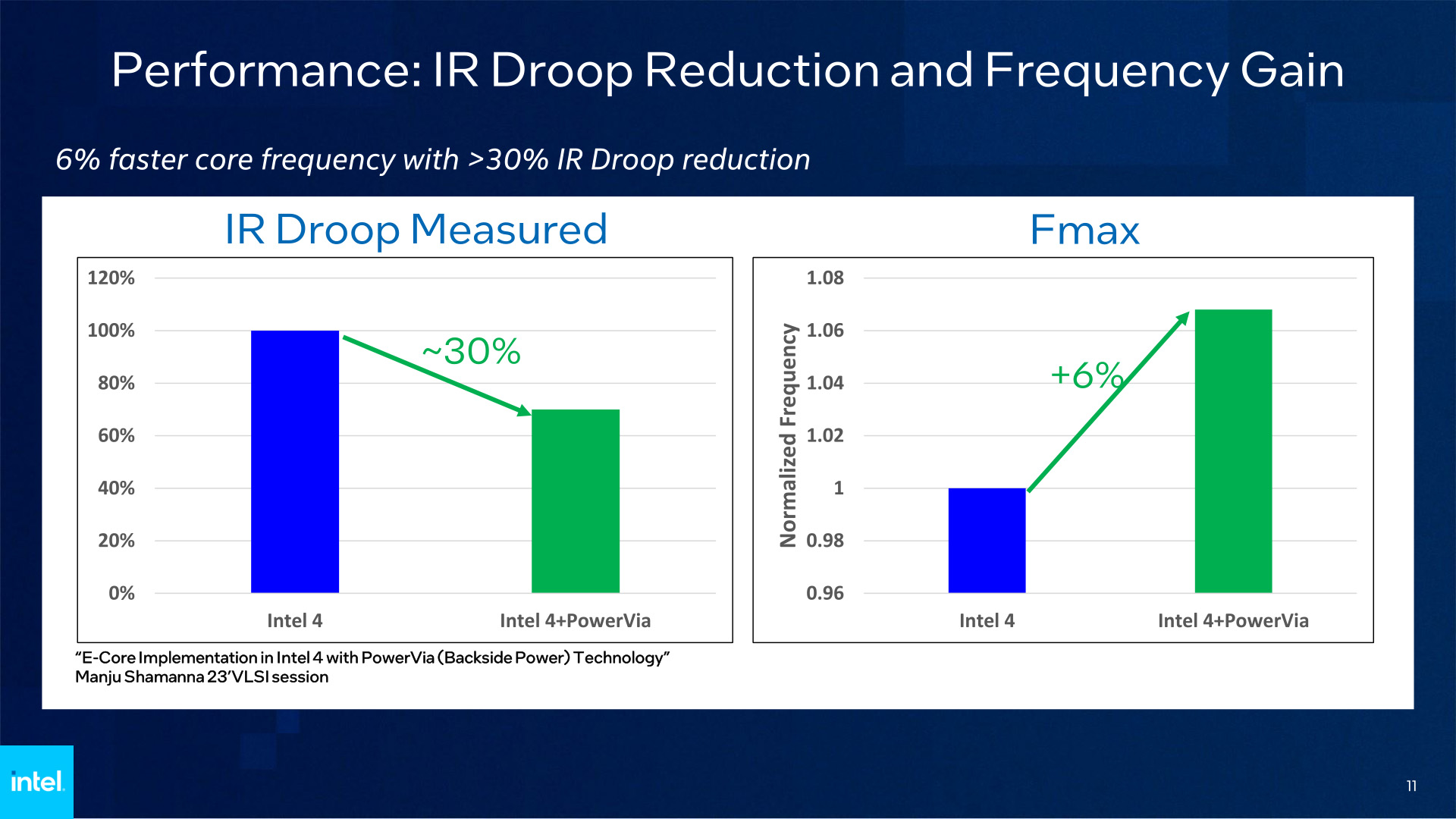

Intel 4 -prosessilla rakennetun E-ytimiin perustuvan testisirun perusteella teknologia vaikuttaa erittäin lupaavalta. IR Droop eli jännitteen lasku pieneni mittausten mukaan jopa noin 30 % verrattuna verrokkisiruun ilman PowerVia-teknologiaa. Suorituskyvyssäkin nähtiin eroa, sillä muutos mahdollisti samalla 6 % korkeammat kellotaajuudet.

Suosittelemme asiasta lähemmin kiinnostuneille AnandTechin ja Tom’s Hardwaren syväluotaavia artikkeleita aiheesta.

Lähteet: AnandTech, Tom's Hardware, IMEC

Linkki alkuperäiseen juttuun