- Liittynyt

- 14.10.2016

- Viestejä

- 24 984

Kaotik kirjoitti uutisen/artikkelin:

AMD piti aiemmin tällä viikolla Financial Analyst Day 2020 -tapahtuman, jossa se kertoi yhtiön lähitulevaisuuden suunnitelmista. Jo uutisoitujen näytönohjainrintaman kuulumisten lisäksi AMD kertoi tapahtumassa muun muassa prosessoreiden lähitulevaisuudesta ja paketointiteknologioista.

[gallery link="file" columns="2" size="medium" ids="44691,44690"]

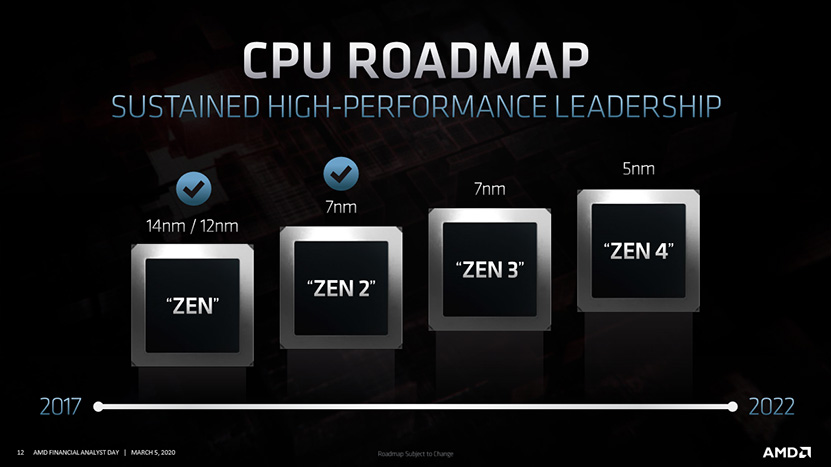

Prosessoripuolella AMD julkaisi uuden suurpiirteisen arkkitehtuuri-roadmapin, joka sisältää nyt neljä Zen-sukupolvea ja aikajanan vuodesta 2017 vuoteen 2020, mutta tarkkoja tulkintoja arkkitehtuurien julkaisuajankohdista siitä ei voi vetää. Joukon tuorein tulokas, Zen 4, tullaan valmistamaan 5 nanometrin valmistusprosessilla. Roadmapin Epyc-versiossa ei ollut varsinaisesti uutta tietoa, sillä AMD on jo aiemmin varmistanut Zen 3 Epycin olevan Milan ja Zen 4 Epycin Genoa.

Näytönohjaindiojen tapaan AMD on poistanut ”7nm+” merkinnän ja korvannut sen pelkällä ”7nm”:llä. AnandTechin saaman vastauksen mukaan merkintä poistettiin, koska se yhdistettiin liian yleisesti TSMC:n N7+ EUV -prosessiin, vaikka sen oli tarkoitus esittää vain parempaa 7 nanometrin prosessia. AMD ei tässä vaiheessa paljasta, millä prosessilla esimerkiksi Zen 3 -prosessorit tullaan valmistamaan. Yhtiön nykyisistä tuotteista ainakin Navi 10 -grafiikkapiirit on valmistettu 2. sukupolven 7 nanometrin eli N7P-prosessilla.

Kuluttajapuolella prosessori-roadmap ei ole päivittynyt vielä yhtä pitkälle, kuin Epyc-puolella. Prosessori-roadmapin aikajana yltää vuoteen 2021 asti, jolloin julkaistaan Zen 3 -arkkitehtuuriin perustuvat Vermeer-koodinimelliset 4. sukupolven Ryzen-prosessorit. Vermeer-koodinimelliset Zen 3 -prosessorit tullaan valmistamaan tarkemmin määrittelemättömällä 7 nanometrin valmistusprosessilla.

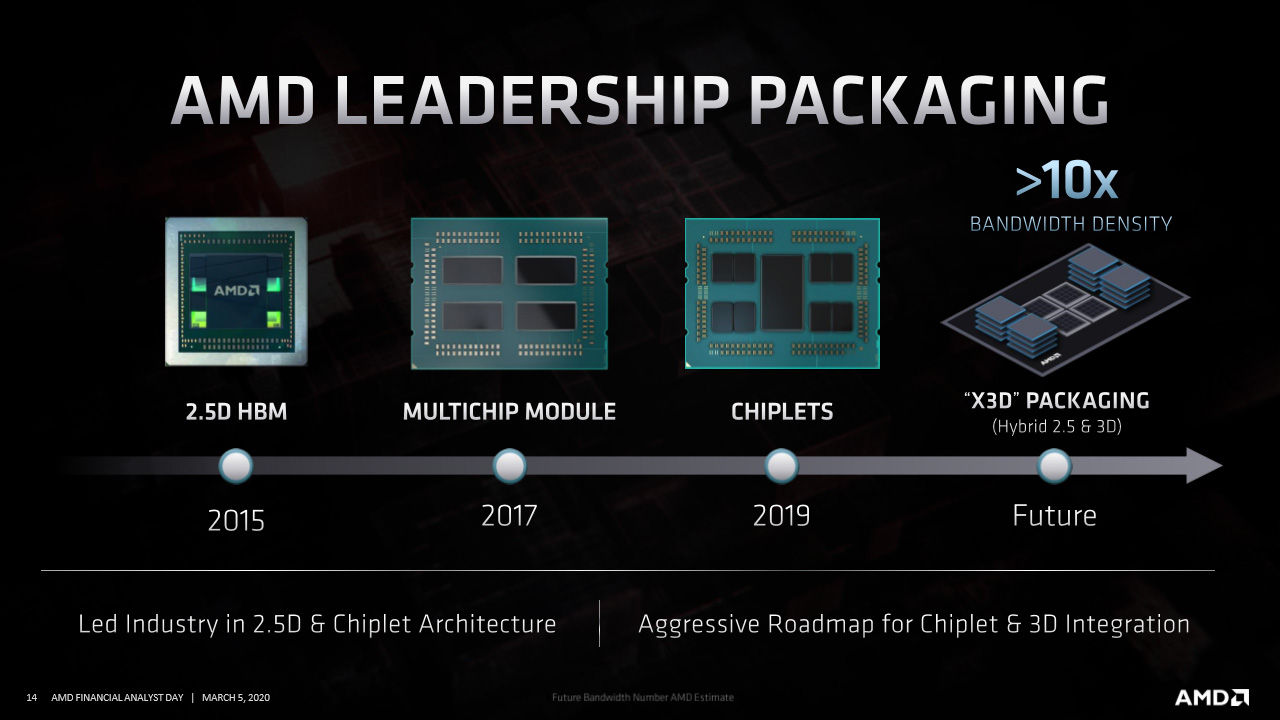

Paketointipuolella AMD:n tulevaisuudensuunnitelmiin kuuluu ainakin X3D:ksi toistaiseksi ristitty teknologia, joka yhdistää 2,5D- ja 3D-teknologiat yhteen paketointiin. Esimerkkikuvassa yhden interposerin päällä on neljä sirua sekä neljä muistipinoa ja sen luvataan mahdollistavan yli kymmenkertaisen kaistan perinteiseen paketointiin nähden samassa tilassa. AMD ei vielä paljastanut edes summittaista aikataulua X3D-paketoinnin käyttöönotolle, vaan totesi sen yksinkertaisesti olevan tulossa käyttöön tulevaisuudessa.

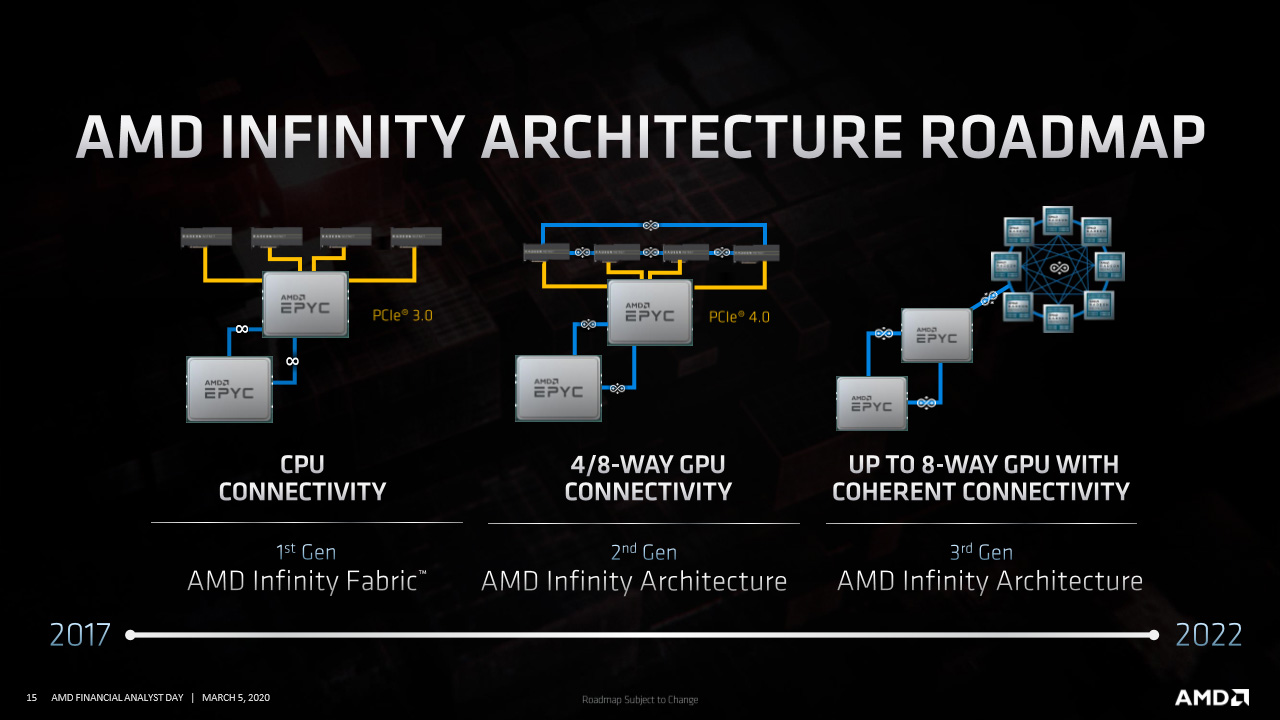

Väyläteknologioissa AMD on ristinnyt Infinity Fabric -väylän yleisesti Infinity-arkkitehtuuriksi. Nykyisellään Infinity-arkkitehtuurin ensimmäisessä sukupolvessa prosessoreiden välillä on IF-linkki, mutta laskentakorteille kommunikoidaan PCIe 3.0 -väyliä pitkin. Toisen sukupolven Infinity-arkkitehtuurilla prosessori ja laskentakortit keskustelevat PCIe 4.0 -väylää pitkin ja laskentakortit keskenään IF-linkkejä pitkin. Kolmannen sukupolven Infinity-arkkitehtuurissa myös prosessoreiden ja laskentakorttien välinen linkki päivittyy IF-aikaan, mikä nostaa väylän nopeuden yli kaksinkertaiseksi ja mahdollistaa koherentin muistiavaruuden prosessoreiden ja laskentakorttien välille. 3. sukupolven Infinity-arkkitehtuuria tullaan käyttämään ainakin El Capitan -supertietokoneessa siten, että kukin Epyc-prosessori on kytköksissä neljään laskentakorttiin, vaikka väylä mahdollistaisi useammankin.

Linkki alkuperäiseen juttuun