- Liittynyt

- 14.10.2016

- Viestejä

- 24 989

Kaotik kirjoitti uutisen/artikkelin:

ISSCC2023 eli International Solid-State Circuits Conference 2023 -tapahtuma pidettiin viime kuun lopulla. Tapahtuma on suunnattu alan toimijoille, jonka vuoksi tapahtuman medianäkyvyys on yleensä pientä.

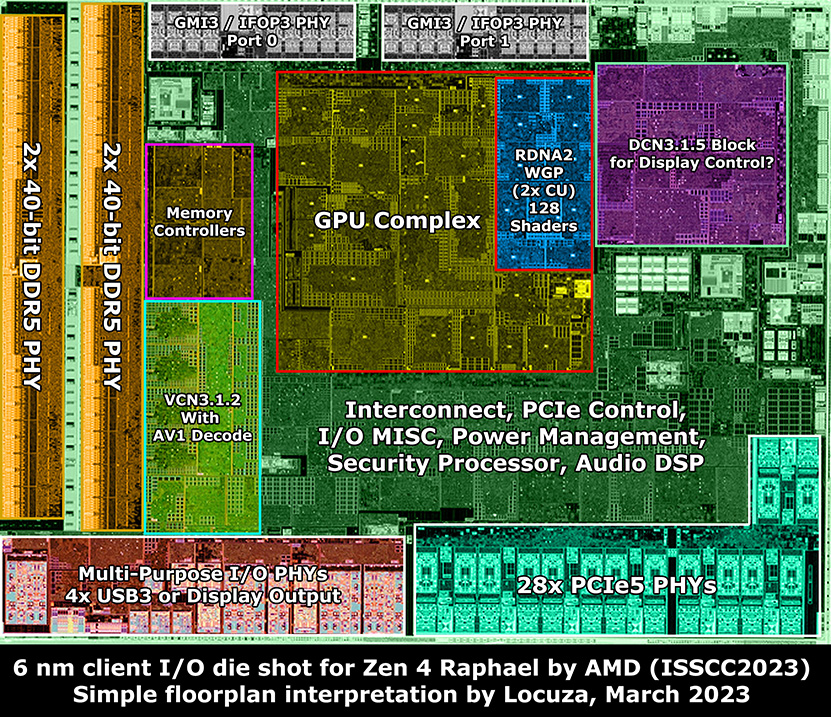

Twitteristä tuttu Locuza on saanut käsiinsä AMD:n tapahtumassa julkaiseman kuvan Raphael-prosessorin I/O-sirusta, kiitos korealaisen Li Jae-Yeonin, joka oli puolestaan kaivanut sen ISSCC:n virallisista dioista. Raphaelin I/O-siru valmistetaan TSMC:n 6 nanometrin luokan N6-perheen prosessilla, kun Zen 4 -prosessorisirut valmistetaan 5 nm luokan N5-perheen prosessilla. X3D-prosessoreiden 3D V-Cache -välimuisti valmistetaan TSMC:n 7 nanometrin luokan N7-perheen prosessilla.

Locuza on aiemminkin niittänyt mainetta nimenomaan merkitsemällä sirujen kuviin eri osien funktioita, eikä tuota tälläkään kertaa pettymystä. I/O-sirusta on eritelty neljä 40-bittistä DDR5-PHY-liitäntää (fyysinen kerros), muistiohjaimet, VCN 3.1.2 -mediayksikkö, integroitu RDNA2 grafiikkaohjain ja sen sisältä yksi kahdesta Compute Unit -yksiköstä rakentuva WGP, näyttöohjain sekä joukko PHY-liitäntöjä. Joitain tunnistamattomiakin alueita piirille on toki jäänyt, jotta oman elämänsä tutkijatkin saavat oman viihteensä. Uutena mukaan lykätty RDNA2 iGPU vie sirun pinta-alasta noin 16 %. Kaksi GMI-linkkiä puolestaan varmistaa, ettei I/O-siruun voi liittää kuin kaksi prosessori- tai muuta sirua.

[gallery link="file" columns="2" size="medium" ids="85252,85253"]

Myös Tom’s Hardware on hankkinut käsiinsä ISSCC2023-tapahtuman materiaaleja sekä järjestäjältä että suoraan AMD:lta. Tapahtumassa on esitelty lähemmin muun muassa välimuistimuutoksia. Uuden pienemmän prosessorisirun myötä AMD on joutunut laajentamaan 3D V-Cachen vaatimia läpivientejä L2-välimuistin puolelle, tosin vain virransyöttöläpivientien osalta.

3D V-Cache on omalta osaltaan myös aikamoinen taidonnäyte. Vaikka käytössä on samat noin 4,7 miljardia transistoria ja 7 nanometrin luokan prosessi, on AMD onnistunut tiivistämään sirun 41 mm2:sta 36 mm2:een. Transistoritiheydessä laskettuna ensimmäisen sukupolven välimuistisirussa oli noin 114,6 miljoonaa transistoria neliömilliä kohden, kun uudessa sukupolvessa päästään jopa 130,6 miljoonaan transistoriin per mm2. Sekä uusi että vanha välimuistisiru ovat vanhemmasta prosessistaan huolimatta myös selvästi Zen 4 -prosessorisirua tiiviimpiä. Prosessorisiru yltää 5 nanometrin luokan prosessistaan huolimatta vain noin 99 miljoonaan transistoriin per neliömilli. Raphaelin 6 nanometrin luokan I/O-sirun transistoritiheys on vaivaiset 28,6 miljoonaa transistoria per mm2.

Lähde: Tom's Hardware

Linkki alkuperäiseen juttuun