- Liittynyt

- 14.10.2016

- Viestejä

- 21 543

Kaotik kirjoitti uutisen/artikkelin:

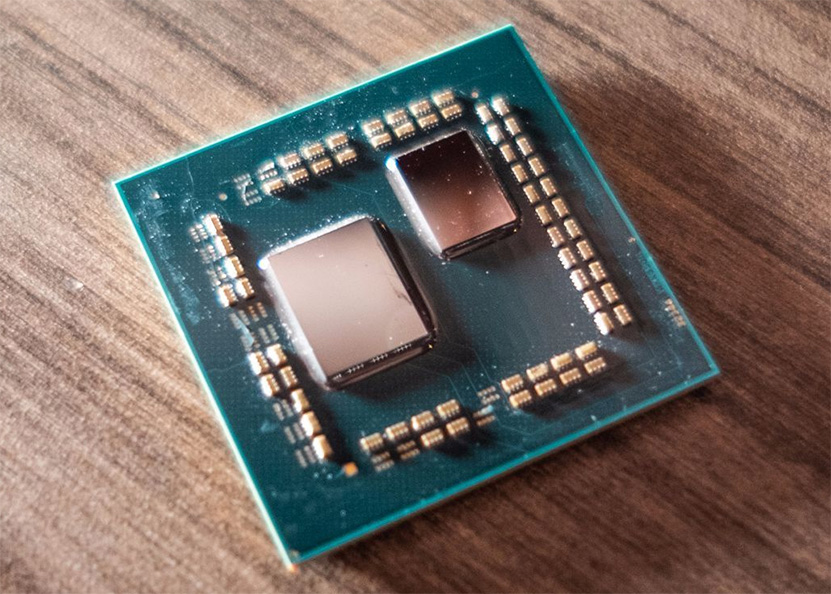

Intelin prosessorit ovat saaneet viime vuosina ryöpytystä tietoturvaongelmistaan, mutta tällä kertaa on AMD:n vuoro. Grazin teknillisen yliopiston tutkijat ovat onnistuneet takaisinmallintamaan AMD:n L1D-välimuistin ennustajayksikön ja hyödyntämään sen kautta saatua tietoja muiden haavoittuvuuksien kanssa.

”Take A Way”:ksi ristitty hyökkäys sisältää todellisuudessa kaksi erillistä hyökkäystä, Collide+Proben ja Load+Reloadin. Haavoittuvuus koskee kaikkia AMD:n Bulldozer- ja Zen-johdannaisia arkkitehtuureita. Haavoittuvuudet on testattu toimiviksi myös laboratorion ulkopuolelle Epyc-pilvipalvelimissa hyödyntämällä JavaScriptiä Chrome- ja Firefox-selaimilla.

Tutkijoiden mukaan takaisinmallintamalla L1D-välimuistin ennustajan (L1D cache way predictor). Saatujen tietojen perusteella toteutettu Collide+Probe-hyökkäys mahdollistaa muistihakujen tarkkailun ilman, että hyökkääjän tarvitsisi tietää tarkkailtavaa muistiosoitetta, kun kaksi prosessia käyttää samaa ydintä. Load+Reload puolestaan mahdollistaa ennustajan hyödyntämisen paljastamaan, onko samaa ydintä käyttävä prosessi käyttänyt tiettyjä muistiosoitteita.

Kehittäjien mukaan Take A Way vuotaa kutienkin vain pieniä määriä metadataa, eikä siten ole verrattavissa esimerkiksi Spectre- ja Meltdown-hyökkäyksiin. AMD puolestaan on kommentoinut Tom’s Hardwarelle, että se ei varsinaisesti laskisi näitä uusiksi hyökkäyksiksi, mutta ei kiellä haavoittuvuuden olemassaoloa. Yhtiö ei ole kertonut vielä, miten se tulee korjaamaan asian, mutta tutkijoiden mukaan erilaisia korjaustapoja olisi sekä rauta- että ohjelmistopohjaisesti olemassa useita.

Netissä nousi myös pienoinen kohu, kun tutkijoiden huomattiin saavan osan rahoituksestaan Inteliltä. Samat tutkijat ovat kuitenkin julkaisseet myös useita Inteliä koskevia haavoittuvuuksia, eikä mikään tapauksessa anna syytä epäillä rahoituksen vaikuttaneen tutkimukseen tai että Intel olisi kehottanut tutkimaan asiaa.

Lähde: Tom's Hardware

Linkki alkuperäiseen juttuun