- Liittynyt

- 14.10.2016

- Viestejä

- 24 940

Kaotik kirjoitti uutisen/artikkelin:

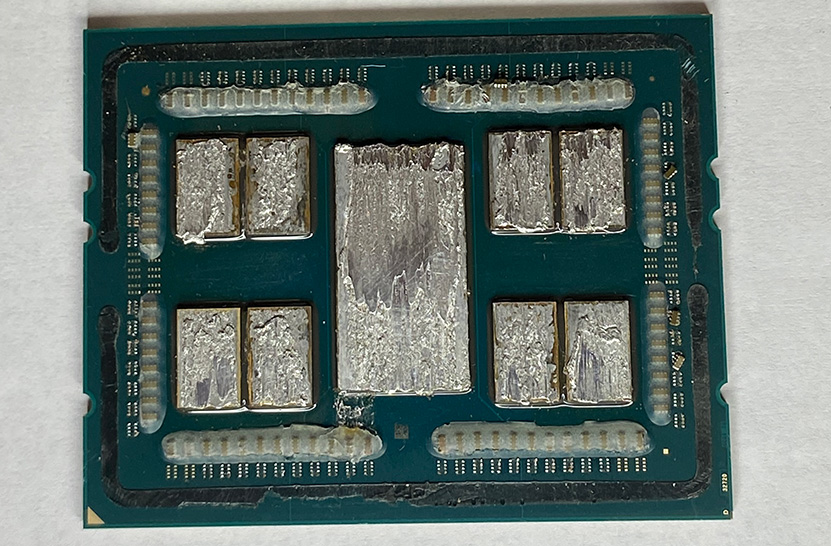

AMD on tuonut tänä keväänä myyntiin ensimmäiset 3D V-Cache -välimuistilla varustetut prosessorit. Yhtiö on esitellyt pinottavaa välimuistiarkkitehtuuriaan useissa dioissa, mutta nyt toteutusta on päästy katselemaan myös lähemmin käytännössä.

3D V-Cachen ensiesiintymisestä ehti vierähtää liki vuosi, ennen kuin prosessorit vihdoin saapuivat markkinoille. Myös itse prosessoreiden ja pinottavan välimuistisirun toteutus on ehtinyt muuttumaan matkan varrella melkoisesti.

[gallery link="file" ids="74485,74484,74482"]

Kun toimitusjohtaja Lisa Su esitteli prototyyppiprosessoria 3D V-Cachella ensimmäistä kertaa, oli välimuistisiru selvästi erotettavissa prosessorista ja täytepiistä. AMD:n diojen mukaan asiassa ei ollut mitään erikoista, sillä rakenne vastasi diojen kuvausta, vaikka niissäkin oli esiintynyt ainakin kahdenlaisia pii”shimmejä” välimuistisirun ympärille. Poikkeuksen tähän tekee yksi tietty ISSCC:ssä esitetty dia, jossa myös välimuistisirun päällä on kerros piitä tukemassa rakennetta.

[gallery link="file" columns="2" size="medium" ids="74483,74487"]

Puolijohteiden paketointiteknologioiden parissa työskentelevä Tom Wassick on saanut käsiinsä Epyc 7473X -prosessorin, eli Milan-X-koodinimellisen Epycin 3D V-Cache -välimuistilla. Wassick korkkasi prosessorin nopeasti ja selvitti mikä lopullisten prosessoreiden todellinen rakenne on. Korkkauksen jäljiltä oli selvää, että ISSCC:n dian kuvaus pitää paikkansa, aiemmat AMD:n diat eivät; välimuistisirun päällä on vielä yksi piikerros tukemassa rakennetta. Wassick aikoo jatkaa prosessorin paloittelua selvittääkseen tarkemmin sirun rakenteen ”kannen” alla. Kuten kuvista näkee, paketoinnin rakenteen selvittämisen jälkeen Wassickin Milan X -prosessorista on enää turha odottaa soivaa peliä.

Lähde: Tom's Hardware, Tom Wassick @ Twitter

Linkki alkuperäiseen juttuun

. Lisäkerros varmaan aiheuttaa lisää haasteita lämpöjen kanssa.

. Lisäkerros varmaan aiheuttaa lisää haasteita lämpöjen kanssa.