- Liittynyt

- 22.10.2016

- Viestejä

- 11 123

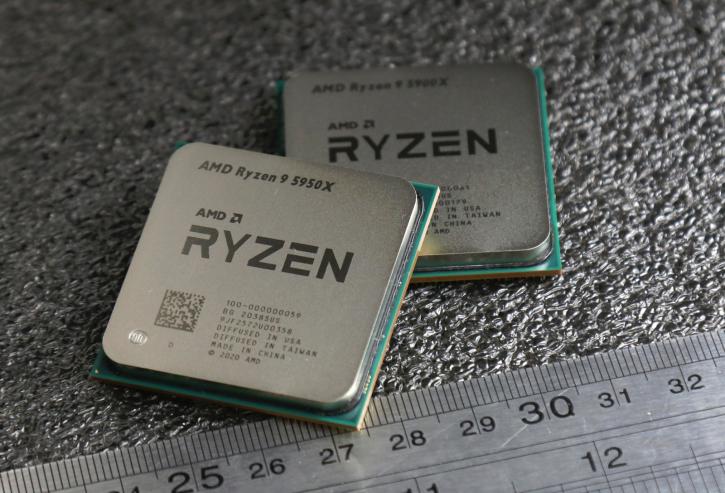

Ei tuohon ole mahdollista tehdä mitään "korjausta" muutoin kuin kytkemällä kyseinen ominaisuus pois päältä, mikä huonontaa suorituskykyä.Merkitään Zen 4 spekulaatioon, että siinä ehkä korjataan Zen kolmosesta löytynyt Spectre V4 kaltainen aukko. Jota ei löydy zen 1/+/2, ja jota ei luultavasti kolmoseen paikata suorituskykyongelman ja pienen riskin takia.

AMD's Zen 3 CPUs Are Susceptible To Spectre-Like Vulnerability (Updated)

Zen 3's weak spotwww.tomshardware.com

Aina kun ennustetaan jotain, ennustus voi mennä pieleen. Se hanskataan oikein arkkitehtuurillisessa tilassa, mutta siitä jää aina jotain sivuvaikutuksia.

Ja tämän poiskytkeminen on jo mahdollista zen3lla.

Ja ottaen huomioon kuinka pieni riski on siihen, että tätä voidaan käyttää johonkin oikeasti käytännössä haitalliseen, se tullee zen4llakin olemaan oletuksena päällä.