AMD 3rd Gen Ryzen Threadripper CPUs To Get New Socket & Chipset

Huhun mukaan seuraava Threadripper ei olisikaan TR4-kantayhteensopiva.

Huhun mukaan seuraava Threadripper ei olisikaan TR4-kantayhteensopiva.

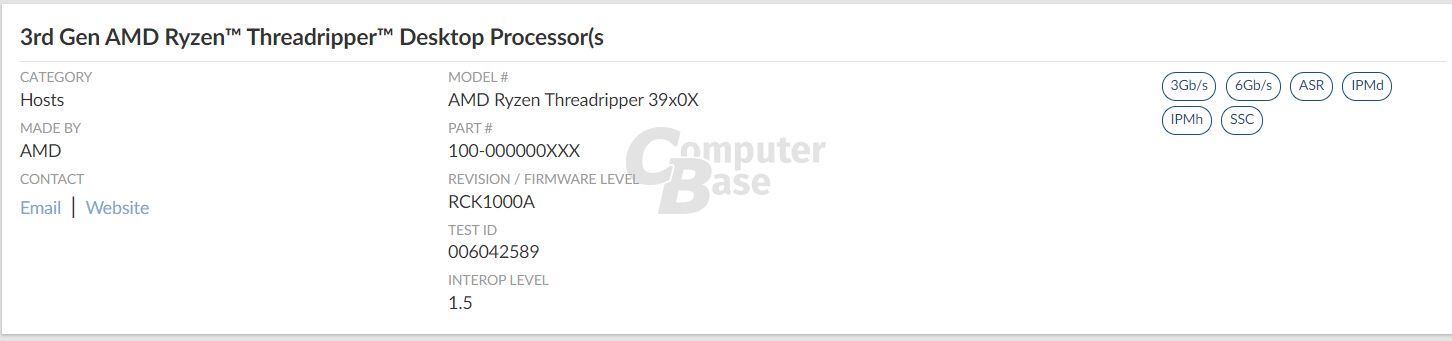

1usmus lähteenä. Ryzen DRAM Calculatorin kehittäjä. Tykkää aukoa suutaan ilmeisesti kans. Eikös EPYC Romet (Zen 2) mene samalle kannalle kuin EPYC Naples (Zen 1)? Onko siinä sitten jotain järkeä, että TR4 ei enää käykään?AMD 3rd Gen Ryzen Threadripper CPUs To Get New Socket & Chipset

Huhun mukaan seuraava Threadripper ei olisikaan TR4-kantayhteensopiva.

Tuostahan tuli huhuja, että tulevassa Threadripperissä olisi mahdollista saada aiempaa enemmän muistikanavia käyttöön. Kuvittelisi sen tarvitsevan muutoksia emoihin jos se siis pitää edes paikkaansa.AMD 3rd Gen Ryzen Threadripper CPUs To Get New Socket & Chipset

Huhun mukaan seuraava Threadripper ei olisikaan TR4-kantayhteensopiva.

Joo toi kaveri kyllä louskuttaa leukojaan jatkuvasti, menny kyllä täysin kaverin uskottavuus. Johan tuo tuossa kuumimman bios sohlauksen aikaan oli amd:n työntekijä ja kaikkee.1usmus lähteenä. Ryzen DRAM Calculatorin kehittäjä. Tykkää aukoa suutaan ilmeisesti kans. Eikös EPYC Romet (Zen 2) mene samalle kannalle kuin EPYC Naples (Zen 1)? Onko siinä sitten jotain järkeä, että TR4 ei enää käykään?

Ottamatta kantaa siihen, onko todennäköistä, niin olisi järkevää riippumatta siitä, montako muistikanavaa siihen tulee.AMD 3rd Gen Ryzen Threadripper CPUs To Get New Socket & Chipset

Huhun mukaan seuraava Threadripper ei olisikaan TR4-kantayhteensopiva.

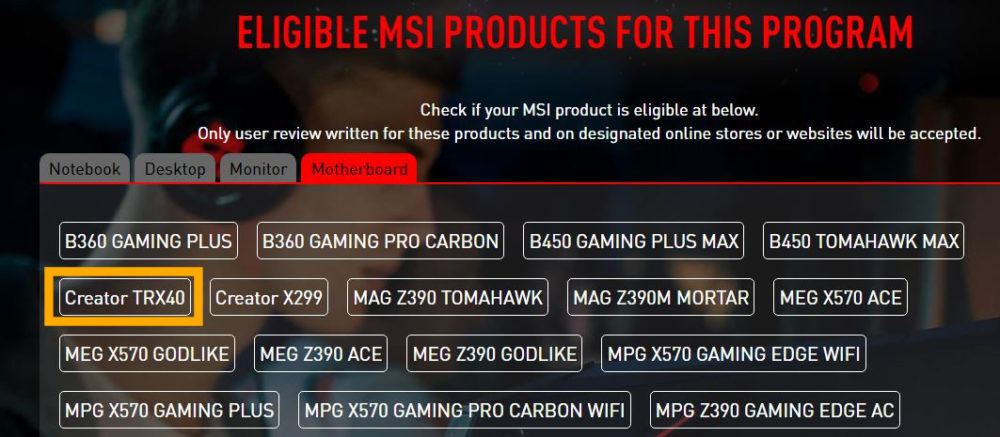

Ei sillä kannalla ole nykyään (juuri) mitään tekemistä "piirisarjan" kanssa. Oikeastaan koko "piirisarja" on täysin vanhentunut käsite, kun puolet siitä piirisarjasta löytyy prosessorin kanssa samasta paketista ja toinen puoli on optionaalinen.Itse uskon, että TRX40 tarjoaa kantayhteensopivuuden vanhoille Threadrippereille (4x muistikanavat, 2dimm / kanava).

TRX80 voisi olla 1 CPU versio 8x muistikanavalla (ehkä rajoitettu 1 dimm/kanava) ja WRX80 taas 2 CPU 8x muistikanavalla/CPU (2 dimm/kanava).

Jos Threadrippereiden piirisarjoissa mennään joissakin versioissa 8x muistikanaviin, niin suurella todennäköisyydellä aivan samat piirisarjat ovat käytössä myös EPYCeissä (ehkä joillakin konfigurointivaihtoehdoilla eroteltuina).

Tämä ei ole videofoorumi, joten pistäppä yhteenvetoa tuloksista.Siinä olisi Epyc 64 coren testiä Linus Tech Tips toimesta.

Kauhian nopia!Tämä ei ole videofoorumi, joten pistäppä yhteenvetoa tuloksista.

Missään ei ole tainnut olla mainintaa, että videoita ei voisi laittaa mikä on aiheeseen liittyvä, joten katso mikäli kiinnostaa. Minulla ei ole aikaa alkaa tekemään mitään yhteenvetoja sinulle aiheesta.Tämä ei ole videofoorumi, joten pistäppä yhteenvetoa tuloksista.

Pelisääntöihin kuitenkin kuuluu että jos linkataan video niin sitten ainakin lyhyt yhteenveto sisällöstä mukaan.Missään ei ole tainnut olla mainintaa, että videoita ei voisi laittaa mikä on aiheeseen liittyvä, joten katso mikäli kiinnostaa. Minulla ei ole aikaa alkaa tekemään mitään yhteenvetoja sinulle aiheesta.

Mikäänhän ei kiellä että ZEN3 olisi myös ensimmäinen DDR5 prossu koska coret ei sisällä muistiohjainta. Alkuperäisissä suunnitelmissahan tuo oli niin että ZEN3 asti tulee AM4 kannalle joka on DDR4:llä.

Jotta semmoista, ZEN3 vaikuttaisi olevan siis DDR4, PCIe 4.0, SMT2 ja 8core/CCX

Juu toki ei, ainakaan teoriassa.Mikäänhän ei kiellä että ZEN3 olisi myös ensimmäinen DDR5 prossu koska coret ei sisällä muistiohjainta. Alkuperäisissä suunnitelmissahan tuo oli niin että ZEN3 asti tulee AM4 kannalle joka on DDR4:llä.

korjasin kuvan

Jotta semmoista, ZEN3 vaikuttaisi olevan siis DDR4, PCIe 4.0, SMT2 ja 8core/CCX

Nythän se ei näy ollenkaan?korjasin kuvan

Jaa, itsellä alkoi näkyä kun otti s pois? Aiemmin ei näkynyt.Nythän se ei näy ollenkaan?

Tuossa roadmapissahan lukee Milanin (Zen 3) kohdalla että DDR4. Tuskin desktop-puolella otetaan uutta muistitekniikkaa käyttöön aiemmin kuin serveripuolella. Se on sitten eri asia, että kun DDR5:tä tukevia prosessoreja tulee myyntiin joskus 2021, niin tuleeko silloin myös vanhempia Ryzen-malleja uudelle kannalle uudella muistiohjaimella. Silloinkin veikkaisin, että uuden sukupolven prosessorit julkaistaan ensin.Mikäänhän ei kiellä että ZEN3 olisi myös ensimmäinen DDR5 prossu koska coret ei sisällä muistiohjainta. Alkuperäisissä suunnitelmissahan tuo oli niin että ZEN3 asti tulee AM4 kannalle joka on DDR4:llä.

Juu Milan on kyllä ZEN3 + DDR4 mutta mikään ei tosiaan kiellä että sieltä ei tulis joku Bologna joka on ZEN3 + DDR5Tuossa roadmapissahan lukee Milanin (Zen 3) kohdalla että DDR4. Tuskin desktop-puolella otetaan uutta muistitekniikkaa käyttöön aiemmin kuin serveripuolella. Se on sitten eri asia, että kun DDR5:tä tukevia prosessoreja tulee myyntiin joskus 2021, niin tuleeko silloin myös vanhempia Ryzen-malleja uudelle kannalle uudella muistiohjaimella. Silloinkin veikkaisin, että uuden sukupolven prosessorit julkaistaan ensin.

Jooh eli merkittävin muutos on toi chipletin L3. Vai menisköhän chipletin rakenne muutenkin uusiksi että ei olis enää 2*4-core ccx?

Jotta semmoista, ZEN3 vaikuttaisi olevan siis DDR4, PCIe 4.0, SMT2 ja 8core/CCX

Video poistettu... Vaihdathan youtubelinkin toimivaan, jos löydät?

Jotta semmoista, ZEN3 vaikuttaisi olevan siis DDR4, PCIe 4.0, SMT2 ja 8core/CCX

Arvasin että se poistetaan koska siinä komeili AMD confidental ja parissa kohdassa puhuttiin julkaisemattomasta tuotteesta.Video poistettu... Vaihdathan youtubelinkin toimivaan, jos löydät?

Koko CCXn "määritelmä" on että se on joukko ytimiä joilla on yhteinen L3-välimuisti.Jooh eli merkittävin muutos on toi chipletin L3. Vai menisköhän chipletin rakenne muutenkin uusiksi että ei olis enää 2*4-core ccx?

Ja yksi CCD eli Core Complex Die on ollut ennen 2x CCXKoko CCXn "määritelmä" on että se on joukko ytimiä joilla on yhteinen L3-välimuisti.

Eli siis, CCXn koko tuplattu neljsätä kahdeksaan ytimeen, ja yhdellä chipletillä on zen3ssa yksi CCX.

Noissa Ryzeneissä on itseasiassa erilliset L3 muistit jokaiselle ytimelleKoko CCXn "määritelmä" on että se on joukko ytimiä joilla on yhteinen L3-välimuisti.

Eli siis, CCXn koko tuplattu neljsätä kahdeksaan ytimeen, ja yhdellä chipletillä on zen3ssa yksi CCX.

Ei ole.Noissa Ryzeneissä on itseasiassa erilliset L3 muistit jokaiselle ytimelle

Jokaisesta L3 cachesta on suora yhteys muiden ydinten L3 muisteille

Tästä kuvasta näkyy ainoastaan välimuistilohkojen paikat, ei yhtään sitä miten mikäkin on kytketty.

wikichip sanoi:Every core can access every L3 cache slice with the same average latency.

Ei siellä ole mitään kalvostoa. Eikä siellä ole sen järjestelyssä mitään ihmeellistä; CCXn kokoa vaan kasvatettu, mikä toki tarkoittaa sitä, että CCXn sisäinen kytkentäverkko on kasvanut selvästi, eli siellä on joko paljon entistä suurempi crossbar, tai sitten se crossbar on ehkä korvattu esim. omega-verkolla jotta siitä ei tulisi liian hidas ja virtasyöppö koon kasvaessaSe miten noissa Milan prossuissa tuo L3 on järjestelty on uutta ja ihmeellistä , mutta

Todella isoa tekniikkaa löytynee tuolta IO-die kalvostosta , se on todennäköisesti mennyt täysin uusiksi ja kertaluokkaa ihmeellisemmäksi

Erohan tuli Intelillä jossain Nehalem-Sandy-Brigde välillä eli yhden yhteisen L3:n sijasta L3:sta tehtiin sliceja, joka ytimelle yksi, sama L3 kontrolleri vastaa oman ytimensä liikenteestä ja omasta cache-slicestään. Kaikki osoitteet on hashattu kaikkien slicejen kesken mutta tuskin AMD:kään olisi niin idiootti että muistiosoitteet häshättäisiin niin että joka muistihausssa jokainen slice jouduttaisiin tarkistamaan. Itseasiassa AMD kertoo että low-order bitit määräävät mihin cache-sliceen muistiosoite ohjataan, eli muistihaut ohjataan siihen sliceen josta se mahdollisesti löytyy.Ei ole.

Kaikki L3-välimuisti toimii L3-välimuistina CCxn kaikille ytimille, ei ole mitään "ydinten omia L3-välimuisteja". Kun ydin tekee muistiaccessin josta tulee L2-huti, kaikki oman CCXn L3n välimuistin wayt tarkastetaan (rinnakkain), riippumatta siitä, kuinka lähellä mitäkin CCXn ydintä mikäkin way fyysisesti sijaitsee.

Se välimuisti on vaan zeppelinässä kahdeksassa osassa (joista jokaisessa on kaksi waytä) joten kaksi osaa vaan sattuu sijaitsemaan aina fyysisesti lähempänä yhtä ydintä. (ja raven ridgessä neljässä osassa, siten että aina yksi neljästä osasta on fyysisesti lähimpänä kutakin ydintä).

ok, eli ei olekaan kaksi waytä/slice, eli siinä olin väärässä, vaan tietty osa jokaisesta waystä on jokaisessa slicessä.Itseasiassa AMD kertoo että low-order bitit määräävät mihin cache-sliceen muistiosoite ohjataan, eli muistihaut ohjataan siihen sliceen josta se mahdollisesti löytyy.

Mikään "olisi ringissä" ei vaan selitä noita viivelukuja tuolla, kun niitä tarkastelee tarkemmin....mutta sekventiaalinen luenta antaa eri tuloksen, tulokset on ihan kuin AMD:kin slicet olisi ringissä.(Mikä sinällään olisi aika loogista, selvitään kahdella portilla per slice sen sijaan että niitä tungettaisiin neljä.....)

Se nimenomaan ei ole missään ytimellä, vaan se on siellä slicen keskellä se L3-välimuistiohjain.Ja siis sekä AMD:llä että Intelillä L3 cache on yhtä monessa osassa kuin on ytimiäkin, joka ytimellä on oma cache-ohjain joka vastaa omasta cachestaan ja muiden cache-ohjainten pyynnöt kulkevat sen kautta.

.png/700px-amd_zen_ccx_2_(annotated).png)

Tämä olisi aika suoritus AMD:ltä ja käytännössä sitten olisi 20-25% enemmän suorituskykyä samoilla kelloilla kuin 2000-sarjan Ryzeneillä. Ja kellojakin olisi enemmän.

öö? Millä matematiikalla saat jotain 20-25% parannuksia?Tämä olisi aika suoritus AMD:ltä ja käytännössä sitten olisi 20-25% enemmän suorituskykyä samoilla kelloilla kuin 2000-sarjan Ryzeneillä. Ja kellojakin olisi enemmän.

Uskon, kun näen. Ei tämä toki mahdotonta ole, mutta ensin leikitään maansiirtokoneiden kanssa 5 vuotta ja sitten yhtäkkiä ollaankin kehityksen aallonharja..

1.15*[1.05, 1.08]öö? Millä matematiikalla saat jotain 20-25% parannuksia?

Eikun hups, en huomannut että vertasit 2000-sarjaan eikä 3000-sarjaan.1.15*[1.05, 1.08]

Tässä on kuitenkin kahden generaation parannukset minun laskuissani. Kun itsellä on tuo 2700X..

Tuossahan ei sanota mistä se IPC parannus tulee. Zen+:ssa AMD sai "+3%" (suuri vaihtelu) pelkästään kiristämällä välimuistien latensseja sille tasolle jolla ne piti olla jo Zenissä. Välimuistia (tai välimuisteja?) muuttamalla "+5-8%" (suuri vaihtelu tässäkin) ei olisi mikään suuri ihme.Zen 3 IPC Gains Are 'Greater' Than 8 Percent - EXCLUSIVE

Insider-Gerüchte: Intel streicht 10-nm-Pläne für den Desktop komplett - Hardwareluxx

Kyseiset huhut tulivat äsken vastaan.

Elikkäs Redgamingtechillä on joku "erittäin luotettava lähde" ja kyseinen lähde on myös ollut aiemmin luotettava mitä tulee Zen 2 vuotoihin. Hän sanoo, että Zen 3 olisi huomattavasti tehokkaampi kuin Zen 2 ja siinä olisi 5-8% IPC parannus ja samalla 100-200Hz korkeammat kellot johtuen paremmasta 7Nm+ valmituksesta johtuen. Varauduksella suhtaudun tietysti näihin vuotoihin, mutta voihan tuo IPC lisä pitää paikkansakkin, kerta noita L3 muisteja uudelleen järjestelevät. Huomioiden myös sen, että vuoden vaihteen CES-messut myös lähestyvät ja siellä voisi myös olla jonkunsortin demoa tulevista Ryzen 4xxx tuotteista.

Löysät on vaan jo otettu pois. Kaikessa on tradeoffinsa (paitsi zen1n L2-välimuistissa, koska siinä se oli hidas vaan sen takia ettei sitä oltu ehditty verifioida ja sitä ajettiin "liian löysillä asetuksilla")Tuossahan ei sanota mistä se IPC parannus tulee. Zen+:ssa AMD sai "+3%" (suuri vaihtelu) pelkästään kiristämällä välimuistien latensseja sille tasolle jolla ne piti olla jo Zenissä. Välimuistia (tai välimuisteja?) muuttamalla "+5-8%" ei olisi mikään ihme.

L2 on ydinkohtainen. Sen määrä kasvaa ytimien määrän mukana, ja sen "kokonaismäärän laskeminen" irrallaan ytimistä on hyvin merkityksetöntä ja harhaanjohtavaa.Yksi mitä teoriassa voivat tehdä on:

3600X

Välimuisti:

- L2: 3MB

- L3: 32MB

3900X

Välimuisti:

- L2: 6MB

- L3: 64MB

Eli kasvattaa alemmallakin tasolla nuo L2 ja L3 välimuistit nykyisin R9 tasolle. Siihen päälle vielä se huhuttu 200-300MHz lisää kelloja. Tosin suhtautuisin hieman varauksella tuohon koska se tarkoittaisi huippumalleissa jo ~5GHz maksimeita, minimeistähän noissa huhuissa ei puhuta mitään eli ne voivat pysyä samoina. Lisäksi AMD sai hieman parjausta kun alettiin mittailemaan ja testailemaan 3900X maksimeita + muisteltiin videota missä näytettiin +200MHz buustin päälle jorinoita mihin ei todellakaan päästä järkevillä jäähyillä.

Sopivampi paikka tälle keskustelulle on täällä: KonepaketitTarkoitus ois rakennella itselle uusi buildi vielä tän vuoden puolella. Koneella ei tehdä mitään tuottavaa tai muutoin järkevää hommaa mutta hyvät fps:t peleihin on toivottavia. Näyttö tulee jossain välissä myös vaihtumaan 1440P.

Mikähän ois sellanen hyvä peliryzeni jos kaveriksi tulee RTX 2080 Super? Omassa harkinnassa ollut 3800X ja cooleriksi noctua nh-d15.

Millaisista muisteista nämä ryzenit tykkää? Esim perus gskilli 16gt 3200MHz 16-18 latensseilla käypää tavaraa vielä? Vai hyötyykö pelikäytössä nopeimmista muisteita/pienemmistä latensseista?

... eli ei tule 6-kanavaista muistia.Gigabytelä kiusottelukuva tulevasta Aorus TRX40 -emolevystä.

- 8 DIMM-slottia